- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

使16位ADC提供19位分辨率的电路设计

录入:edatop.com 点击:

许多数据采集系统都要求高精度和快速采集数据,以便允许该系统能够检测小信号并且能将更多的传感器通道聚集在同一系统。传感器通道越多,系统的外形就能够越小,成本和功耗也越低。远程光通信和医用设备(例如,CT扫描仪)即得益于快速和高精度的数据采集系统。在光功率系统(例如,激光泵)中,需要不断监视其功率水平。在这种数据采集系统中,对于需要≥90dB动态范围的输入激光功率,其激光控制环路响应时间要求具有1MSPS的采样率。在CT扫描仪中,数据采集系统必须具有16 b到22 b的分辨率,以便处理通过各种人体组织的宽动态范围的X射线信号。该系统需要大量的光检测器(较多的数据采集通道)和高精度数据采集以提高图像分辨率。

以上两个例子说明了系统要求的是相对精度,而非绝对精度。尽管能够检测出10nW的功率变化相对于1μW的输入光功率很重要,但同样的10nW变化作为1.00001mW与1mW之差的绝对值则显得无足轻重。然而表征模数转换器(ADC)精度的技术指标--积分线性误差(INL)是一种绝对误差。为了获得最佳相对精度,本文提出一种创新的解决方案是在精密ADC前端使用可编程增益放大器(PGA)。AD7677 ADC的满量程线性误差为±15 ppm(在16 bit分辨率条件下为±1 LSB)。在此ADC前端的PGA达到稳定状态的建立时间必须足够快,以便与具有相同分辨率ADC的转换速度相匹配。另外,该PGA还必须具有尽可能低的噪声,因为它决定数据采集系统的信噪比(SNR)。为了解决这些问题,本设计中的放大器采用AD8021运算放大器,它具有满足设计要求的速度、精度和快速建立时间,并且其电压噪声谱密度仅为2 nV/√Hz。图1示出该PGA增益设置与其ADC精度的对应关系。当输入信号幅度很低时能使该系统达到19 b精度。

(See Fig 1 of original article)

图1 在16位 ADC前端使用一个PGA能将其精度提高到19 位

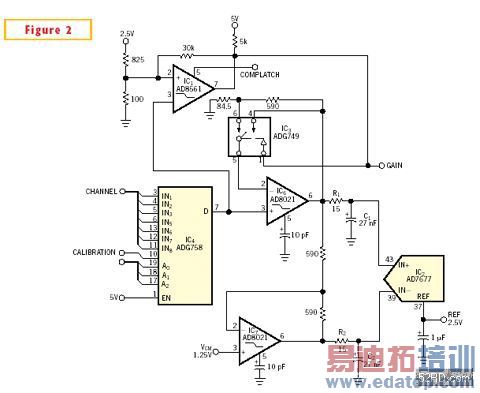

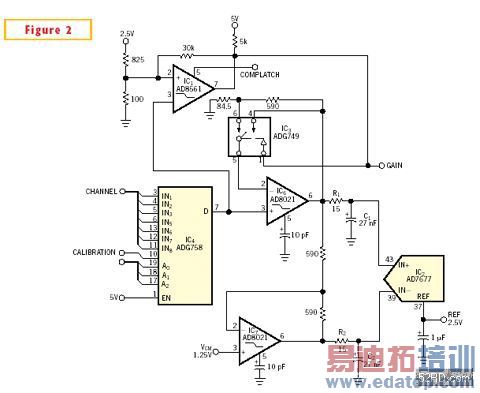

ADC的相对精度通常是指在满度范围被校准的情况下,任意数字量所对应的模拟量实际值与理论值之间的偏差最大值,用相对满度范围百万分比(ppm)表示(也可用百分比,或LSB表示),再加减(±)其系统测量过程引起的最小绝对误差所对应的ppm。图2所示的电路设计能达到107ppm±1.9ppm的相对精度。模拟多路复用器IC4含有多个带宽较小的通道以便利用ADC的1MSPS采样率。因为PGA对多路复用器表现为高输入阻抗,所以可级联多个多路复用器,从而增加通道数。多路复用器还具有一个校准输入端口,从而利用一个校准基准电压就可以简便地校准每次增益设置引起的失调电压和增益误差。校准仅需要在加电或工作条件(例如,温度)发生变化时进行。放大链路由多路复用器、比较器、前置放大器和ADC组成。AD7677具有逐次逼近型结构,它允许放大链路中的单独部分同时工作。当ADC对一个通道进行采样时,其比较器和放大器可以使随后的通道达到稳定。因此,该数据采集系统能以ADC的最大采样速率工作。

(See Fig 2 of original article)

图2 通过PGA与16 位ADC结合使系统提供19 位精度

在模拟多路复用器达到稳定之后,快速比较器IC1立刻完成适当的增益设置。比较器的阈值电压使信号被IC6 和IC7放大后不会饱和或嵌位。AD8561 比较器的响应时间为7 ns,它提供一个锁定信号,能够在放大器达到稳定期间和ADC捕获信号期间保持增益不变。通常的PGA配置要求用户在输入端施加信号之前预先设置放大器的增益。图2中的PGA具有"自动设置增益范围"的特点,它能够选择最适当的PGA增益以获得最高精度而不引起信号饱和或嵌位。比较器包含滞后电路,以便在信号接近某一个具体增益范围限制时减少设置的增益变化。该电路能自动将ADC的精度提高到19位,同时又能保持其1MSPS的全速采样速率。

IC6 使用1或8的增益设置对多路复用器的输出信号进行放大,如果需要提供最大可达到25的不同增益,可以改变反馈网络电阻。模拟开关IC3控制增益的设置。运算放大器AD8021的高增益带宽乘积能提供足够的带宽,因而其补偿电容对所有的增益保持相同。放大器IC7 为ADC产生差分输入信号。比较器和放大器的建立时间以及ADC的捕获时间都远小于ADC 的1μs的转换时间。ADC两个输入端的RC噪声滤波器R1/C1和R2/C2,它们占用额外时间。这些滤波器限制PGA的噪声带宽。当IC7 的增益为-1时,PGA是数据采集系统主要的噪声源。

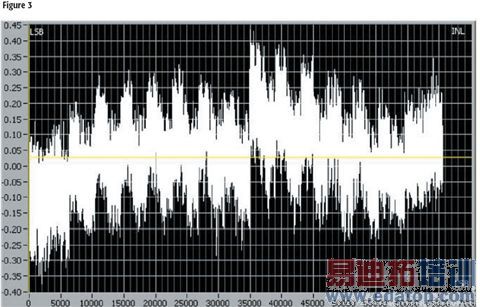

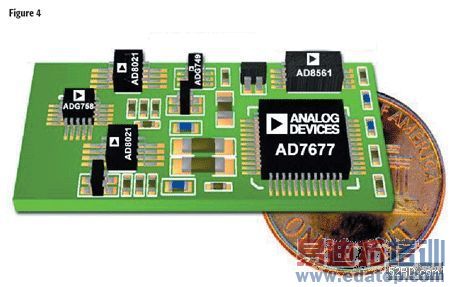

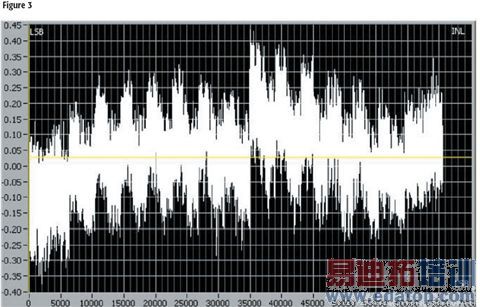

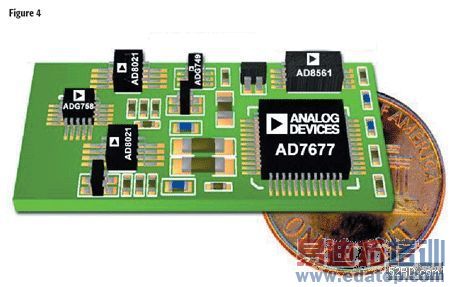

图3示出该电路设计的线性误差。在这种最高增益设置条件下达到如此低的线性误差(图中示出最大值为0.44 LSB,最小值为-0.37 LSB)并非易事。这相当于±0.9 ppm的典型误差。当增益为8时,输出噪声为85 μV rms。如果需要,可以利用软件平均进一步减少噪声。图4示出使用AD7677评估板构成的完整数据采集系统,印制电路板面积为15×30 mm。

See Fig 3 of original article)

图3 数据采集系统对于所有可能ADC数字量的线性误差

(See Fig 4 of original article)

图4 以1美分硬币为参照的完整数据采集系统的相对尺寸

以上两个例子说明了系统要求的是相对精度,而非绝对精度。尽管能够检测出10nW的功率变化相对于1μW的输入光功率很重要,但同样的10nW变化作为1.00001mW与1mW之差的绝对值则显得无足轻重。然而表征模数转换器(ADC)精度的技术指标--积分线性误差(INL)是一种绝对误差。为了获得最佳相对精度,本文提出一种创新的解决方案是在精密ADC前端使用可编程增益放大器(PGA)。AD7677 ADC的满量程线性误差为±15 ppm(在16 bit分辨率条件下为±1 LSB)。在此ADC前端的PGA达到稳定状态的建立时间必须足够快,以便与具有相同分辨率ADC的转换速度相匹配。另外,该PGA还必须具有尽可能低的噪声,因为它决定数据采集系统的信噪比(SNR)。为了解决这些问题,本设计中的放大器采用AD8021运算放大器,它具有满足设计要求的速度、精度和快速建立时间,并且其电压噪声谱密度仅为2 nV/√Hz。图1示出该PGA增益设置与其ADC精度的对应关系。当输入信号幅度很低时能使该系统达到19 b精度。

图1 在16位 ADC前端使用一个PGA能将其精度提高到19 位

ADC的相对精度通常是指在满度范围被校准的情况下,任意数字量所对应的模拟量实际值与理论值之间的偏差最大值,用相对满度范围百万分比(ppm)表示(也可用百分比,或LSB表示),再加减(±)其系统测量过程引起的最小绝对误差所对应的ppm。图2所示的电路设计能达到107ppm±1.9ppm的相对精度。模拟多路复用器IC4含有多个带宽较小的通道以便利用ADC的1MSPS采样率。因为PGA对多路复用器表现为高输入阻抗,所以可级联多个多路复用器,从而增加通道数。多路复用器还具有一个校准输入端口,从而利用一个校准基准电压就可以简便地校准每次增益设置引起的失调电压和增益误差。校准仅需要在加电或工作条件(例如,温度)发生变化时进行。放大链路由多路复用器、比较器、前置放大器和ADC组成。AD7677具有逐次逼近型结构,它允许放大链路中的单独部分同时工作。当ADC对一个通道进行采样时,其比较器和放大器可以使随后的通道达到稳定。因此,该数据采集系统能以ADC的最大采样速率工作。

图2 通过PGA与16 位ADC结合使系统提供19 位精度

在模拟多路复用器达到稳定之后,快速比较器IC1立刻完成适当的增益设置。比较器的阈值电压使信号被IC6 和IC7放大后不会饱和或嵌位。AD8561 比较器的响应时间为7 ns,它提供一个锁定信号,能够在放大器达到稳定期间和ADC捕获信号期间保持增益不变。通常的PGA配置要求用户在输入端施加信号之前预先设置放大器的增益。图2中的PGA具有"自动设置增益范围"的特点,它能够选择最适当的PGA增益以获得最高精度而不引起信号饱和或嵌位。比较器包含滞后电路,以便在信号接近某一个具体增益范围限制时减少设置的增益变化。该电路能自动将ADC的精度提高到19位,同时又能保持其1MSPS的全速采样速率。

IC6 使用1或8的增益设置对多路复用器的输出信号进行放大,如果需要提供最大可达到25的不同增益,可以改变反馈网络电阻。模拟开关IC3控制增益的设置。运算放大器AD8021的高增益带宽乘积能提供足够的带宽,因而其补偿电容对所有的增益保持相同。放大器IC7 为ADC产生差分输入信号。比较器和放大器的建立时间以及ADC的捕获时间都远小于ADC 的1μs的转换时间。ADC两个输入端的RC噪声滤波器R1/C1和R2/C2,它们占用额外时间。这些滤波器限制PGA的噪声带宽。当IC7 的增益为-1时,PGA是数据采集系统主要的噪声源。

图3示出该电路设计的线性误差。在这种最高增益设置条件下达到如此低的线性误差(图中示出最大值为0.44 LSB,最小值为-0.37 LSB)并非易事。这相当于±0.9 ppm的典型误差。当增益为8时,输出噪声为85 μV rms。如果需要,可以利用软件平均进一步减少噪声。图4示出使用AD7677评估板构成的完整数据采集系统,印制电路板面积为15×30 mm。

图3 数据采集系统对于所有可能ADC数字量的线性误差

图4 以1美分硬币为参照的完整数据采集系统的相对尺寸