- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Blackfin处理器的调试功能对成功设计的作用

软件工具

软件工具在系统开发过程中起到两个重要作用。第一,软件工具允许在订制的硬件

Blackfin 处理器VisualDSP++工具套件提供几项主要功能,允许软件开发商预测最终目标能够达到的性能。因为Blackfin处理器体系结构从根本上支持高效编译代码,因此大多数开发项目能够用C或C++完成。这项功能允许在项目开始的时候将现有的代码基快速整合到该项目中。这样就能利用很多设计结果而无需探究体系结构细节。

一旦初始项目建立起来,程序员有几种仿真选择,允许在周期精度和仿真速度之间灵活地折衷。VisualDSP++开发工具提供代码运行时间统计分析功能,作为其仿真器和模拟器的一部分。该工具允许程序员看到一个应用程序不同部分的运行时间是如何分配的,从而为优化工作提供方向。

即使Blackfin编译器的性能对于信号处理应用和MCU应用(低周期数和低字节数)都是杰出的,但是总是有一部分代码需要利用基于汇编语言的程序库进一步优化。虽然这种情况在大型开发项目中不常见,但是VisualDSP++仿真器提供了流水线查看器以便用图形方式识别失速(停止),从而进一步优化。由于Blackfin指令流水线是互锁的,因此失速不需要程序员手动跟踪和管理。即使如此,这种查看重要部分代码失速的能力通常允许程序员能够进行小调整从而实现对周期数的极大改进。

该仿真器的另外一个便捷功能是高速缓存查看器。由于始终存在系统设计工程师必须对片内和片外存储器大小进行折中的问题,所以对于预测如何根据指令流程完成高速缓存以及显示实际上如何访问数据,高速缓存查看器能起到非常重要的作用。(查看器语句示例如下)

<Translation of graphics>

VisualDSP++ Debug Tools Aid Code Optimization=VisualDSP++

调试工具辅助代码优化

Pipeline viewer finds stalls in critical sections of code=

流水线查看器发现关键部分代码失速

Cache viewer helps programmer understand cache efficiency (hits and misses)=

高速缓存查看器帮助程序员了解高速缓存效率(命中率和缺失率)

Code profiler shows where most time is spent during program execution=

代码运行时间分析器显示在程序执行期间何处耗时最多

硬件平台

一旦整个系统经过仿真,算法和大多数外设都可以利用低成本的EZ-KIT Lite评估平台操作。EZ-KIT评估平台为开发商提供一种评估Blackfin处理器的方法,该处理器适合多种应用,例如音频、视频和其它处理计算量很大的算法。例如,ADSP-BF533 EZ-KIT Lite评估平台包括视频和音频解码器和编码器,以及板上SDRAM(32Mb)和闪存(2Mb)存储器。另外,可设置的标志引脚能够连接到按钮和LED。

USB调试器接口允许利用简单的USB接口连接到评估板,如果直接访问VisualDSP++ PC主机上的工具套件,为了提高性能,JTAG在线仿真器能够很容易连接到评估板。

可提供的ADSP-BF533 EZ-KIT 评估平台的EZ-Exterder 子卡允许开发商能够连接多个高速数据转换器评估板(ADC、DAC和混合信号转换器),CMOS图像传感器评估板和一些TFT LCD显示器。它还能为电路配置提供试验板区域,并且几乎可以为Blackfin处理器的每一个引脚提供检测。

芯片内置功能

Blackfin处理器的体系结构为设计工程师提供了内置硬件调试的附加功能。这些功能包括性能监视器、周期计数器、监测单元和跟踪单元。

性能监视器

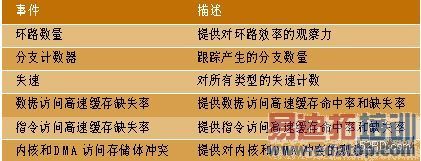

Blackfin处理器系列中的每一种处理器都有两个寄存器,它们能够通过编程对特定“中心性能”事件的发生次数进行计数。下表总结了能够跟踪的独立事件。

开发商可以利用性能监视事件来发现优化处理器的重点区域。通过性能监视器提供对芯片中实际发生事件的观察力,而不是通过仿真预测这些事件。

我们以数据访问高速缓存和指令访问高速缓存性能为例。性能监视器根据数据和指令访问高速缓存缺失率提供实际信息。知道了高速缓存缺失率,程序员能够利用VisualDSP++ Expert Linker开发工具交互地移动存储器中的数据和指令以实现最优性能。

性能监视器如何能帮助处理器的另外一个有效实例是当访问内部存储体时采用内核和DMA(直接存储器访问)引擎相互作用的方式。Blackfin处理器有一个集成的DMA控制器,它能够高效的移动数据无需与内核相互作用。内核安排数据传输,并且当数据缓冲器准备好处理时通知内核。处理器内核和DAM控制器能够在同一周期内访问不同的子存储体。当它们试图在同一周期内访问同一子存储体时,其中一种访问必须停止。在一个采用与多个DMA通道访问相并联的巨大的内核存储器访问的复杂系统流程中,知道什么时候DMA和(或)内核由于试图访问相同的子存储体而停止是非常重要的。性能监视器对这些事件计数以便开发商能够优化存储器中的数据分配。

周期计数器

Blackfin处理器体系结构还提供一个64 bit的周期计数器,用于对内核时钟周期计数。该周期计数器跟踪所有的执行周期,包括流水线活动,例如失速。它是用来确定一个给定算法的执行时间的极好工具。我们将周期数除以处理器内核的时钟速度,很容易将周期数转换成时间。Blackfin处理器的内核仿真器是周期精确的,所以从仿真器读取的周期数设计成与工作在内部1级存储器时从实际硬件测得的周期数相匹配。

监视单元

Blackfin处理器监视单元提供了另外一种调试灵活性。它监视指令总线和数据总线地址,在一个特定的地址或地址范围发生指定的次数之后产生一次异常。这是一种存储错误或优化代码的便捷方法,从而触发一次根据实际总线活动的事件。

监视单元提供的另外一个实际功能是补丁代码功能。这涉及到运行新代码替换现有代码的过程。监视单元可以配置成当到达旧代码的起始地址时产生一个异常,然后异常服务例程跳转到新代码所在的位置。

跟踪缓冲器

跟踪单元通过记录程序流中最后16次变化存储最近处理器活动的历史。另外,当跟踪缓冲器满的时候将产生一次异常,从而允许用户创建一个程序时序生成器活动从跟踪单元起始点开始的全部记录。该单元足够智能有选择地忽略与前一两次缓冲器入口匹配的流程变化,以便使一个密集的环路不会产生跟踪缓冲器溢出。

显然,对于像Blackfin处理器系列的嵌入式处理器,有许多供系统设计工程师使用的调试功能。通过利用这些软件和硬件工具,以及巧妙地使用实际的片内调试功能,设计工程师能够显著地缩短他们的产品开发周期并且促进对其系统内部工作过程的更好的理解。

上一篇:液晶显示器的自动调光技术

下一篇:通信系统设计中串行链路的优劣势探讨