- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

增进微型硬碟电池续航力与耐用度之设计

消费性电子产品对于省电功能的需求主要源自于持续成长的可携式产品,以及提高可靠度与降低故障率的要求。对于硬碟机(HDD)而言,一方面须增加储存容量,另一方面又得降低功耗以延长电池续航力并提昇产品的可靠度。本文就将针对这几个面向,提供硬碟机半导体解决方案的技术进行深入探讨。

随着内建高容量储存装置的可携式消费性电子(CE)产品愈来愈受欢迎,从手机、影音播放装置到数字相机,促使硬碟机产业必须开发各种独特解决方案以满足快速攀升的应用需求。如何使微型硬碟的成本更低、容量更大、电池续航力更佳以及可靠度更高,这些都是硬碟机研发业者致力发展的功能。为运用更弹性化的设计因应上述市场的需求,硬碟机制造商要求硅元件供应商提供理想的解决方案,支援架构方面的创新设计。

消费性电子产品对于省电功能的需求主要源自于持续成长的可携式产品,以及提高可靠度与降低故障率的要求。对于硬碟机(HDD)而言,一方面须增加笔记型电脑与掌上型消费性装置的储存容量,另一方面又得降低功耗以延长电池续航力并提昇产品的可靠度,但这两种需求通常无法兼顾。在运算领域,愈来愈多笔记型电脑被用来取代住家与办公室的桌上型电脑,因此需要更长的电池续航力、更高的传输速度以及更大的容量,以维持与桌上型机种相同的水准。在掌上型消费性电子方面,硬碟机必须具备更长的电池续航力以及坚固的设计,以因应意外掉落的风险。

针对省电性能量身设计

对于掌上型消费性电子装置而言,耗电率尤其重要。随着高频宽影音传输成为现今媒体播放装置与手机的必备功能,消费性产品制造商要求小型化(SFF)硬碟机(1.8吋以下机种)不仅可储存更多音乐,也须提供高速读/写功能,以支援影片播放与其他功能,这又对耗电率带来另一层压力。

可携式消费性电子装置持续扩展至更先进、储存更多资料的应用,而具有高普及率与高成长率的行动电话,正是各种功能集大成之平台。新款手机设计结合媒体播放功能与其他用途,却只分配约10%的耗电配额供储存功能所需;然而在不同电池技术中,装置的平均耗电率则须维持在100 mW的水准。

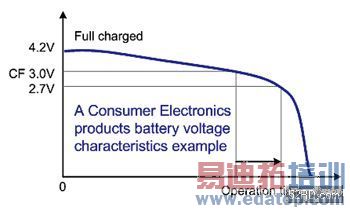

锂电池是现今掌上型装置最理想的电池技术。硬碟机的运作电压已降低到2.7伏特的最低值,使电池如(图一)所示,得以达到最长的播放时间。

(图一) 典型的锂电池

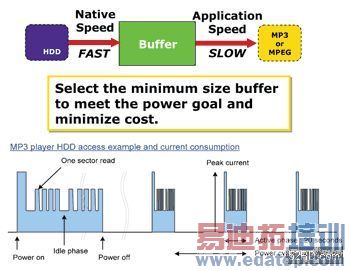

(图二)显示在传送串流音乐档案时,典型的电流週期图。一般而言,在没有传输资料时,主控端会将硬碟机设定为低耗电状态或关闭电源模式,而需要传输资料时,硬碟机才会开始运转,以高速传输率将大量资料送到主控端缓冲记忆体,并立即切换至低耗电模式。接着,主控端会以较低的传输率从缓冲区中读取资料。此举使得硬碟机能採用极低的工作週期,平均耗电率因此降低,进而延长电池续航力。但是当硬碟机在传送资料时,仍会採用各种电源管理技术来降低耗电量。例如,当读取磁区资料时耗电量会达到最高,但当主控端为忙碌状态时,硬碟机便切换至耗电率较低的模式。

(图二) MP3播放装置的电流消耗

缓冲区的功能是作为主控端的速度匹配元件。主控端缓冲区的容量会影响耗电量;缓冲区越大,表示高耗电硬碟机运转/停止程序越少,进而降低平均耗电量。在缓冲区容量、电源、以及成本之间取得最理想的平衡点,将协助主控端元件制造商选择适合的缓冲区元件,不仅能达到应用的功耗目标,且还能降低成本。典型的音乐播放装置缓冲区容量约在8至16MB之间,价格的压力促使硬碟机制造商致力于降低耗电率。

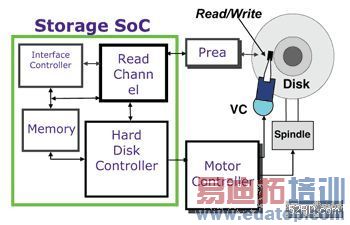

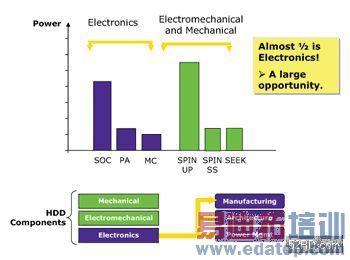

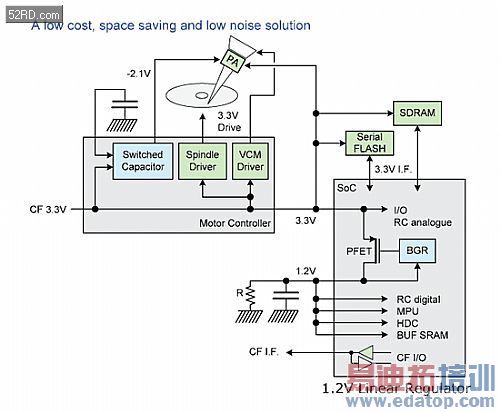

如(图三)所示,硬碟机电子元件包括一个前置放大器(PA)IC、马达控制器(MC)IC以及一个整合型系统单晶片(SoC),内建读取通道与硬碟机控制器技术,并整合所需的I/O元件与记忆体于其中。分析微型硬碟机的耗电预算(图四),显示储存电子元件佔去约一半的总耗电量,其余则是各种机械与电子零件(大多数是在主轴马达启动与关闭时所消耗)。由于SoC的主要功能是管理与读写储存在硬碟机磁盘上的资料,所以会消耗大部份的电力。这项耗电分析包含瞬间耗电,且会比典型的主控端应用的平均值要来得低。

(图三) 硬碟机电子元件

储存IC消耗约50%的硬碟机耗电量,因此硅元件供应商有绝佳机会来提升系统层面的省电效率。其中包括电压调整、磁碟分割、介面、耗电管理机制以及半导体制程技术等方面的创新设计。

(图四) 硬碟机耗电预算

■电压调整

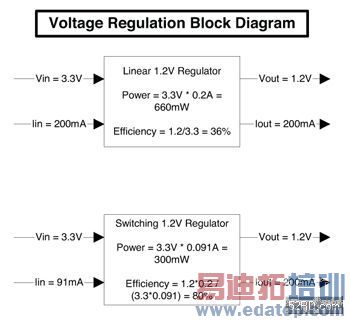

典型的硬碟机需要两种电压──供逻辑元件使用的数字核心电压,与供马达、模拟数字转换器(ADC)以及介面元件使用的模拟电压。模拟电压以往都是由主系统供应,并调整到最高值。核心电压以往都是透过硬碟机马达控制IC内的线性调整器,如(图五)所示,将主系统的电压调整至1.2伏特。现今的硬碟机使用3.3伏特的电力,线性调整器将3.3伏特转换成1.2伏特/200毫安培(mA)供储存IC使用。如(图六)所示,线性调整器耗用200毫安培的电流,转换效率仅有36%。

(图五) 传统线性调整器的设计

SFF硬碟机提升省电效率最有可能的方法,就是以交换式调整取代马达控制器的线性调整器,负责产生核心电压。这种元件亦能将3.3伏特转换成1.2伏特,仅耗用90毫安培的电流,转换效率高达80%。交换式调整器的噪音,可使用低成本的元件控制,以维持一定的信号完整性。利用交换式(300毫瓦)取代线性660毫瓦)调整器,可节省55%的总耗电量。此外,使用交换式调整器能把数位核心电压从1.2伏特降到1.0伏特,因此能节省更多的电力。

另一个改进方法就是降低电源电压、数字核心电压以及模拟电压。改採集积度更高的制程能进一步降低核心电压,带来惊人的省电效益。但降低的幅度会因漏电量的增加而减少,使得在65奈米制程技术环境中衍生出更多有待克服的问题,削弱了降低模拟电压原本可观的省电效益。藉由采用模拟电压则有机会带来省电效益。一般的主控端电压最高值为3.3伏特,但若採用混合信号电路,能将电压的额定值压低到2.5伏特。2.5伏特可透过降低主控端电压或是由硬碟机内建的调整器转换。若使用后者,由于调整器会损耗极微的效率(即使使用交换式调整),故降低耗电量的幅度是最低的。这种方法较适用于採用较低的主控端电压。

(图六) 电压调整区块图

■主控端/硬碟机分割

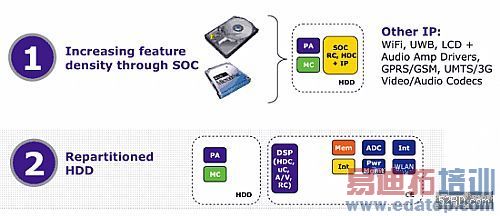

另一种节省电力的方法就是有效的硬碟机/主控端分割,也就是把功能从主控端转移到硬碟机,或是从硬碟机转移到主控端。现今各种多媒体功能纷纷被整合至媒体播放装置与手机等可携式产品中,透过磁碟的重新分割不仅能降低整体耗电量,亦能让空间有限的掌上型装置多出宝贵的可用空间。许多这类的装置都内含独立、可移动的元件,因此使用嵌入式硬碟机设计有助于节省耗电量、尺寸以及成本。(图七)提供这种整合策略的两个极端例子:

●将IP转移至硬碟机,例如像无线功能(WiFi/UWB)或影音编解码器。这种全功能的硬碟机能连结简单的显示器与键盘,开发出移动电话或MP3播放装置。

●消费性电子产品研发业者选择不将功能建置于硬碟机上,而是把硬碟机组件(HAD)以及基本的功能元件,连同其他应用元件一同整合到装置的主机板。

(图七) 重新分割主控端/硬碟机的功能

这两种设计各有优缺点,然而功能的整合的确能减少重复性以及多余的线路,并减少互连元件的数量,进而降低可携式装置的耗电率。

■介面

像CE-ATA 与MultiMedia Card(MMC)等新介面都正在发展专门支援消费性电子应用的规格。这些介面标准提供更小的尺寸以及使用相同的实体介面,但在通信协定不同之时,解决方案是採用较低的介面电压来降低耗电率。现今的Compact Flash介面使用3.3伏特的信号与驱动电压;CE-ATA/MMC介面规格使用1.8伏特的信号电压,并区隔模拟电源,藉以提高硬碟机的省电效率。

■功耗管理

功耗管理让主控端能有效地控制硬碟机的耗电量。储存单晶片通常内含一个多重状态的排序器,使系统能透过韧体控制以支援各种自主管理的耗电管理功能。这些功能可根据硬碟机的设定来调整耗电量,并可选择关闭电路、启动/关闭所有功能区块,以及针对无法关闭时脉的功能区块加以区隔。其他功耗管理技术包括选择正确的系统时脉频率,通常是选择适合的处理器时脉速度来提高硬碟机的效率,而这些功能都有助于提高整体省电效率。

■半导体制程

业者应根据硬碟机的传输速度来选择元件的制程技术。为在低耗电情况下,晶片研发业者应选择低漏电、高起始电压值(high threshold)的制程,能在待机模式下限制漏电情形,且仍能提供所需的系统效能。掌上型装置所使用的SFF硬碟机传输速度较低,因此使用较慢的元件可达到较低的耗电量。

此外,缩小制程的尺寸可降低产品的耗电量。降低的幅度大致呈线性比例,但因为65奈米所制造的元件中,漏电是一项相当显着的问题,因此在65奈米制程中耗电降低的幅度就开始缩小。

坚固耐用的设计

随着高容量装置在可携式消费性电子产品中日趋普及,硬碟机的动态保护机制也就相形重要。要提高这些装置的坚固性,必须能可靠地侦测出「坠落」的状况,并且必须在撞击之前将读写头归至停止位置。这是相当困难的目标,因为从一公尺坠落到地面所经过的时间不到半秒。

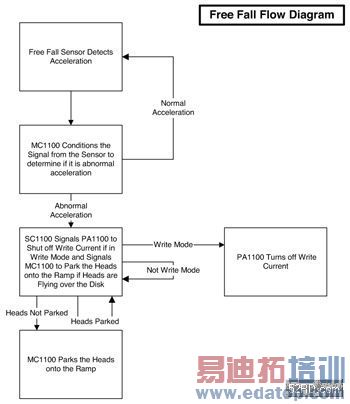

在半导体元件方面,小型化硬碟机须针对马达控制晶片、储存系统单晶片(或读取通道)、前置放大器以及用来侦测坠落事故的感测器,如(图八)所示,等元件的设计加以整合协调。现今的微型硬碟机採用两种感测器中的其中一种──撞击感测器或加速度计,并搭配相关演算法。

(图八) 硬碟机坠落时元件反应的流程图

在磁碟机坠落时,马达控制晶片会收到感测器传来的信号;而内建撞击感测器的硬碟机中,会把模拟信号放大后再转换成数字信号。马达控制器会将信号与参考值进行比对,研判信号是否「异常」。消费者不能容忍经常发生误报情况 ,例如在非必要时关闭硬碟机,或在真正发生坠落时却没有启动保护机制(在撞击地面之前没有保护硬碟机)因此系统会妥善处理信号,将读取的数据与参考值进行比对。若信号落在参考范围之外,马达控制器就会警告SoC硬碟机正在坠落。

SoC会先检查硬碟机的状态,判断其正处于搜寻作业或待机模式。有别于桌上型PC专用硬碟机,即使在没有进行读写的状态下,仍旧会把磁头置于旋转中磁盘的上方,对于微型硬碟机而言,电池电力的重要性远超过资料传输速度,因此在待机模式时会关闭主轴马达,并将Head Stack Assembly(HSA)磁头组件置于磁盘以外的区域。若硬碟机处在写入模式,SoC会透过前置放大IC关闭写入电流,并由马达控制器关闭主轴马达,并将HSA磁头组件停在待机区。

对SFF硬碟机而言,改进可靠度与管理电源损耗是同样重要的考量因素,因为像是拔下电池造成电力忽然中断等类似事件,与撞击一样经常会发生。这种事件与装置坠落的情况十分类似:马达控制器感测到电力中断后,会立即将HSA组件置于待机区。SoC在确认电源中断后,在正常控制的状态下立刻关闭硬碟机中其他电子元件。所有种类的硬碟机在执行这项程序时的模式都相当类似,较大的(2.5至3.5吋)硬碟机可利用主轴马达的反电动势提供足够的能源来收回磁头。SFF硬碟机中的小型磁盘则没有足够的旋转动能来产生必要的能源,因此必须利用电容,在硬碟机运转时对电容充电,在电力中断时就使用电容中的电力来收回磁头。

新型SFF硬碟机的设计愈来愈依赖晶片与韧体的通信效率,藉以缩短反应时间。在改进可靠度方面,元件的整合度是另一项重要的考量因素。由于消费性电子装置的可携性增加机械或电子故障的机率,而增加一个电容或电阻,则会使硬碟机故障的机率大幅提升,因此,新型硬碟机必须透过马达控制器来整合许多独立型元件,藉以改进可靠度与降低整体成本。

结语

现今许多小型化硬碟机採用最佳化的设计,能整合在各种须大量运用SSF的装置中,例如像手机与未来的多媒体掌上型装置。硬碟机制造商与硅元件供应商持续致力于发展出更高的容量、更长的电池续航力以及更坚固的机种;而他们的努力也造就了创新的产品,比如,于2006年问市的1.0吋硬碟机,其容量较前一年机种高出一倍以上,提供12至15GB的储存容量,增加的幅度是自1999年以来最大的一年。1.0吋硬碟机的空间密度已达到1.8吋机种的水准,有效扩展此机种的市场版图至包括像高阶笔记型电脑的市场。(作者为Agere Systems杰尔系统储存部门资深技术经理)