- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PLL提供最佳PC效能控制

在消费性个人电脑等高度竞争市场,如何创造差异化是关键。在晶片组、中央处理器及绘图控制晶片不同的选择,便能创造一台高效能个人电脑的差异化。但是,一个稍微不同的小选择却可能造成一个系统内运作产生差异且还不错,而且还能让电脑玩家享受系统内各项元件不同功能组合所带来的好处。

时脉架构已发展到能让使用者将系统最佳化以达到高效能,并能将选用的元件性能发挥到极致。许多PC用时脉晶片的设计并不是让使用者可以根据一些主要的元件如主处理器及绘图晶片等进行时脉频率微调。超频(Overclocking)主要是对如中央处理器等的关键零组件进行超过于一般时脉频率的调整,这已成为玩家和一些个人电脑制造商用来对其PC效能最佳化所使用的方法。

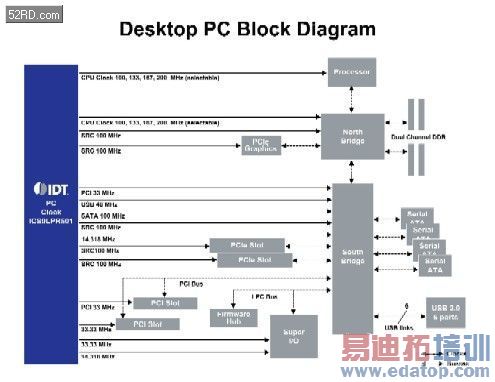

图一(请点小图看大图)

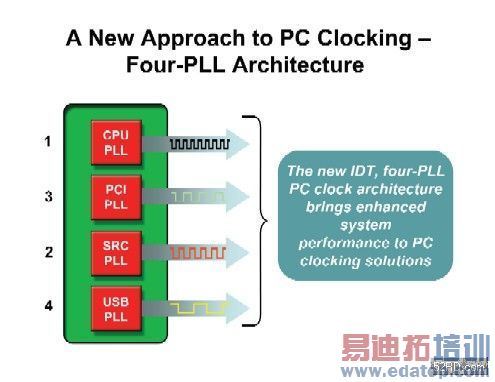

这群总是渴望高速系统快感的玩家们,是刺激桌上型个人电脑往高阶发展的主要动力。但是其中一个主要问题是,超频控制元件在市场上的取得性,而且此元件必须让玩家们在进行超频的同时不会影响其他关键零组件的性能。要实现此目标,就必须倚赖四相位闭锁迴路(PLL)的时脉产生器协助。

时脉分离运算之优势

过去,个人电脑对于时脉的需求相当简单。多数系统时脉是以原本即可以产生较高频率的基本33 MHz时脉设定,但通常都设定为33 MHz的整数倍数。这些时脉不只驱动中央处理器,还支援包括晶片组、前端匯流排和绘图晶片,以及一些速度较慢,配置于晶片组南桥的周边元件。另一主要时脉是来自于48 MHz时脉源。使用48 MHz时脉源的周边元件包括USB,通常需要一个48 MHz的基础时脉。还有个人电脑使用的super-I/O晶片,需要平均分用24 MHz时脉。因此,从前的个人电脑广泛採用二相位闭锁迴路(2-PLL)时脉产生器。

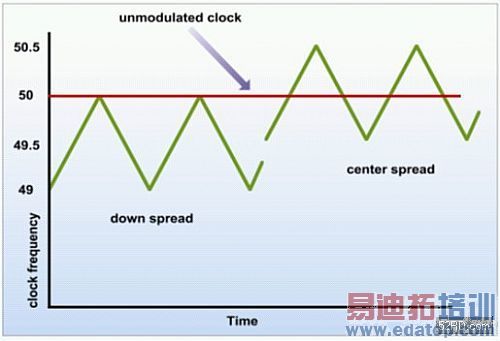

为减少主机板所产生的电磁干扰(EMI),制造商已採用诸如展频时脉的对策。此技术是对中央频率周围进行时脉的随机调变。如此便能在中央频率周围进行频率扩散,降低波峰,以符合各国或欧盟的法令限制。然而,只有某些时脉可以採用展频技术。虽然中央处理器、记忆子系统及绘图晶片能接受可展频的时脉,但是如USB的通信系统则无法接受。

图二

许多供应商是根据这些需求来设计时脉晶片,但这样的考量却容易忽略了对中央处理器及绘图晶片进行时脉源分离可获得的好处,这些元件也可以进行不同程度的超频。二相位闭锁迴路(2-PLL)的时脉产生器可提供系统中这两种元件相同的时脉,结果,绘图晶片的时脉频率必需降低,以便中央处理器能正常运作,反之亦然,这也就意谓着系统中的所有个别元件无法发挥其最大功能。

最近出现了三相位闭锁迴路(3-PLL)的设计,让绘图晶片及CPU的时脉得以个别运算。CPU及绘图控制器个别分开产生时脉,便增加了提高微调个别效能的可能性。然而,随着Serial ATA(SATA)硬碟机的问世,系统必需产生独立的100 MHz SATA时脉。虽然使用3-PLL时脉产生器时,此时脉可分享来自绘图晶片或CPU所使用的33 MHZ时脉源,但是Serial ATA无法进行超频,这意谓CPU和绘图晶片所需的时脉必需来自于同一个PLL,才能避免超频的程度个别受到控制。

4-PLL提高PC稳定度

若採用四相位闭锁迴路(4-PLL)这类新型PC时脉装置(例如IDT CV115C),即可让配有SATA硬碟机的系统上绘图晶片及CPU得以单独进行超频。此时脉能够线性比例扩展,让使用者免除要在极少又不够精确的频率设定中作勉强又不合适的选择,转而可进行调整至所要达到的效能,也毋须冒着可能造成系统无法开机或稳定执行的风险。

图三

藉着在两组33 MHz时脉输出上提供独立的展频选择,也可以让PC降低噪音和EMI,更有效的进行最佳化。即使整个系统不需要进行超频,此独立的展频时脉控制功能让PC制造商在设计系统时,能考虑到某些特定元件对展频时频率中的随机波动所产生的不同敏感度,让制造商在此方面进行功能调整以达到更高稳定度,进而大幅减少退货。

以4-PLL因应设计复杂化

当消费性个人电脑渐渐发展成为家庭媒体中心,兼具网路流览及游戏机功能时,便需要更多的时脉源。除了追求最佳效能的市场外,对具有弹性的时脉产生器的需求更多。利用四相位闭锁迴路(4-PLL)的设计所提供的控制能力,才能符合PC设计越来越复杂趋势下对时脉的需求。

由于即使如PC时脉晶片这类不太引人注意的产品,也必须因应需求持续变化,显示半导体开发制造商必须对终端应用有所瞭解,才能创造出符合现阶段及未来系统发展需求的产品。(作者为IDT副总裁暨PC时脉事业处总经理)

上一篇:提高汽车ECU的测试速度

下一篇:增进微型硬碟电池续航力与耐用度之设计