- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

第二代PCI Express测试技巧

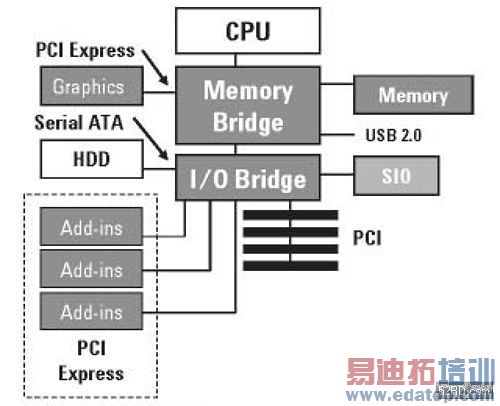

PCI Express (PCIe) 匯流排不再是所有资料都以固定速度传递的平行资料匯流排,而是序列、点对点、个别设定时脉的“波道”(lanes)组合,每个波道包含两对差动资料线路,一对上传资料,另一对下传资料。这些波道可以堆叠在一起,以提高I/O系统特定区域,如视讯卡插槽,的频宽(详见图1)。以第二代技术而言,每个波道在每个方向可达5 Gb/s的资料速率。这项技术有一些显而易见的优点,比如点对点电路可以大幅减少在主机板上绕递的轨迹数量。PCIe对桌上型PC市场所造成的最大冲击就在于PCIe x16绘图卡插槽,这项技术的实作取代了AGP 8x成为绘图卡制造商的首选平台。

图1:主机板结构

PCIe实体层规格

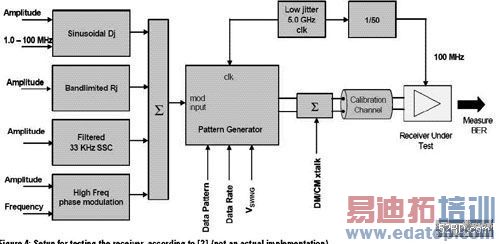

PCIe提升了资料传输效率与资料品质。它使用8b/10b编码,将时脉信号嵌入资料信号。波道数最多可达16个。第一代技术的资料速率是2.5 Gb/s [1],第二代的速度是第一代的两倍,并且增加了更多信号完整性需求 [2],以致对抖动测试产生新的要求。再者它是为了扩频时脉(SSC)而设计,能减少电磁干扰(EMI)的问题。从规格可以瞭解测试边限。PCIe晶片组包含发射器(TX)和接收器(RX),它们各自拥有标准 [1, 2] 所定义之不同实体参数。图2、3、4是第二代技术标准的复制 [2]。

■特性描述

TX资料流的速度为5 Gb/s,相当于200 ps的单位间隔(UI)。资料速率的差异在±300 ppm之间,但不包括SSC,它会以30 kHz的速率增加一个-0.5%的三角形调变。PCIe第二代规格定义了两个电压漂动位准:最大漂动与低漂动。最大漂动信令使用解强调(de-emphasis),低漂动则否。究竟发射器必须支援最大漂动、低漂动或同时支援此两种模式,主要取决于它的使用方式。通常低漂动适用于可接受较短通道的功率敏感(power sensitive)应用。规格中并未明确定义选择输出模式的方法,必须视实作而定。

■RX特性描述

PCIe实体系统的另一个部分是RX。同样地,它的资料速率也是5 Gb/s,亦即200 ps的UI,时序差异在± 300 ppm。TX定义了两种信令位准,但RX只有一个电压位准规格,这表示在RX指定的边限与TX的输出漂动无关,而且通道的特性必须与TX输出漂动匹配。通常低漂动输出所支援的通道,其损耗大约是最大漂动信令所支援通道的一半。

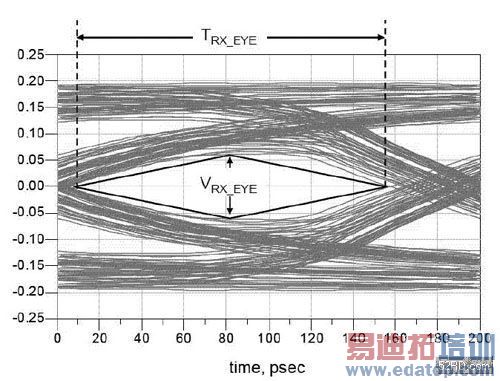

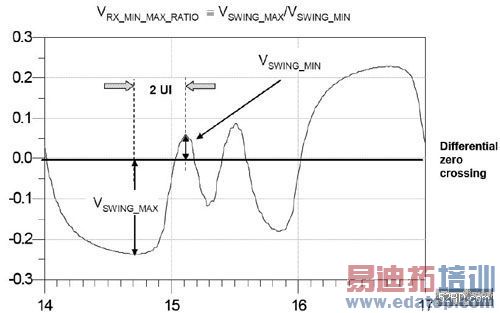

认证眼图测试(Compliance Eye Test)要求输入信号的差动振幅必须小至120 mV,而时间则必须接近0.4 UI(详见图2)。对接收器的动态电压范围来说,所需的输入电压必须提供Vswing_max /Vswing_min = 5的动态范围,及小至.6 UI的最小脉冲宽度(详见图3)。

图2:依据PCIe基本标准 [2],差动信号的接收器眼图边限。

图3:接收器的动态电压范围

RX与TX的振幅和时序规格的差异,在于两个晶片组间的媒体所允许的抖动概算。RX必须能够解读因通道符号间干扰(ISI)而造成振幅有明显差异的输入。在此以VRX-MAX-MIN-RATIO来表示,求出的值是5(详见图3),相当于传统FR4材料长达25英吋的传输线。此外,RX输入必须容忍高达150 mV的交流峰值共模输入电压。

第二代接收器的特性是,符合规格 [2] 所定义的一组最差输入条件之误码率(BER)。接收器的规格与易于实作的测试设定相容。直接在接收器的接脚量测是不可能的,因为这类量测同时包含了入射与反射信号成分。在量测参考负载时调整接收器参数,使其符合最差规格的边限,然后以待测接收器来取代负载,这个问题便能获得解决。只要两个步骤就能准确调整接收器的测试环境,并从最差的边际条件设定中将接收器的电子寄生去耦。

开发RX的规格边限时,在参考负载所测得的信号与接收器装置焊垫所需的信号间容许有信号衰减。设计RX硅晶片和封装的厂商必须留意封装-硅晶片的交互作用,以保证装置焊垫的信号位准能产生够好的BER。

图4:根据 [2] 所做的接收器测试设定(并非真正的实作)

PCIe测试的基本概念

PCIe总共包含三层:由下而上分别是“实体层”、“数据链路层”和“交易层”。每一层都必须透过适当的仪器来进行验证。以实体层而言,通常需要使用码型产生器和错误侦测器,配合示波器来检查正确的误码率(BER)和信号完整性。逻辑分析仪可用来验证数据链路层,也可执行编码除错。协定分析仪和模拟器则用来验证交易层。

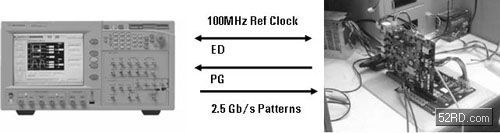

■PCIe实体层环境与测试设定

PCIe实体层有两种测试方法,第一种是主机板测试,另一种是内插卡测试(详见图5)。主机板测试着重于主机板上的北桥或南桥晶片组,必须使用像认证测试负载板(CLB)的解决方案来取得TX和RX信号。内插卡如Ethernet或绘图卡的测试,则必须使用认证测试基板(CBB)来取得TX和RX信号 [3]。CBB必须从一般的PC电源供应器获得电力,而主机板通常会提供100 MHz的参考时脉。以内插卡测试来说,必须从测试设定提供。

■PCIe BER测试原则

测试数位资料流的误码率(BER)时会用到下列基本程序。首先,码型产生器会将位元流传到DUT(待测装置)。错误侦测器会根据码型产生器送出的位元流,从内部产生一个称为期望资料(expected data)的位元流,但视DUT而定可能会所不同。DUT输出的位元流会返回错误侦测器。完成数字转换和取样后,错误侦测器中的决策电路便会即时且逐一位元的比较进入的位元流与期望资料间的差异。如果对应的位元不同,便被视为错误,而误码率就是进行比较的总位元数中的错误数量。此乃BER测试的基本原理,适合各种不同的应用,例如光收发器测试、数字IC晶片测试或数字通信系统测试。BER测试需要有已知、确定的週期性位元流通过DUT。为了能够对PCIe装置进行BER测试,标准定义了迴反模式。要让DUT进入迴反模式,必须透过训练序列(Training Sequences)TS1和TS2传送特定的符号。

图5:认证测试基板上的PCIe绘图卡

当PCIe Link开始从有效的附加程式执行时,训练序列便成为配置的一部分(详见图6)。在此设定中,PCIe装置会从“侦测状态”进入“轮询状态”,然后到“配置状态”,最后再藉由交换TS1和TS2,包括特定的链路资讯,而进入 "L0" 模式。为迫使DUT进入迴反模式,必须传送TS1和TS2资料流,并使用符号5的迴反位元。一旦进入迴反模式,大多数採有效的8b/10b编码之位元序列都可以使用。如此便可根据BER量测,来执行任何功能/参数验证或认证测试。

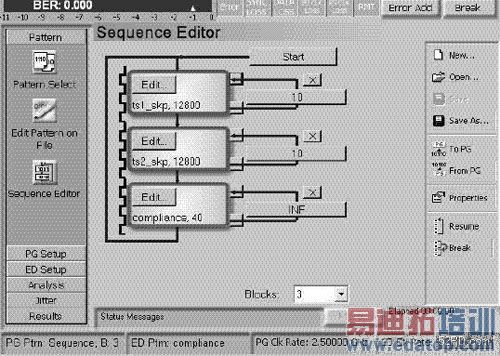

■建立正确的训练序列流程

如同稍早的描述,BER测试与个别的位元有关,而这里所需的Training Ordered Sets是以符号为基础,它是一个遵循下列规则的位元流:

• 8b/10b编码的运行不一致(Running Disparity)

• Skip Ordered Set

• Training Ordered Sets的正确重复

在BER测试仪器上,必须使用序列和区段编辑来设定。

■测试仪器

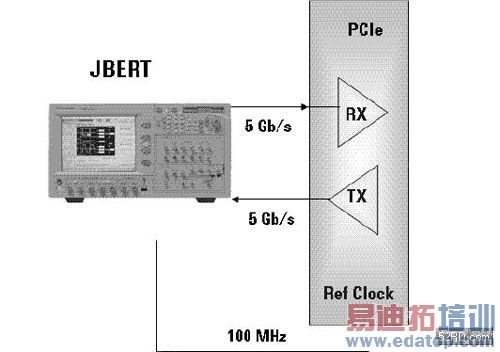

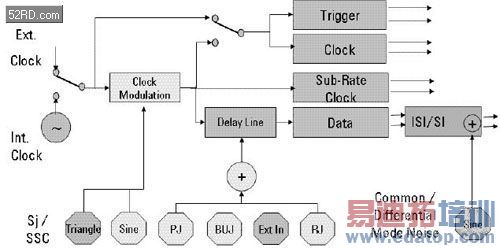

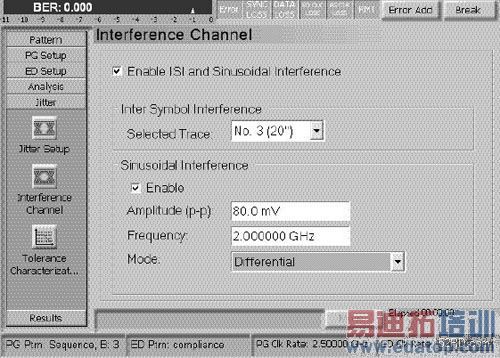

本文以安捷伦J-BERT N4903A高效能序列BERT(详见图6)所实作之PCIe实体层测试解决方案为例。有关抖动注入的能力,请看图8的描述。这台BER测试器(BERT)调变时序时脉的能力。透过该项能力,可以产生频率低于4 MHz的UI抖动,或产生一个扩频时脉(SSC)。至于较高的抖动频率(最高到1 GHz),则可在压控延迟线路上加入任何的外部信号。针对PCIe,可以混合正弦波信号(Pj)、随机噪音(Rj)和有界限的随机噪音(BUJ)来进行调变。最后再以符号间干扰(ISI)来调整资料信号,并于共模或差动模式下加入噪音。

图6:具备抖动容忍度测试能力之Agilent J-BERT N4903A高效能序列BERT

■建议配置

基本系统为J-BERT #C07或#C13。

#C07的执行速度高达7 Gb/s,#C13为12.5 Gb/s。

#J10可加入SJ、PJ、RJ & BUJ等抖动源。

#J11可加入SSC能力。

#J20加入含ISI和SI的干扰通道,可在资料输出中加入共模和差动噪音。

另一个建议选项是#A01,其可加入位元码回復模式(Bit Recovery Mode)。位元码回復是不必设定期望资料就能测试BER的方法,DUT的资料可当作参考。这项能力详细描述于 [4]。

图7:J-BERT与PCIe DUT的设定

图8:Agilent J-BERT N4903A高效能序列BERT的抖动能力结构

■J-BERT设定

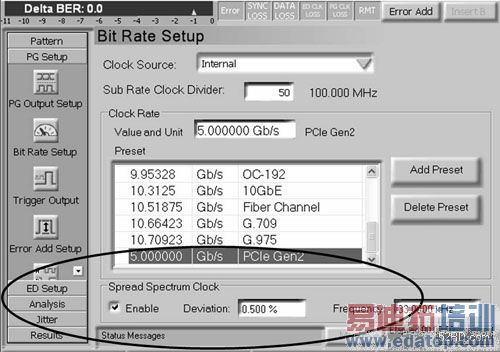

1. 频率

产生器和分析仪的资料速率设为5 GHz。

2. 参考时脉

Ref Clk连接到分割时脉输出;除法器设定为50以产生100 MHz时脉。

3. 传到接收器的信号:

资料输出会以差动方式连接到RX。执行功能测试,必须使用1 Vdiffpp。因差动振幅是单端振幅的两倍,所以DC位准为HIL = +0.25 V,LOL = -0.25 V,而终端电压Vt则为0 V。

4. 可以选择使用资料产生器的外部时脉或内建的时脉资料回復(CDR)来进行分析。使用CDR的优点是当测试抖动时,低频效应可由CDR追踪并从抖动数中去除。执行SSC测试时,建议在产生器提供的外部时脉执行分析仪,使测试系统与SSC时脉同相。

5. 图9的序列编辑器(Sequence Editor)将码型设定为迴反模式,其结合了迴路与自订的使用者码型。图中描述必要的TS1和TS2加上嵌入式SKIP符号的设定,SKIP符号经常被需要,它们是由TS1SKP和TS2SKP区段所提供。这么做可迫使PCIe装置进入迴反模式,一旦进入该模式,长达40个位元的COMPLIANCE码型便会产生无限的迴圈以利执行BER测试。

另外也必须指定认证测试码型(compliance pattern)给错误侦测器作为期望资料。序列编辑器会被设定 “Start on Command”,这可以从Sequence Editor Properties底下选择。

它的好处是BERT的内部时脉产生功能已经启动,而且产生器的次速率时脉会在按下START键之前执行。PCIe DUT需要参考时脉执行一段时间,好让内部PLL开始运作,并且在加入训练序列之前就执行。

■测试结果

下列测试结果是从连接到CBB(认证测试基板)的第一代PCIe绘图卡获得的。

RX/TX功能测试:

执行功能测试时,序列编排器(sequencer)必须启动,而错误侦测器会执行 “Auto Align”。结果请看图10,当中出现眼开,且BER读值为0。

图9:使用序列编辑器来产生训练,以便执行BER测试。

图10:取样点设定

TX输出量测

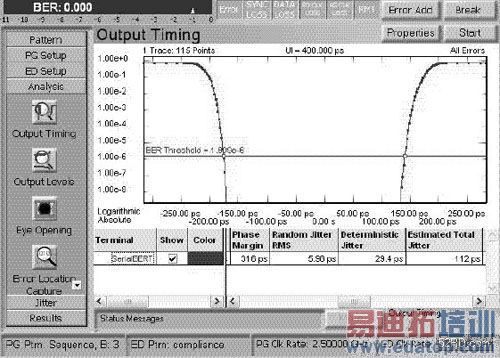

■TX输出抖动

TX时序效能可透过图11的输出时序量测得知。它提供抖动量测,包括RJ/DJ分离。除了在真正的BER临界点所取得的相位边限读值外,还利用外推法求出BER临界点在1e-12时的总抖动(Tj)。得出的外推值为112 ps。

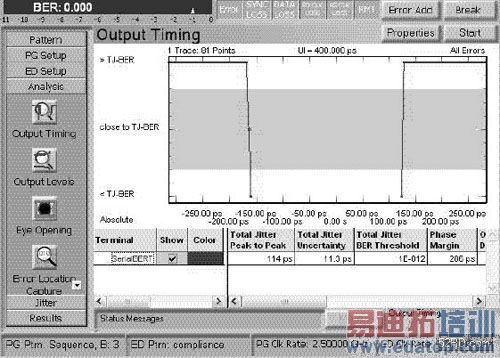

小至1e-12的真实量测,可由图12的快速总抖动量测提供,这项工具能量测真实的BER。在此例中,量测值是114 ps,非常接近外推值。因此,花许多时间来执行完整的量测只要一次就够了,当参数改变时不必再次执行。

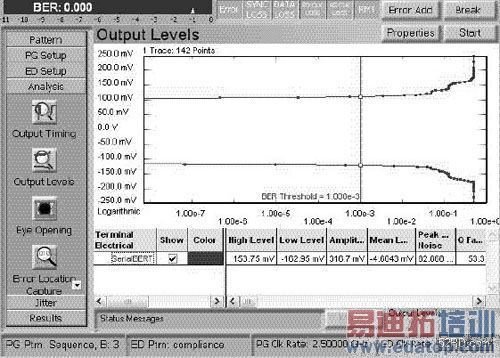

■TX输出位准

图13的输出位准量测,可提供差动输出信号的位准和振幅资讯。这项量测直接提供差动位准和振幅为BER函数的读值,另外还列出位准和振幅杂讯的读值,而且因为这项量测也可用于光学输出,所以会一併计算出Q系数值。

图11:输出时序量测

图12:快速总抖动量测

图13:输出位准量测

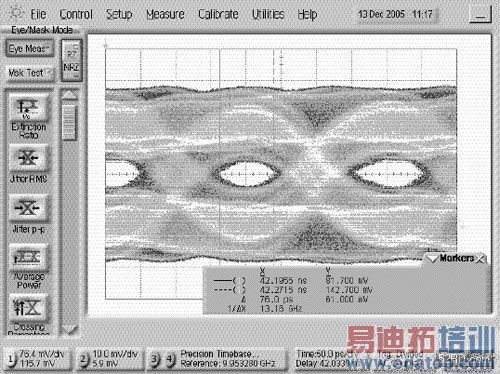

■TX输出眼图

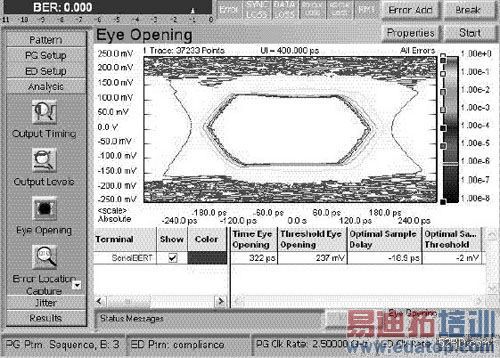

眼开量测提供差动信号在时序和电压的眼图结构,如图14所示。

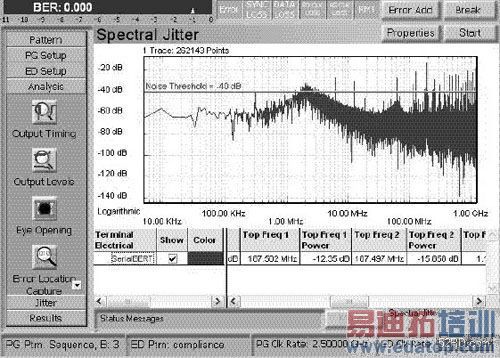

■TX抖动频谱

图15的频谱解析是一个很实用的除错工具,藉此可以瞭解抖动的频谱成分,及确认抖动的来源和根本原因。我们从该项量测中观察到:

• 在大约2 MHz的地方有一个峰值,此为相位杂讯,极可能是在时脉产生与分配时形成。

• 认证测试码型每40个位元重复一次,所以最低码型频率为67.5 MHz。所有介于67.5 MHz和最大速度间的峰值都源自资料相依抖动。

• 在5和10 MHz之间还有两个峰值,极可能是串音所造成。

图14:执行二维BERT扫描所得到的眼图

图15:抖动频谱解析

接收器RX输入量测

为检查RX输入的参数特性,我们必须建立:

• 接收器认证测试眼图 – 最坏情况

• 接收器动态电压范围的波形

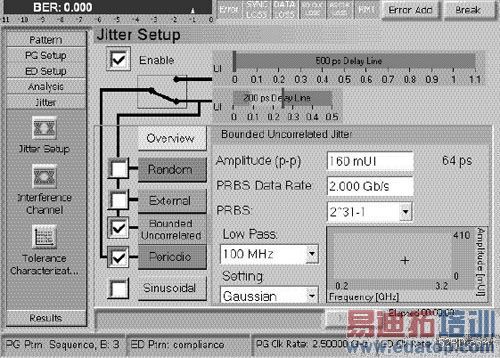

按标准制定组织的说法,J-BERT是“接收器测试电路”,而86100C Infiniium DCA-J则是内建显示器的“测试负载”。包含抖动选项的J-BERT内建了规格(如图4所示)所要求的所有抖动源(如图8所示)。

加入杂讯以建立接收器认证测试眼图(Receiver Compliance Eye)共模。资料信号必须以有界限的非相关抖动(BUJ)和正弦抖动(Sj/Pj)来调变,以产生小到.6 UI的眼闭(eye closure),其相当于.4 UI的最小眼开。

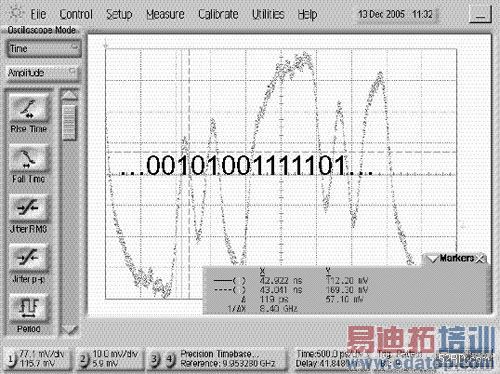

为加入共模噪音,必须以ISI/SI附加程式馈入资料信号,此时应启动最短的ISI路径。这么做可过滤较陡的边缘,使其具备正弦特性。首先加入频率为2.5 GHz的150 mV共模噪音及.16 UI的有界线非相关抖动(BUJ)。接着加入週期性抖动(PJ),这时眼闭为.6 UI。最后,调整产生器的振幅,使差动振幅的垂直眼开达120 mV,如图16所示。单端信号的振幅是60 mV。图17是混合各种抖动的设定。

图16:示波器画面(单端)– 加入150 mV共模杂讯的BUJ/PJ调变波形

图17:为产生认证测试眼图所做的J-BERT抖动设定

图18:示波器画面(单端)– 加入差动模式噪音的ISI调变波形

为产生接收器动态电压范围的波形,必须同时使用ISI滤波器和差动模式噪音。关于码型,理想上应使用Comma Symbol位元来执行;在5个连续的相同位元后面接一个0/1。适当的ISI滤波器应针对Vswing_min /Vswing_max提供1/5的振幅比,这可利用可程控滤波器的轨迹3来达到。接着加入差动模式噪音,在.6 UI的脉冲宽度下调整单一位元的最小脉冲宽度。最后再调整码型产生器的振幅,使单一位元达到120mV的垂直眼开。图18是结果产生的单端信号。

图19是ISI滤波器和差动噪音的设定。

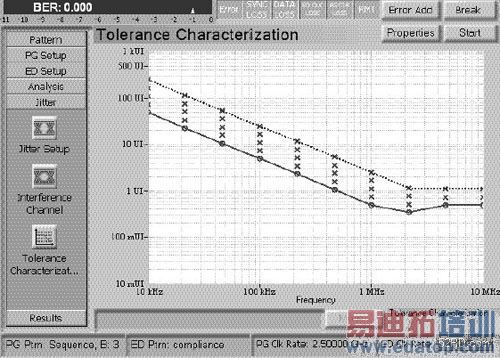

执行RX特性描述时,只要找出在迴反点取得的信号之BER数字就够了。如果是规格符合度测试(Conformance Testing),最好载入包含依认证测试需求而调整的信号之RX输入,并且依认证测试需求来检查TX输出。0.7版的PCIe 2.0标准 [2] 并未提到太多的抖动容忍度需求,但预计下一代速度更快的技术,会需要依据抖动容忍度曲线的运作。在测试上必须从低频时的多个UI到高频时的UI的各个部分,进行抖动频率和幅度扫描。

至少对特性描述而言这是必要的测试。J-BERT提供一个自动化软体工具,可在多个UI下扫描低频SJ到高频PJ,以记录抖动容忍度特性。图20是从Gen1装置撷取到的萤幕画面。配备#J10和#J20的J-BERT可用来执行以上所有的量测。

图20:抖动容忍度的特性描述

扩频时脉

PCIe标准指定资料速率可以不超过30 kHz - 33 kHz范围的调变速率,从公称资料速率频率的+0%调变到-0.5%,调变信号呈三角形。为维持± 300 ppm的频率需求,必须调变两个通讯埠,使它们的总差异永远不超出600 ppm。对大多数的实作而言,会要求当以SSC来调变资料时,两个埠应使用相同的位元速率时脉源。

FM调变是对称的,因此建议在信号产生器中使用的设定为4.9875 GHz,调变偏差为±.25%,即12.5 MHz。J-BERT产生器会在SSC启动时,自动执行偏移位移。产生器的程式设定频率仍然是5 Gb/s。图21说明在产生器时序页面上启动SSC的情形。为产生SSC,J-BERT必须配备#J10和#J11。在时脉和次速率时脉输出中也会出现SSC调变。

错误侦测器在外部时脉模式下会自动侦测适当的频率作为中间频率。当使用CDR模式时,使用者必须将参考频率设定为4.9875 Gb/s的中间频率。

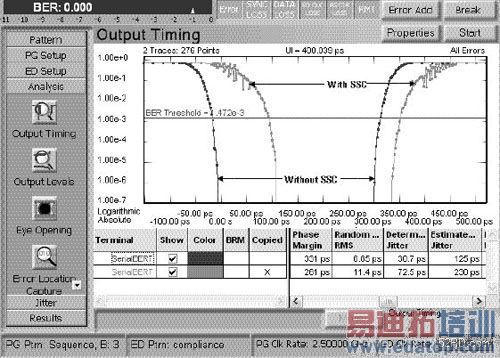

图22比较使用及不使用SSC时PCIe 1.0装置的眼开,从结果可以看出SSC会影响装置的眼开。复制的波形(恆为右边的轨迹)代表启动SSC时的量测。

图21:启动J-BERT产生器上的SSC时脉

图22:在使用或不使用SSC时的输出时序量测

结语

PCIe实体层测试解决方案对晶片组设计人员来说非常重要,而BER测试也随着资料速率的提高而变得愈来愈重要。对第二代PCIe,以及未来的SATA II/III和高速完全缓冲DIMM(AMB晶片)测试而言确实是如此。安捷伦以J-BERT N4903A高效能序列BERT,提供一个解决实体层量测需求的强大解决方案。

上一篇:解析伺服系统之新记忆体架构──FB-DIMM

下一篇:USB可变电源的制作