- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

解析伺服系统之新记忆体架构──FB-DIMM

2006年5月4日,JEDEC正式发布最终敲定的FB-DIMM规格标准,FB-DIMM是由Intel提出的一项新存储器架构,用意在于提升伺服器及高阶工作站的存储器效能,同时也扩增存储器的容量潜能。FB-DIMM(Full Buffered Dual In Line Memory Module,有时也写成FBDIMM)与现有的存储器架构相较到底有何承袭与革新?本文以下将对此更深入解析。

(图一) FB-DIMM依然使用今日主流的DDR2 SDRAM存储器颗粒

传统架构的效能、容量皆已受限

长久以来存储器一直倚赖两种手法来提升效能,一是加宽资料传输的并行度,另一是加快资料传输的时脉速度,不断加宽的结果是存储器模组(DIMM)的接脚数愈来愈多,从过去的FPM/EDO RAM 72pin、SDR SDRAM 168pin、DDR SDRAM 184pin,到今日DDR2 SDRAM的240pin,然而主机板的电路布局面积有限,难以再用拓宽线路数的方式来提升效能,虽然可以用增加电路板层数的方式来因应,但成本也会大增。

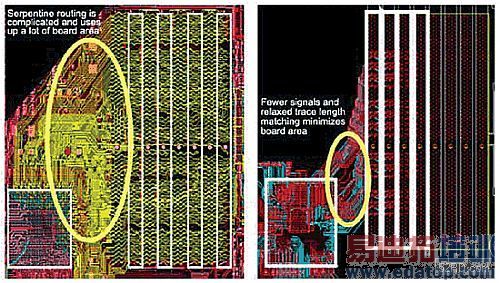

更具体而言,今日一个存储器通道(Channel)的宽度为64bit,在并行线路数的限制下,一般的运算系统多只能有两个通道,即是128bit,难以再更宽,更宽多半要付出极高的代价,同时线路数愈多也就愈难掌控并行传输的时序准确性,使得实际布线设计变的困难,过往就经常要用蛇绕方式的布线来求取并列时序的同步[1]。

另一个问题是时脉,透过并列同步频率的提升以达成加速的目标会带来副作用,即是愈高速愈会使传输线路的长度受限,这同样会造成电路布线设计时的难度,连带的也会使每通道的连接模组数受到约束,过去一个通道允许连接四条模组,之后降成两条模组,若方式不变未来一个通道仅能连接一个模组,这并非不可能,看看ATA硬碟介面,更高速的SATA仅允许一个通道连接一个ATA装置(硬碟),而过去较慢速的PATA则仍允许一个通道连接两个ATA装置。

即便模组数可以增加,然现有存储器架构的连接拓朴(Topology)属Stub-bus作法,即是同一时间、同一通道内只能有一个DIMM进行传输,其余的DIMM都必须闲置等候,如此传输效率依然卡在通道数、资料宽度的环节,难以改变。

通道数受限、模组数受限,自然存储器的扩充容量也会受限,倘若情形不改变,就只能倚赖存储器颗粒(晶片)的容量密度提升,然这就得倚赖半导体制程技术的精进才行(如从90nm进步至65nm)。很明显的,传统存储器架构已至多方窘困:效能、容量、线路数、时脉速、通道数、模组数、同步设计难度、电路面积成本等。

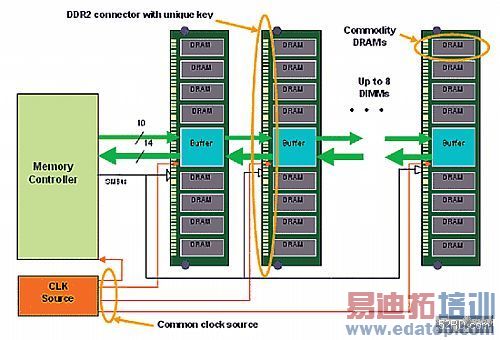

(图二) FB-DIMM主要是在既有的DIMM模组上加装一颗转化功用的AMB晶片

FB-DIMM的沿袭与变革

接着来看FB-DIMM的作法,FB-DIMM其实只改变存储器的连接架构与传输方式,在存储器颗粒方面仍是用今日常见的DDR2 SDRAM,但是在每个DIMM模组上追加一颗先进存储器缓冲(Advanced Memory Buffer;AMB)晶片,所有在DIMM上头的DDR2 SDRAM颗粒都与AMB晶片相连,再由AMB晶片与主机板相连,不再是过去让每颗DDR2 SDRAM颗粒自行与主机板相连,简单说即是一律透过AMB来转换、转接。

至于如何转换转接呢?AMB将原有DDR2 DIMM的64bit并列资料传输转换成24bit的串列传输,过去64bit并列传输是使用统一的传输时脉,且64bit在单一时间内只能在读取「或」写入,不能让读取与写入同时发生,而AMB转换后变成14bit读取与10bit写入,且在串列传输中夹带时脉信号(类似PCIe的8b10b法),各bit的传输时序不用整齐一致(即指同步),没有过去并列传输常要担忧的串音干扰,并允许各bit尽其所能的加快传输。

此外,DDR2 SDRAM使用的单端式(Single End)传输,逻辑定义来自绝对性的电压准位,如LVTTL、SSTL、HSTL等,难以长距离传输,如今AMB将单端传输转换成差动式(Differential)传输,以一对传输线路间的相对电压差作为逻辑定义,因此可长距、高速传输,也因此FB-DIMM的每通道可串接八个DIMM,不似现有传统架构仅能两个DIMM。

从64bit同步并列改成24bit非同步串列后,FB-DIMM的线路数也获得大幅缩减,过去要用240pin与存储器控制器(即北桥晶片)相连,如今只需用69pin相连,如此布线设计更容易(线路减少,不用时序同步),电路面积、层数等制造成本也可缩减。

进一步地说,每个FB-DIMM上的AMB晶片会相互串接,且如前所述可在单一通道内串接八条DIMM,即是串接八颗AMB,八颗AMB相互间以点对点(Point-to-Point)的方式连接,因此两点间可高速交换传递资讯,逐颗串接后会形成一个链(Chain)状连接,每个通道中只有第一颗AMB晶片会与存储器控制器连接,其余都是相互串接,串接的结果变成每颗AMB(DIMM)随时都可以传输,不似传统Stub-bus架构同时间只能有一条DIMM传输,明显的FB-DIMM/AMB作法较不易产生传输瓶颈,进而增加整体传输率。附带一提的是,串接的部分包含14pin的读取与10pin的写入,每个bit用一对差动线路构成,在专业用语上称为传输巷(Lane),而14pin的串接称为北面(Northbound),10bit写入称为南面(Southbound)。

此外,为何要称为Full Buffered,因为过去SDR SDRAM时代就用过Buffer技术,但只用在位址线路与控制线路,未用在资料线路,属于部分性的Buffer运用,运用Buffer缓冲可提升信号的发散(Fan Out;扇出)驱动力,这在过去单一DIMM上的颗粒过多时必须使用。如今FB-DIMM则是各颗粒的所有运作信号都要进行Buffered,所以称为Full Buffered。

之后,由于并列宽度与速度都提升,Buffer没有并列传输的同步机制,容易使传输失误,所以改成有同步机制的Registered作法,即是今日所称的Registered SDRAM,然预计Full Buffered作法将在二、三年内取代Registered。至于为何不在DIMM上也用Registered?因为各bit的传输已内含自用的时脉(称为Self-Clocking),各bit不用时序同步,所以不需要。

而AMB的转换也将侦错、更错机制进行改变,由过去的ECC(Error Correcting Code)换成CRC(Cyclical Redundancy Check),使侦错、更错能力获得提升。

(图三) FB-DIMM的架构可连接六个Channel

计算FB-DIMM的提升效益

改采FB-DIMM架构后真的可以加速与容量拓增吗?对此一样以机制原理来解释。

以现有DDR2 800而言,使用200MHz时脉可得到800Mbps传输率,乘以64bit可得51.2Gbps,除以8则成6.4GB/Sec。

同样的时脉频率用于FB-DIMM,则每个bit能有4.8Gbps,乘以24bit可得115.2Gbps,除以8为14.4GB/Sec,如此在同样的单一通道、同样的传输时脉下,FB-DIMM的14.4GB/Sec远胜传统的6.4GB/Sec。而且如前所述,FB-DIMM仅有69pin与存储器控制器相连,远少于现今的240pin,这意味着:取消一个传统通道的设置,可以改设置三个FB-DIMM通道,且使用线路、占用面积依然少于传统通道(69pinx3<240pin),串接方式也比Stub-bus更省电路面积。如此,原本可以设置两个传统通道的电路板,可以改设置成六个FB-DIMM通道,六个通道同时启用,则最高传输率可达86.4GB/Sec。

不过,86.4GB/Sec只是理想值,重点依旧在存储器颗粒上,FB-DIMM仍是使用DDR2颗粒,DDR2颗粒并行传输若只能达6.4GB/Sec,那么六个通道同时启用也只能获得38.4GB/Sec,此一瓶颈与硬碟的内外部传输率相类似,FB-DIMM的极致传输值如同硬碟外部的介面传输率,DDR2颗粒的传输率如同硬碟内部的磁头感应速率,真正的整体效能取决于内部、外部居次,外部更快速只是预留频宽,以待日后内部传输率提升时仍可因应,使外部不至成为整体传输的碍阻。

如此,FB-DIMM将DIMM数从二增至八,Channel数从二增至六,使FB-DIMM架构的最高DIMM数达四十八条,相对的传统架构仅四条,差异为二十四倍[2]。

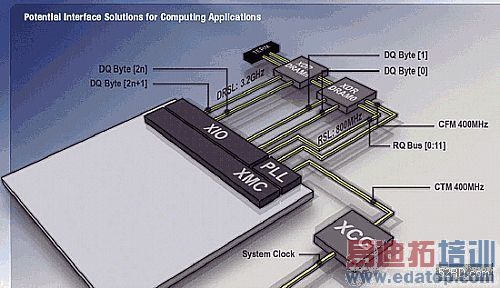

(图四) FB-DIMM运作原理

更多的益处

FB-DIMM除了能提升传输、拓增容量,其实还带来更多传统架构时所较难实现的好处:

●由AMB晶片统管各存储器颗粒,反而能消弥以往传统架构所常出现的DRAM颗粒相容性问题,因为此一电气特性差异已由AMB转化吸收,只要通道内的每条DIMM都使用同一业者的同一型款AMB晶片,颗粒相容性问题就容易排除,其他如负载效应平衡、阻抗匹配问题也都容易解决。

●更容易实现伺服器系统所需要的存储器坚稳机制,例如由AMB负责管控,若某颗DRAM颗粒暂时或永久失效,则可由其他备援颗粒来暂顶或取代。此外,也因为相同线路数下可比过去多设置1、2个通道,因此要实现如Chipkill之类的记忆体镜射阵列(Memory RAID)防护也更容易。类似的情况,当某一传输巷(Lane、bit)失效或故障时,因为各bit毫无相依关连,也可即时由其他传输巷来替顶。

●要在串列传输中增加特色功效机制也比并列方式容易,例如改用更先进的侦错、除错编码法,或添入传输加密等,这些追加只需稍减损原有的传输频宽即可达成,相对的并列传输得拓增更多的相关线路才能办到,在硬体工程上有较高的变更成本。

●过去伺服器管理者经常碍于单一系统内可用的DIMM数过少,迫使采购初期就得用单条高容量的DIMM,但也必须接受较贵的单价,否则没有足够的DIMM数可供扩充,而改採FB-DIMM后则可抒解此一问题,因为一通道内最多可有八个DIMM,使存储器的容量组态弹性、最高扩充容量都获得改善。

●此一特点其实也源自第一项特点,透过AMB的转化,日后即便DRAM颗粒改朝换代也可持续相容,现在使用DDR2 SDRAM,日后也可升级使用新一代的DDR3 SDRAM,或其他类型的DRAM。

(图五) 图左为一个DDR2 Registered DIMM通道的布线图,图右则为二个FB-DIMM通道的布线图

FB-DIMM也有隐忧、威胁

乍听之下FB-DIMM的一切表现都超越传统,然事实真如此吗?事实上FB-DIMM也有其隐忧,以下也逐一讨论:

●高速的AMB晶片功耗相当高,就一般而言,过去的DDR DIMM约5.4W,DDR2 DIMM因颗粒制程的进步而降至约4.4W,然使用DDR2颗粒的FB-DIMM却增至10.4W(因为加了AMB晶片),这在讲究营运成本精省的今天是一大致命伤,同时更高的功耗也使散热更困难,多条密排的DIMM将不易设计散热,如此不易运用在刀锋伺服器或超薄伺服器等散热空间有限的系统上,例如Sun在评估过FB-DIMM后就透露出可能放弃在薄型或省电型的伺服器中使用。

●在DIMM上追加AMB晶片也使DIMM模组上的电路复杂度增加,这对DIMM模组的制造商而言也有些挑战要克服。

●老实说FB-DIMM的原理与Rambus的RDRAM相近,主要差别只在FB-DIMM是以相容现有DRAM颗粒的方式来实现,以此规避技术专利,但就成本与简化性而言,反而是RDRAM较有利。

●Rambus已在推行比RDRAM更先进的XDR RAM及XDR2 RAM,XDR RAM是RDRAM的进化,将位址线、控制线分立出来,如此传输的延迟性(Latency)可低于RDRAM,且将用在Sony的新一代电视游乐器:PlayStation 3(PS3)上,FB-DIMM面对RDRAM已居弱位,如今就更难面对XDR RAM,唯FB-DIMM是JEDEC国际标准,此点胜过RDRAM、XDR RAM的独家业者授权。

(图六) XDR RAM技术示意图

支持业者与展望未来

最后,除了Intel发起外,Dell、HP等系统大厂都已表态支持FB-DIMM,DIMM模组业者如A-DATA、Apacer、Crucial、Kingston、SMART Modular Technologies也都支持,存储器颗粒业者也是全面投入AMB的研发及量产,如Samsung、Micron、Hynix、NEC/Elpida、Infineon等,就连IDT也投入AMB晶片的战局,同时各大厂也将持续提升FB-DIMM的传输率,预计将既有每Lane的4.8Gbps提升至6.4Gbps,甚至上看9.6Gbps。

上一篇:电源转换器的电磁相容性

下一篇:第二代PCI Express测试技巧