- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用微处理器与软体 完成数位电视H.264编解码设计

面对高解析视频的需求,大型家电业者以及半导体业者,都陆续地竞相开发能够进行HDTV影像即时编解码的晶片,以目前来说,针对HDTV影像即时编解码的技术上,大多使用「MPEG-4 AVC/H.264」编解码方式,从2007年开始,相信系统开发业者都能够轻松的取得丰富多彩的H.264编解码晶片。

以资料量来看,H.264编解码所需的运算量是MPEG-2的6∼10倍。因此在过去,能够进行H.264编解码的晶片,在数量以及多样化上是极其有限的,而正式展开使用H.264编解码晶片是从2004年,包括PSP、iPod等可携式产品开始采用。以此为应用开端,使得在解析能力上能够让QVGA(320×240画素)面板,达到SDTV(最大720×576画素)规格的播放能力,而到现在为止也已经成为一个主流性的趋势。

图说:使用H.264编解码晶片是从2004年,包括PSP、iPod等可携式产品开始采用。(资料来源:PANASONIC)

紧接下来,从2006年下半年开始,许多业者开始发展符合HDTV规格的数字摄影机,其中的关键点也是因为H.264编解码晶片的普及,因此透过与HDT数字摄影机的採用,H.264编解码晶片的市场规模也迅速地拓展开来。就目前来看,应用在QVGA面板达到SDTV规格播放能力的H.264编解码晶片,在功能性上还未跨入差异化的阶段,由于目前大多的影像处理产品,还处于激烈的低成本化竞争,所以在根本上,还没有实际导入H.264编解码晶片的机会性,所以在实际的产品中采用H.264编解码晶片,只有强调高阶视讯处理能力PSP的索尼硬碟/DVD录影机,以及富士的录影机「PvrAlex」等等。

就市场的需求而言,导入H.264编解码器晶片,让QVGA的面板达到SDTV播放效果的需求仍旧相当的小,最主要的原因还是在成本与应用上面,因为到目前为止,尚未有杀手级的软件或应用出现,来逼迫这些产品必须完全提供H.264编解码能力。以实际的售价或成本来看,目前提供H.264录影功能的DVD相关产品,在包括了SoC和各种中级软件的开发之后,价格有可能往上增加4,000元以上,也就是说消费者在增加花费之后,以现阶段而言根本感受不到具有H.264编解码能力产品的优点,另外在加上,即使利用H.264的高压缩率来减少硬碟的容量,但是目前来说1台硬碟的价格,不管高容量还是低容量,都不会有太大的变化,因此整体零组件的成本却是因为H.264编解码能力而大幅度的增加了。即使产品是以能够大幅度增加录影时间来诉求,但是因为现在硬碟的大容量化技术下,并且可以以低廉的价格取得储存装置的情况下,「增加录影时间」这样的诉求实在是很难对消费者产生一些吸引力。

图说:现在硬碟的大容量化技术下,「增加录影时间」这样的诉求实在是很难对消费者产生一些吸引力。(资料来源:Krollontrack)

HDTV适应件的开发正在进行中

因此现在,大部份的大型家电业者和半导体业者,对于导入H.264编解码能力的产品还是以开发符合HDTV规格的产品为主,因为在符合HDTV规格这部分的产品,看起来好像是数字摄影机和数字相机,似乎比较能够吸引消费者出现期待的心情。另外,利用H.264的压缩技术,提供地面数字广播来传送高压缩录影的用途,预计也有一定的需求。

编解码器晶片的结构有三种

就目前技术而言,期望能够达到H.264编解码能力,主要有3种技术结构。而在这三种技术结构中,因为各有利弊得失,所以必须根据每个产品的本身条件,来判断使用哪种技术。第1种是透过专用的编解码器电路来实现编解码能力,虽然还没有被完全单晶片化,不过日本Techno Mathematical能够提供符合这个条件的软体IP核心,利用SoC(system on a chip)的架构来运行软件IP核心,并且几乎不会造成SoC上的微处理器核心太大的负载,除此之外,如果应用在一般的微处理器上的话,所造成的电力消耗也不大,更不会让晶片的面积增加。因此,这样的技术架构是相当适合应用在消费性产品上的,例如针对电力消耗要求严格的摄影机等等可携式产品上。但是也是有其缺点存在,那就是如果计划增加支援新编解码方式,或变更计算程式的时候,就必须重新设计IP核心和SoC。软体IP核心也可以应用在FPGA上,就目前市场上透过FPGA实现编解码功能的产品有很多,例如,FPGA的领导业者Xilinx和Altera,就已经开发出了适合自己产品的H.264编解码器IP核心,来提供客户设计与采用。

图说:软件IP核心也可以应用在FPGA上,就目前市场上透过FPGA实现编解码功能的产品有很多。(资料来源:dsp-fpga.com)

另外一种,是合併使用一般的微处理器核心和DSP核心,以及再加上编解码中担任特定运算的加速电路结构。与一切都採用Hard-Wired逻辑电路的结构相比,这种结构可以透过替换使用的软件,来达到适应更多种编解码方式的灵活性。因此,这样架构的好处是,如果以这种结构来开发出SoC,未来在各式各样的产品应用中就能够拥有相当高的弹性度。另一方面因为随着加速电路的进步,更能够将电力消耗和晶片面积控制在比较低的程度,所以也相当适合应用于可携式的消费性产品。以目前而言,较多采用这种技术结构的是日本瑞萨半导体的「SH-Mobile3A(SH73380)」,和德州仪器适用于数字家电平台「DaVinci」的晶片「TMS320DM6446」,还有富士通搭载了双微处理器核心「FR450」的晶片「MB93475」等等。

利用微处理器核心上运作的中级软件,来实行编解码的运算能力,就结构上是需要透过API,将运算的一部分交付给加速电路,所以一般情况下,在加速电路的部份中,需要开发出针对庞大计算量所需要的「运作检索」的运算功能等。因此在这样的架构下,如何利用运作检索的运算来达到高解析的画质,是各业者所积极开发的电路设计。

最后一个技术方式是,利用一般的DSP或处理器,再配合编解码软件的结构。虽然这样方式的灵活性最高,但是其缺点就是一般而言,对于电力消耗和晶片面积都会造成相当性的影像,很难应用于消费性产品,特别是可携式产品。例如,针对德州仪器和Analog Device所开发的DSP,很多业者都设计出了是用的H.264编解码器软件。

利用多微处理器 实现H.264影像编解码器

其实在晶片上利用多 微处理器来实现H.264影像编解码能力,并非是新的想法。不过因为随着CMOS制程技术的进步,硬件晶片和微处理器也开始被整合到单晶片上了。例如最近,整合了DSP核心和微处理器核心的单晶片正被应用到手机中。

功能分割和资料分割

对于利用多微处理器结构来进行H.264影像编解码系统晶片设计上,从微处理器的使用方法来观察架构的话,可以考虑到功能分割、资料分割、和功能资料分割这3种。所谓功能分割,就是将设计的系统结构利用功能性的观念与以切割,并且分配给各微处理器,以应用产品来说,大多数手机所采用的系统晶片,就相当用用功能分割这样的方式,例如,可以将控制系统的微处理器和处理资料的DSP,集中到一个晶片上的结构。而资料分割就是,将某个资料群利用多个微处理器来进行同时处理,达到提高处理能力的目的,就像应用在高精细电视的MPEG-2影像编解码,将Slice的资料群分配给3个微处理器进行处理与运算。当然,利用跟踪处理高精细电视的MPEG-2影像编解码器,同样也能够实现功能分割,但是实际上,则必须根据系统的架构来开发出合适的结构。

Homogeneous与Heterogeneous系统结构

从不同观点看多微处理器系统的话,有以下这两种结构。一种是根据同一 微处理器核心开发而成的结构- Homogeneous(同质结构)。二是,根据不同架构的 微处理器核心而组成的Heterogeneous(异质结构)。以Homogeneous而言,结构中的多 微处理器,是将微处理器核心如同瓷砖一样排列,例如当实行同一程式的网路处理设计等。在应用类型上,资料分割的例子较多,大多是利用多工技术同时处理资料,提高运算能力。

而在Heterogeneous的结构中,是需要采用最合适架构的微处理器,来解决影像编解码的运算问题。但是,如果考虑微处理器间的介面,和开发工具等问题之后,和Homogeneous的结构相比,Heterogeneous的结构有较复杂的情况。事实上,也有一些多微处理器系统是採用Homogeneous与Heterogeneous混合构成。例如,应用于高阶游戏的图形显示晶片,对于面对Pixel Level的运算下,就需要Homogeneous的多微处理器结构,并且开发附加环绕身歷声等音效处理器的晶片。

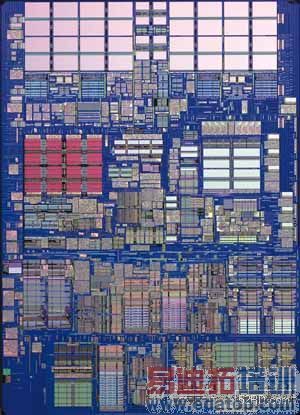

晶片内部网路衍生的问题

由于晶片制造技术和开发工具的进步,目前各业者也能够轻易地开发装载大量逻辑闸的晶片了。以目前应用来看,在一个晶片中搭配数个微处理器核心是相当普遍的,甚至也有可能在单晶片中搭配了数百个的微处理器核心。但是虽然技术能够达到这样的程度,但是如果仅是单纯的朝向仅仅在单晶片中装满了微处理器核心的话,实际上还是会出现一些问题,理由就是晶片上的电路传输网路。

电路传输网路指的是,资料交换和指令的路径。微处理器和外部(例如其他微处理器和外部存储器,微处理器以外的硬件资源等)协调进行某种资料传送或处理时,资料和指令的交换是不可缺的,因此的传输路径在晶片上变得相当的重要。)以前经常採用匯流排结构,来达到电路传输网路,例如ARM核心的AMBA匯流排等就是相当知名的晶片内部电路传输网路。

匯流排结构中,必须安排来自数个区块的匯流排存取,这时候就会产生了存取延迟的问题。由于安排先后以及匯流排存取被迫等待,会造成硬件重要的CRITICAL无法满足需要,而产生了软件的运算与执行延迟等等问题,另外,如果再加上微处理器间资料共同享有的话,匯流排上的资料传送负担会更为加大。。

图说:匯流排结构中,必须安排来自数个区块的匯流排存取,这时候就会产生了存取延迟的问题。(资料来源:act.hagale.net)

利用铁路交通架构 来解释晶片内部网路

这里以铁路为例来解释晶片内部信号传输网路。在铁路交通的服务中,为了面对需求量的增大等问题,必须先重新调整行车时间表,考量加开快速列车的可能性,并且利用在间歇时,适时地安排普通列车发车,使得传送量的增大和延迟问题达到最佳化。因为,过度增开快速列车的话,就会导致普通列车的误点变得相当严重,无法满足乘客的需求,所以自然而然产生限制。另外,设法改进车辆的结构,例如减少座位来减轻车体重量提昇行车速度,而因此获得更大的传送量等等。所以从晶片内部网路的观点考虑,这相当于Arbitration的改善、Burst Mode的导入等等,不会造成硬件太大影响,而且也可以提高资料传送能力的方式。

当铁路运输量进一步增加的话,就必须开始引进双向轨道,并列行走的Bypass道路等策略,同样这些在晶片内部网路的设计上,也可以应用这样的观念。对于延迟误点问题,就必须考虑设置连接两个车站的新路线等方式来解决,这个相当于,晶片内部开始考虑设计网状结构的网路。接下来,制定满足更大交通运输流量策略很重要的一点是,在终点站和大型转乘站中做更深入的研究,当然交通运输流量是不可能超过终点站之后还在进行传输,所以必须从上下车乘客人数,做更精细的最佳化研究。对于系统晶片来说,内部网路中最重要的终点站是外部储存介面,必须有效的控制和安排这个终点站的资料处理量,所以在晶片内部网路的设计中也是重要。

为了控制信号延迟和资料量的增大,大多都朝向设计更复杂的网路结构,这包括了和外部存储器的介面,对于每个应用程式(系统晶片)安排阶层构造,网状/环状网路和开关、缓冲装置、Arbitration等等。就像IP核心供应业者ARM,开发出了相当不错的AMBA3AXI,和以往的AMBA匯流排相比,连接结构的性能可以获得明显提高。所以网路确实很重要,所以「Network On Chip」也成为业界热门讨论的话题,例如在芬兰就举办了有关Network On Chip的国际研讨会。不过到底能否现实高效地设计网路,归根到底要看系统晶片Architecture的力量。

H.264影像编解码系统的设计

利用多微处理器结构来完成H.264影像编解码系统的设计,因为是采用软件核心的关系,使得系统晶片的应用弹性大大的增高,例如不仅仅可以支援H.264,也可以支援MREG-2,MPEG-4,VC-1等其他影像编解码规格技术,在功能上不仅能够解决硬件的限制,逻辑闸也能够有效使用。利用软件来完成这样的编解码能力,最大的目标就是期望设计出,完全不使用硬件逻辑线路的区块来达到编解码目标。H.264和以往的规格(MREG-2等)相比更为复杂,因此所採用的微处理器,是需要非常高的性能才可以顺利完成编解码的运算,例如Pentium等级的微处理器。到目前为止,利用大量硬件区块来完成运算的硬件软件复合设计是主流的趋势,在这样的架构下,有很多情况是软件掌管流量控制,而大半部分的资料处理都是由硬件执行的。

所以最佳化的利用软件进行编解码系统是,资料的存取由软件控制的DMA来担负,但是资料处理全部由软件实行。因为这样的系统架构,可以达到大幅度地降低硬件逻辑线路,所以具有相当多的优点,包括了,硬件的设计验证可以达到最小化、逻辑闸可以再次利用(因为固定功能的硬件模组相当小)、能够灵活应对结构的改变或增加、减少硬件的错误出现率。所以,能够使用逻辑闸,并灵活地支援规格的变更和增加,利用软件来完成运算处理的优点。不过软件处理也是有其缺点的,最大的弱点是,软件的并列度和硬件的并列度有决定性差异、指令存储器的必要性等等,这是因为硬件是最终的Parallel设备,因此有着潜在性错误检验的困难。

值得注意的是画质和储存

选择H.264编解码晶片时,最重要的是画质的评价。比较不同晶片的画质时,有3个阶段的评价方法。主要有Baseline Profile、Main Profile、High Profile三种。High Profile包括前面二者全部的规定。一般情况下,只要是相同编解码速度,每次按Baseline、Main、High推进,画质就会上升,但是与此同时晶片电路规模和电力消耗也会增大。在接下来的阶段,使用专用的软件计算出显示原影像劣化的尺度PSNR,在数值上面,根据经验,如果要达到显示高画质的程度,编解码速度下的PSNR,最低也必须超过30dB,如果是40dB以上,几乎无法分辨和原影像的差异,另外,主观判断还是一个最后的判断,也就是实际用眼观看编解码的影像来比较画质。

选择H.264编解码器时,另外有一点需要注意,和晶片连接的外部储存容量和储存信号线的波段幅度(资料传送速度),特别是将HDTV影像编解码时,储存信号线的速度会变得非常大,所以根据情况下,必须将2颗以上储存晶片连接起来,扩展信号线的波段幅度,特别是进行1920×1080画素的影像编解码时,更要提高储存容量,或扩展信号线的波段幅度等。不过这又会造成电力消耗和成本的提昇,相信未来短期之内,1440×1080画素的编解码还是不易实现。