- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

为匯流排和 POL转换器最佳化的 MOSFET 额定值

录入:edatop.com 点击:

随着中间匯流排架构 (Intermediate Bus Architecture,IBA)在可以降低系统成本及提高系统效率的电信功率系统(Telecom Power System)中越来越流行,MOSFET 的额定击穿电压级别也在不断地扩充,以便将导通阻抗 (RDS(on))/成本性能最佳化。本文将讨论在商用直流/直流 (DC/DC)和负载点 (POL)转换器中越来越普及的 MOSFET 特性。

固定比率直流/直流砖型转换器

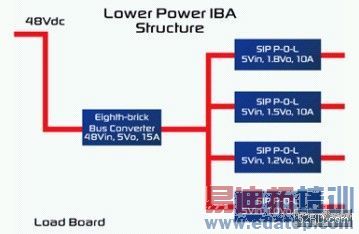

图1中的电压转换路径可为系统设计工程师带来许多效益。该结构可以让使用固定比率的直流/直流砖型转换器 ― 包括非调节、半调节或全调节型 ― 来实现有效的解决方案。其中的选择受到输入电压范围和所需稳压效果的影响。

图1. 基本IBA结构的方块图

商用电源生产商提供4:1 (12 V)、5:1 (9.6 V)和 6:1 (8 V)的变压器转换比率,以实现高效率的性能。选择的比率应能将所需的POL输出电压适当地增加到最大。例如,对5 V 和 3.3 V的输出,可选择12 V的输入。较低的输出电压可以充分利用较高的转换比率 (较低的次级电压)来POL的导通週期 (duty ratio) 最佳化,以防止高侧(high-side) MOSFET出现非常短的导通週期,否则可能带来贯通 (shoot-through)和时序问题,而带来效率降低及热效应的问题。基于与图1同样的理由,图2所示的5 V匯流排可以用于2 V以下的一组输出。

图2.可以用于2 V以下一组输出的基本IBA结构方块图

负载转换器的非隔离点

高效率的POL可以让具成本效益的解决方案不再需要基于相对简单的同步降压拓扑技术(Synchronous Buck Topology)的隔离。

匯流排转换器的MOSFET选择

为匯流排转换器选择MOSFET时,所需的额定VDS将取决于输入电压摆幅和所选择的拓扑。

输入电压

电信输入匯流排具有很宽的电压范围:

36 V 到 75 V 或

35 V 到 55 V 或

48 V +- 5% (43 V 到 53 V)

拓扑

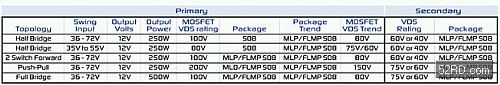

拓扑通常都与转换器的输出功率相关。常用四分一砖型转换器的典型输出功率是250 W,这个功率水准大多选择半桥架构。表1所示为适合这种拓扑及趋势的MOSFET额定电压值。

表1. 各种拓扑和输入电压的MOSFET电压额定值

初级MOSFET

额定击穿电压

过去两年间,由于电信和网路系统中的电信输入电压范围变窄,使得初级MOSFET的使用从传统的200 V / 150 V / 100 V 选择扩大到80 V 和 60 V MOSFET。

额定阈值电压

在初级驱动器中,许多都提供6 V以下的UVLO (低压锁定)阈值。这使得Vth得以提高,并有可能利用闸级氧化层(gate oxide)来降低寄生损耗。

封装

过去5年间,SO8 封装形式的 MOSFET逐渐获得採用。从使用一个D2PAK转向使用数个标准SO8 MOSFET的趋势,有助于解决电路板的散热问题,并提供较小的外形尺寸。随着功率密度增加,漏极暴露在封装底部的高热效SO8的性能也获得改善,但却不会增加占位面积。目前,这个方案正广泛地使用在电源产业中。

次级MOSFET

匯流排转换器的特点是在初级和次级中都使用相同的部件。这样可以简化材料清单(BOM),而量的增加也有助于採购时的谈判。(註:这时将有一个逻辑级的需求(在80 V 的VDS范围,MOSFET的额定RDS(on)为5 V / 6 V))。

过去,这类MOSFET的适用领域仅限于汽车应用。

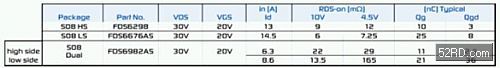

对于12 V的输出,使用40 V / 60 V 和 80 V的 低 RDS(on)MOSFET,对应于40 V、 60 V 和 80 V,其RDS(on)值范围在7.5 毫欧(40 V)、10毫欧(60 V)及16毫欧(80 V)之间。表2所示为RDS(on)和 Qg同时最佳化的适当特性。

表2 RDS(on)和 Qg同时最佳化的适当特性

非隔离的POL MOSFET选择

基于同步降压拓朴的要求,额定VDS需要在最大额定输入电压之上有一个降额因子 (derating factor)。例如,12 V输入 + 10% = 最大值13.2 V + (2V的尖波(spike))15.2 V/0.8 (20% 的降额因子)= 19 V,故可以使用VDS额定值为 30 V 的MOSFET。

业界有迹象显示未来将提供25 V的额定VDS。对于5 V和3 V来说,普遍地採用带有3条匯流排的20 V击穿电压MOSFET,并具有2.5V RDS(on)额定值以避免使用电荷泵或独立的5V电源。但缺点是2.5V RDS(on)额定MOSFET的闸级氧化层较薄,意味着寄生的电容较大,并带来较高的开关损耗。故需仔细处理硅片面积的大小,以平衡应用的传导损耗和开关损耗。

导通週期变化

高侧 MOSFET导通比率可由VOUT/VIN x 100 所支配。

于是,若输入电压12 V,输出电压1.8 V,则高侧 MOSFET导通比率为18/12 x 100 = 15%。

当则高侧 MOSFET导通比率小于30% 时,高侧和低侧(low side)一般採用不同的MOSFET。若输出电流为5 A及以下时,MOSFET供应商可提供不对称的双SO8 MOSFET。这些双MOSFET在同一个封装中有不同尺寸的MOSFET,让设计工程师能够针对其应用而进行最佳化。较小的MOSFET (RDS(on)较高,Qg较低)可在高侧使用;较大的MOSFET (RDS(on)较低,Qg较高)可在低侧使用。此外,另一个选择是为低侧器件使用带有快捷半导体SyncFET™ (固有体二极管上的肖特基二极管)器件的双晶粒。

这种改良的体二极管(body diode)可以进一步将低Qrr 和低Vf最佳化,从而提高效率。回到上述的例子中,当电流大于5 A时,单一一个SO8 MOSFET可以根据高侧及低侧进行调整,利用以Qg换取RDS(on)的做法,并视用于高侧或低侧而来决定。而且,单一一个MOSFET可为低侧提供SyncFET (见表3)。

表3. 单一的SyncFET 低侧和 SO8 高侧解决方案,以及使用SyncFET的双重解决方案

肖特基/MOSFET器件的其他优点

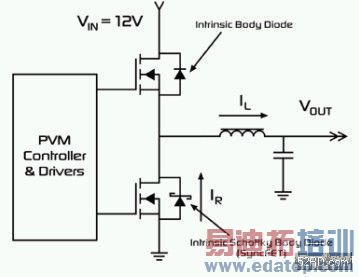

图3 所示是同步降压转换器。在这个例子中,当低侧立即关断且高侧开始导通时,有一个短暂的体二极管传导时间。低侧的关断由于体二极管的Trr而延迟。高侧MOSFET开始导通,而低侧并没有完全关断,这时就会出现贯通现象。

贯通的次级效应是效率损失,进而是高侧MOSFET的Tj增大。由于输入电压越高,功率损耗越大,使得这个现象更为严重。在使用SyncFET (整合肖特基二极管)的例子中,Trr大幅降低了。

图3. 具有低侧SyncFET的同步降压转换器

贯通现象的另一个原因

当高侧MOSFET导通时,快速开关转换在低侧MOSFET的栅漏极之间形成一个DV-DT脉冲。较高的CGS/CGD 比值 (理想为2:1)有助于消除闸级上的电压脉冲。在高侧导通时,这个脉冲可能引起低侧导通,从而造成从Vin到接地的电流尖波。这表现在低侧MOSFET为Pd较高,以及效率降低。

结论

业界继续使用MOSFET来为电信应用的参数最佳化,为匯流排转换器和POL的直流/直流功率转换提供更高的效率。而在这领域应用MOSFET技术时,必须考虑到系统架构、封装和器件整合等因素。

上一篇:次世代FPD面板显示精细度 快速朝向10BIT以上推进

下一篇:利用微处理器与软体 完成数位电视H.264编解码设计