- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速模拟数字转换器的LVDS资料输出

模拟数字转换器(ADC)的取样率正在逐年稳定的成长中,以便因应通信、测试仪器以及消费性等市场上大频宽新产品的需求。伴随着将信号链当中的信号预先数字化,以便应用在数字信号处理技术的这类需要出现,促使了高速模拟数字转换器核心的发展,朝向字转换时脉高于100MHz到200MHz,且解析度高达8到12位元的境界发展。

以单一个模拟数字转换器而言,它必须要能够驱动接收端逻辑电路,以及伴随的PCB 走线电容。然而因为驱动负载所造成的暂态电流切换,会同时回流至模拟数字转换器的模拟前端,因而对其效能产生负面的影响。要把这种影响减到最小的方法,是把转换器的两个输出埠予以多工化,并降低所需的边缘变化率,同时增加切换瞬时之间的有效设定时间,进而以一半的时脉率将资料输出。

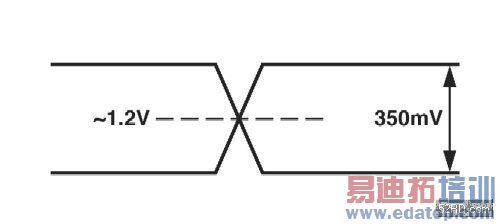

有一种新的方法,能够让模拟数字转换器在应用上提供高速的资料输出,同时又能够使其效能限制降至最低,那就是利用LVDS(low voltage differential signaling 低电压差动信号)技术。LVDS,正如其名称所描述的,是一套低电压差动信号传输架构。这里面的关键字是”低电压”(~350mv)以及”差动”。关于其标准架构及已经发展完整的规格,本文稍后将会讨论到。如同降低EMI所注重的,较低的电压信号振幅将能够获得较短切换时间所带来的最根本益处(相邻的差动走线可相互抵销EMI)。

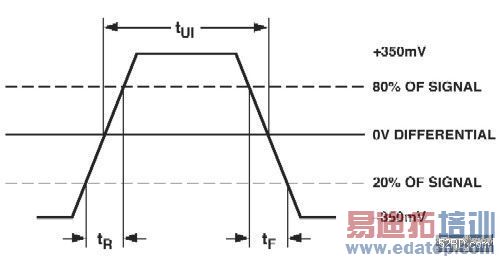

图 1. LVDS 输出位准

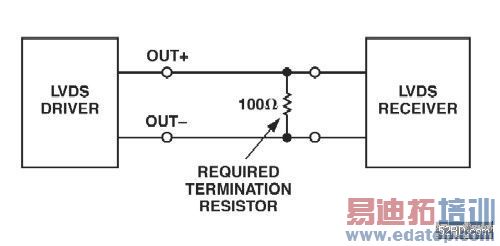

差动信号传输同时也拥有众所周知的共模互斥(common mode rejection)所具备的优点。透过设计良好的差动接收器,伴随信号所产生的噪音将能够更易于被平均分配到两个信号通道上,并且被削减掉。不同于CMOS的输出,通常是不需要安装任何终端电阻的,LVDS输出在电流输出阶段的部分,仍需要在接收器上安装100W的终端电阻。电流的输出会在输出供应的部分产生固定的直流负载电流 - 这是用以避免在电源处的电流突波与敏感的模拟前端产生耦合。

LVDS

接收器

LVDS

驱动器 100_

OUT+

OUT.

所需的终端电阻

图 2. LVDS 需要远端终端

标准

关于LVDS的定义,目前已经有两种书面标准。一种是 ANSI/TIA/EIA-644,也被命名为 ”Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits.”。另一种则是 IEEE Standard 1596.3 ,也被命名为 ”IEEE Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI).”关于这两种标准的简短说明,分别说明如下:

■ANSI/TIA/EIA-644

ANSI/TIA/EIA标准是由通信工业协会 (TIA)TR-30.2小组委员会所制订,其中只包含了LVDS的一般电子规格。这个标准的制订目的,是用来建立一个可以应用在资料通信设备之间的点对点连线,所需使用的高速传输介面标准。其最大资料信号传输速率是655 Mbps。通信工业协会小组委员会希望,其他各种标准在制订传输器与接收器间更完善的传输介面规格时,ANSI/TIA/EIA – 644能够成为其参考准据。

■IEEE Standard 1596.3

IEEE Standard 1596.3是由1992 SCI通信协定(IEEE Standard 1596-1992)所延伸发展出来的一个标准。原本的SCI通信协定是为了高阶运算所需的高速封包传送所制订,并且采用ECL标准。然而,针对低阶运算以及对电源敏感方面的应用,则必须要有一套新的标准。由于LVDS信号的电压振幅远比ECL输出来得小,能够符合对电源敏感设计上所需的较低电源供应,因而成为首选。

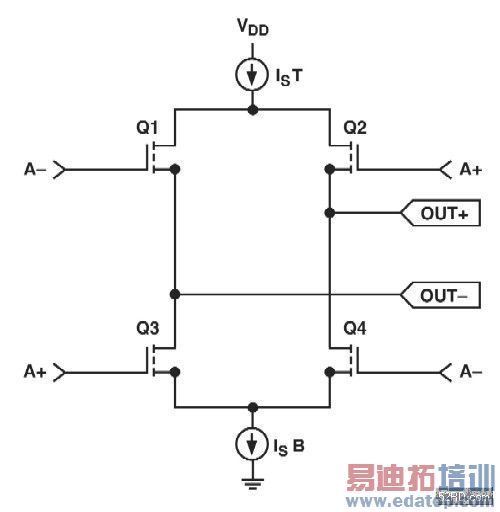

以ADI推出一款210MSPS、12位元的数字模拟转换器 - AD9430-为例,该元件中内建了LVDS的输出能力(CMOS输出仍然可用),图3是AD9430 LVDS输出的电路简图。

OUT+

OUT.

VDD

IS T

IS B

Q1 Q2

Q3 Q4

A. A+

A+ A.

图 3. LVDS 资料输出

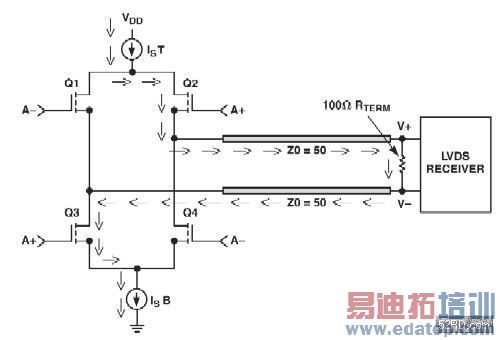

在图3中,差动输出是以「OUT+」来标示,亦即正向输出或实际资料输出,而以「OUT-」所标示的则是其相对应的差动信号资料输出。电路的操作可以下图来说明(参照图4)。来自于VDD的电流(lsT)是内建于晶片当中,并且透过Q2来做导引。在这个范例当中,数字逻辑的1 被传送出去 ( V+>V- )。接收器上的100 W终端电阻提供了一条电流路径,可以让电流透过Q3回返至较低的电流槽(lsB)并接上地线。一般电流源/汲是设定为大约3.5mA左右,藉由一个外部的100 W终端电阻,可以产生出350mV的振幅。

VDD

IS T

IS B

Q1 Q2

Q3 Q4

A. A+

A+ A.

LVDS

接收器

V+

V.

Z0 = 50

Z0 = 50

100_ RTERM

图 4. LVDS 输出电流

假设有个大约为1.2V的输出共模电压(共模控制电路未显示出),则输出电阻可以由2颗50 W电阻组成并与它们的分接器 (center-tap)串联设定在1.2V。这样的设计可以与传统的PCB走线特性的50W典型阻抗(Zo)相匹配并且将反射作用降至最低。AD9430的LVDS输出规格与ANSI/TIA/EIA – 644标准是符合的。表I中所示为ANSI/TIA/EIA – 644标准与AD9430-210规格的比较。

表 I. ANSI/TIA/EIA-644 和 AD9430 规格摘要

ANSI/TIA/EIA-644 AD9430-210

输出电流

不同于CMOS使用传统的电压输出,LVDS採用的是电流输出技术。AD9430的输出电流是利用一个电阻来加以设定,其电阻值通常为3.7k。这个3.7k的电阻使得输出电流值为3.5mA。请注意到在AD9430中,这个3.5mA的一般输出电流是可以调整的,以便于让某些系统在设计上能够更具有弹性。

差动输出电压以及偏置电压

在ANSI的规格中,定义出差动输出电压振幅是介于247 mv到454mV之间。假设类比数位转换器的输出部分,输出电流设定为3.5mA,接收器的输入阻抗是100,则一般差动输出电压就是350mV。AD9430的输出驱动器是专用于1.2V共模电压,恰好符合了ANSI规格。共模电压范围是设定在1.1V到1.375V,以便在驱动器与接收器的地线之间产生最多1 V的地电位偏移(ground shift)。为了达到最佳效能,必须要让同一电路板上的模拟数字转换器输出端,与接收器输入端的位置非常靠近,这么一来就可以不需要顾虑地电位偏移所产生的影响。

转换时间

在表I中,ANSI/TIA/EIA – 644标准的规格对于信号转换时间的定义是:当资料信号率低于或等于200MHz时,信号转换时间必须低于或等于0.3 tUI。tUI的值是依据资料取样率的相反值来定义。在AD9430的例子中,最大的取样速率是210MHz,所以tUI的值就等于4.76ns。将tUI值4.76ns代入规格表里面的公式计算,0.3 x 4.76ns = 1.43ns。因此,差动信号的上升时间(tR)以及下降时间(tF),其总和应该要低于1.43ns。以AD9430而言,其上升及下降时间值都只有0.5ns。图5中所列举的是LVDS差动输出电压,其上升时间以及下降时间的定义。LVDS对于上升以及下降时间的定义,是以在最大信号强度的20%至80%之间变动的信号时间为依据,不同于CMOS输出的上升下降时间,其定义通常是在10%至90%之间。

tUI

tR tF

+350mV

讯号的80%

0V 差动

信号的20%

.350mV

图 5. 时序图

在数字逻辑上,对于高效能模拟数字转换器的LVDS输出部分,应该要以不同于标准LVDS输出的方式来看待。在高速的数字应用方面,即便标准LVDS能够驱动1到10公尺的距离(取决于资料的速率),仍然不建议你让一个高效能模拟数字转换器来驱动如此长的距离。比较建议的方法是将输出走线的长度缩短(<2英吋),这样可以使得相邻电路羊在输出时所伴随产生的噪音,因而回流至模拟输入端的机率降至最低。差动输出的走线应该要紧密地布线,将100的终端电阻与接收器尽量贴近,将可以让共模互斥尽可能的提高。使用者应该要注意PCB走线的长度,以便降低任何可能的延迟歪斜(delay skew)。

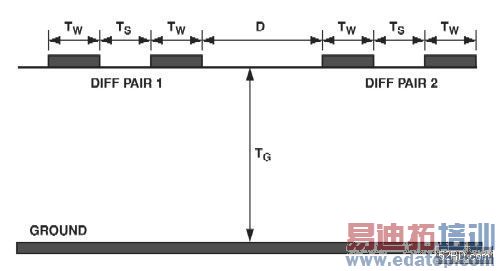

图6所显示的是传统的差动微带(microstrip) PCB 的剖面图。

TW TS TW D TW TS TW

差动对 1 差动对 2

TG

地线

图 6. PCB 走线布局的空间

布局方面的指引

⊙确保 Tw,Ts以及D的走线长度是固定的

⊙确保 Ts ~< 2 Tw

⊙尽可能避免使用过孔(vias)

⊙确保 D > 2 Ts

⊙尽可能避免90度转折

⊙将Tw和TG设计为 ~50

对于这些快速 (< 0.5 ns)边缘变化率而电源供应器的去耦是非常重要的。一个具有低感应系数,能够使用表面黏着的电容器应该要安置在每一处电源供应器以及地线接头的周边,并且尽可能的靠近模拟数字转换器。不建议你在电路板的另一端放置去耦电容,因为通孔电感会使有效去耦的能力降低。每个导体的差动Zo将会有比单端Zo略低两倍倾向,这是原因于近接效应 - 每一条线上的Zo在设计上应该要略微高于50。在关键性的应用上,可以先进行模拟,以便确认阻抗是否匹配。以目前来说,这点还不是那么重要。

其他设计考量

在降低EMI值方面,LVDS也提供了一些好处。由反向电流所产生的EMI磁场会有相互抵销的倾向(以相互搭配的边缘变化率而言)。走线的长度,歪斜失真以及中断,都会降低这个效益,因此应该要尽可能的避免。相对于解多工(demuxed) CMOS 解决方案,在近似的资料速率下,LVDS也提供了较简单的计时限制。解多工资料准流排(demuxed databus) 所需要的同步信号,在LVDS中是不需要的。在解多工CMOS准流排中,需要一个相当于模拟数字转换器取样速率一半值的时脉,再加上成本以及复杂度的增加;这些种种在LVDS中都是不需要的。大体而论,LVDS有较大的容错度,并且能够由客户导引出更简单、更俐落的设计。

总结

在高速信号传输上,藉由降低噪音耦合至转换器核心所造成的影响以及降低EMI值,LVDS所具备的优点可以在转换器的应用上提供更好的效能与系统效益。

上一篇:分散式远端监控水产养殖资讯管理系统

下一篇:利用软件开发出高弹性影像编解码系统