- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CDMA移动手机本机振荡器的设计策略[多图]

本地振荡器(LO)的设计和性能对手机能否达到或超过最初的设计目标有很大影响,大多数为北美市场设计的CDMA手机也包括AMPS,以便为那些尚未安装数字基础设施的地区提供服务,针对这些应用的手机可能需要8个不同的LO信号。本文讨论影响CDMA手机LO的设计问题,并利用PLL合成器来探讨LO的性能、标准要求和设计方法。

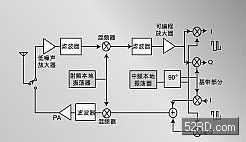

目前,大多数CDMA手机采用的是图1所示的超外差无线结构,在典型的CDMA应用中,接收到的无线信号由频率范围介于900 MHz至2.0GHz之间的高频载波信号及经过调制和编码的低频数据信号混合而成。

LO为混频器提供输入,对CDMA手机来说,它通常是一个PLL(锁相环)合成器,PLL合成器可通过多种不同的途径来实现。由于CDMA需要多阶频率转换,PLL合成器必须生成非常精确的信号,否则手机会与其它通信信号相互干扰或阻碍解调,从而导致误码率(BER)增大,降低语音和/或数据质量(图1)。

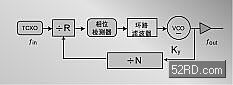

图2给出了PLL合成器的方框图。典型的PLL合成器由分立VCO(压控振荡器)、分立环路滤波器和合成器IC组成。合成器IC包括参考分频器(R分频器)、整数或分数N分频器以及鉴相器,但不包括VCO和环路滤波器。几家CDMA收发器制造商已开始在其芯片中集成可选的PLL合成器功能,以减少元件数目及简化设计。考虑到复杂性问题,目前尚无法在这些芯片中集成RF VCO,因而现阶段尚未开发出完全集成这些功能的CDMA收发器芯片。

PLL合成器输出频率可由方程(1)确定:

中心频率fcen可由方程(2)计算得出,fcen应是LO所生成的输出频率频谱的中心频率。C和L表示振荡所需的VCO振荡回路。一旦fcen确定,基带处理器或板上DSP可通过改变N分频器的值将输出频率fout调整到特定的频道。

确定输出频率

设计PLL合成器的第一步是确定手机要求,即需支持的频带、模式和收发器要求。在北美,有两个频带分配给了商用数字蜂窝通信,如表1所示。大多数移动电话制造商同时支持数字和模拟(AMPS)通信,以扩展覆盖范围。由于综合数字网络的成本极高,业务运营商更倾向于将AMPS作为未来移动电话的一个选项。

频带为确定PLL合成器的输出提供了一个起点,精确的输出频率要求取决于收发器和无线频率分配规划,频率分配规划是所有无线结构开发的中心环节。IF和RF LO所选的实际频率必须在研究过伪混频、谐波干扰及所选实际频率的元件适用性之后才能确定。

大多数CDMA收发器采用超外差式结构,该结构同时包含RF和IF上变频和下变频两级。为方便混频,必须同时以两种频带在发送和接收路径上为每个混频器提供RF和IF LO信号。

双频手机通常需要两种或更多不同的RF LO信号,这取决于发送和接收混频器是否需要不同的频率(视收发器和无线频率分配规划而定)。因此,RF LO必须具备用于双频工作模式的两个或更多分离RF PLL合成器。在IF混频级,每个频带要求至少两个IF LO信号以便于双向通信。然而,某些CDMA收发器方案在两个频带上复用同一IF频率,从而减少了设计所需的元器件数目。

参考频率

fin由可用的收发器和基带方案予以标准化,由此规定了手机的频率分配规划。典型的参考频率如表2所示。

方程(1)中,注意到fin和R分频器的混合决定了鉴相器的刷新率(update rate)及信道或信道栅(channel raster)的间距。表2还包括相应的R分频器值,为AMPS生成适当的信道栅间距,以及为CDMA生成适当的栅间距。对于蜂窝基带,30 kHz的刷新率可为AMPS提供30 kHz的信道间距,并为CDMA提供30 kHz的信道栅。PCS基带需要50 kHz的信道栅。

目前已提出了LO物理约束的基本框架,下面将重点讨论为满足正式和非正式标准要求,设计必须达到的性能规范,如相位噪声和稳定时间等。

相位噪声

CDMA标准并未直接阐述用于RF下变频的CDMA PLL合成器的精确相位噪声性能,只是间接定义了单音信号去敏(Single Tone Desensitization)的要求。单音信号去敏规范可保证在1.25MHz CDMA信道带宽上接收到高功率窄带干扰信号时,CDMA接收器仍能继续工作。

该标准规定,95%置信区间内的最小误帧率(FER)为0.01。由于较大的干扰带有-30dBm的功率电平,偏移量为1.25MHz时,系统的相位噪声约为-136dBc/Hz。注意到该相位噪声规范适用于整个RF系统,而PLL合成器只是其中一部分。如果在规范中留有-4dBc/Hz的裕度,在偏移量为1.25 MHz的条件下,PCS基带的PLL合成器大约应为-140dBc/Hz。具体实现将根据收发器性能和无线设备的其他特性而定。通常,减小PLL合成器引发的相位噪声有利于系统其他部件获得更大的相位噪声裕度。

也许双模手机最大的挑战在于必须达到AMPS标准规定的相位噪声水平。在AMPS中,由于语音数据不能像在CDMA中一样较广的带宽上以数字形式发送,AMPS相位噪声的性能就显得尤为重要。另外,与载波信号仅相差60kHz的信道干扰将使得接近中心的噪声性能更加突出。为满足AMPS要求,PLL合成器在60kHz偏移量的条件下,所生成的相位噪声不得超过-120 dBc/Hz。

稳定时间或死锁时间

稳定时间或死锁时间是指在规定的频率或相位精度条件下,PLL合成器输出达到稳定所需的时间。大多数通信系统规定LO需要在功率放大器接通之前,在传送通路中设定0.1ppm的频率误差。这样可防止手机在所期望信道以外进行信号传送并与其他手机相互干扰。在某些通信系统中,接收端的稳定时间是以相位误差的均方根形式进行描述,该相位误差给出了所接收的数据组群被解调的位置。

与相位噪声一样,CDMA规范并未规定确切的PLL合成器稳定时间。然而,该标准规定了最终限制稳定性能并影响PLL合成器设计的系统性能参数。总之,由于CDMA采用直接序列扩频方案,PLL合成器的稳定时间与多接入方法关系不大。在GSM或跳频系统等其它通信系统中,LO必须不断改变频率,这对PLL合成器稳定时间要求而言,无疑增添了更多的麻烦。

从系统角度看,CDMA规范中至少存在两个限制手机响应时间的因素:其一为硬切换(Hard Handoff)条件,此时移动手机必须在小区之间进行不连续的转换;另一因素与采用异步消息接收方式将手机配置在分时段寻呼模式有关。下面将根据对PLL合成器设计的影响,详细阐述这些条件。

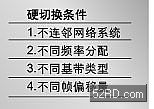

硬切换

在CDMA中,需要两种切换:硬切换和软切换。软切换是首选的小区切换方法,因为其“中断之前即切换”的工作方式可减少潜在的错误,并将对用户的影响降至最低。然而,CDMA移动手机应当在“中断之前即切换”工作方式 (参见表3)下也支持硬切换。当基站引导移动手机在两个不相邻网络系统、不同频率分配、不同帧偏移量或不同基带类型的条件下进行切换时,将启动CDMA至CDMA的硬切换。而当基站命令移动手机变换到蜂窝基带模拟语音信道(移动手机必须支持AMPS)时,将启动CDMA至AMPS的硬切换。在任何一种情况下,PLL合成器都必须迅速更换频率并在新频率下达到稳定,以满足系统的时序要求。

当需要在手机和新业务小区或区段间更换频率时,必须启动硬切换。由不同小区中的不同频率进行硬切换后,移动手机重接入小区的过程包括调整新频率和搜索新导频信道。CDMA规范要求所有事务必须在60毫秒(msec)内完成。

为了在蜂窝电话网络内均匀分配负载,业务信道帧将作为系统时间的偏移量,“帧偏移量”以1.25毫秒的增量予以划分。为了支持软切换,目标小区必须使用与当前业务小区相同的帧偏移量。如果不能满足这一条件,则必须进行硬切换,这类硬切换必须在20毫秒内完成。

PLL合成器的稳定时间是硬切换完成时间的一部分。如果不能满足这些硬切换持续时间的限制要求,那么语音质量将受到影响,甚至导致通话中断。移动手机必须调整到新的频率,查询新导频信道,接入新信道,然后再发送切换完成消息。对上述提及的任何情形,硬切换的界限在帧偏移量条件下为20毫秒,而在其他硬切换条件下为60毫秒。这段时间中,PLL合成器必须只消耗总时间的很少一部分,因为功率放大器等部件将在骤开骤关中消耗大量的时间。如果PLL合成器可迅速稳定,那么更多的时间可用于为其他功能块执行切换任务。在硬切换情况下,设计人员通常分配大约1至2毫秒的切换时间。

分时段寻呼模式

移动手机开启后,即开始搜索导频信号、接入导频信号和同步信道的初始化进程,然后进入空闲状态。空闲状态下,手机监视寻呼信道,以确定该终端是否设置了呼叫。CDMA规范规定了两种不同的监视寻呼信道方法:分时段和非分时段寻呼模式。在非分时段模式中,手机监视寻呼信道的每个时段。该监视模式虽然很有效,但由于手机的RF部分必须时刻保持通电,电池会很快耗尽。

而分时段寻呼模式可让手机只在特定时段监视寻呼信道,16帧组成一个时段,而每帧的长度为80毫秒,总周期为1.28秒(见图4)。

在分时段寻呼模式下,当不监视指定时段时,CDMA无线部分将断电。到了监视时段时间,PLL合成器必须被“唤醒”以接入寻呼信道,“唤醒”时间包含在图4所示的重接入过程中。当基带软件为RF部分通电时,同样也使PLL合成器通电。但在重接入过程开始之前,PLL合成器的输出必须稳定。基带处理器等待接入寻呼信道的时间越长,就越节省电能。不同于硬切换情景,一旦用户停止通话,手机就可进入分时段寻呼模式,这可能占用手机开启状态的大部分时间。因此,由PLL合成器稳定时间节省的任何时间都有助于延长电池的寿命。典型的PLL合成器方案约需1毫秒时间达到稳定。

降低整机功耗

降低整机功耗是一个重要的目标,因为功耗直接影响电池的使用寿命。为降低手机功耗,低电压和低于3V电压工作将成为发展趋势,因而对PLL合成器设计将产生多重影响。PLL合成器的功耗有助于降低噪声电平,因此有利于改进性能。然而,低电压也使得VCO更难调谐,除非同时增加环路带宽和VCO增益(Kv)。方程(3)粗略地表达了这一关系,增益增加将增加噪声和系统对VCO及充电泵非线性的敏感度,由此增加相位噪声。快速稳定时间是另一个期望的特性,通常要求增加反馈和充电泵速率,这在低电压下更难实现。

调谐范围=输入电压* Kv (3)

结构上的折衷

鉴于上述原因,必须在分立、部分分立和单片IC三种实现方案之间进行结构上的折衷。尽管完全分立方案具有更大的灵活性,但也增添了更多的设计任务,因为PLL合成器的每个功能块必须从头开始设计。分立方案还需要较多的部件,这会影响元器件的采购,对库存的要求也较大,元件的稳定性较低,还要占用额外的板空间。由于这些因素会影响产品成本和面市时间,CDMA手机开发通常不采用完全分立的设计方案。

部分分立方案利用商业化的合成器IC和VCO,减少了元器件数目,也简化了设计。实际上,许多商用CDMA收发器集成了PLL的各种部件--从设计的角度看,这些部件包括外部VCO和/或振荡回路,以及回路滤波器。对于双频应用,要在指定的频带上更换适当的PLL回路滤波器,必须使用切换电路。该方法的缺陷在于如果性能参数不能满足系统规范或目标,PLL合成器设计人员几乎没有替代方法。

对于PLL合成器功能全部在单片IC上的全集成PLL合成器方案,其优点在于将外部元件数目、设计工作量和产品尺寸降至最少,而且其相位噪声和稳定时间性能在许多情况下均优于其他方法。此外,在双频带应用中,为简化开发而改变环路滤波器时,该方法不需要切换。该方法的缺陷在于目前市场上只有很少产品能在单片IC上集成完整的PLL合成器。

总结

为CDMA移动手机设计LO时,必须考虑许多因素,本文讨论了现今CDMA手机开发人员面临的一些问题。成功设计PLL合成器的关键在于清晰了解开发标准和系统目标,并掌握相应的技术知识。

作者:James Kimery

Silicon Laboratories

Email: jgk@silabs.com