- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

系统设计面临不断变化的挑战

随着工艺技术从40 nm向28 nm的发展,不可避免的尺度效应改变了基本单元的电特性——芯片设计人员必须采用的晶体管和互联导线。这些新的晶体管级难题也导致了系统级IC体系结构、实现以及性能的改变。这些芯片级变化建立了新领域,系统设计人员必须在其中开辟新途径。

IC面市以来,工艺尺度一直在不断进展。在每一新工艺代,最小特征尺寸都减小了大约三分之一,最小的晶体管占据的面积也减小了两倍。同时,数字电路的最大时钟频率在增大,功耗也在降低,其变化都相对稳定。那么,在每一新工艺代,芯片设计人员能够为系统开发人员提供新IC,集成了更多的功能,速度更快,而功耗更低。但是,这些都一去不复返了。

今天,为了减小晶体管的尺寸,工艺开发人员不得不提供给芯片设计人员涉及到速度、功耗和成本的一系列复杂条件。芯片设计人员必须采用他们所有的工具,包括新的电路设计、新体系结构方法,并对算法进行根本的修改,以便能够以相竞争的价格继续实现更好的性能,而功耗在可接受范围内。目前为止,这些方法是有效的,但是系统设计人员对此并不了解。28-nm工艺代的确是系统设计的新时代:在这一时代,系统设计人员必须理解提供硅片的芯片设计人员面临的难题及其决定。

简单尺度的结束

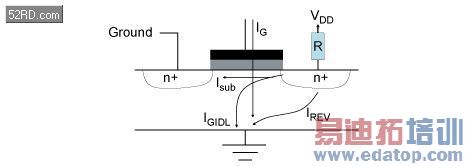

工艺工程师认为,基本问题在于随着晶体管尺寸的减小,互联部分越来越短,电信号特性也在不断变化。随着晶体管的减小,它们无法自动提高速度,而是开始泄漏。那么,在28 nm,设计人员看到晶体管不再像以前那样在各方面都继续提升性能,而是出现了复杂的变化。您可以简单的减小40-nm硅氮氧化物栅极晶体管的尺寸,实现相对较低的圆晶成本。但是,您既不能实现最高速率,也不能实现最低功耗。您可以通过应变工程提高速度,采用高k/金属栅极(HKMG)堆减小泄漏电流,但是增加了成本。在一定程度上,您可以通过改变工作电压来综合考虑功耗问题。您可以通过控制晶体管的阈值电压,或者设计修改,应用体偏置,牺牲速度以减小泄漏电流。但是,对于所有应用,没有一个最佳平衡点,能够以最低功耗实现速度最快的晶体管。

主要

- 降低电压

- 提高电压阈值

- 延长栅极长度

- 掺杂参数优化

主要

高k金属逻辑门(HKMG)

小

掺杂参数优化

反向偏压结泄漏电流 (IREV)可忽略

掺杂参数优化

同时,晶体管电路的最基本单元——走线,也成为一个问题。随着晶体管尺寸的减小,互联前几层的走线相应的变窄。但是,现代工艺通过充满高电阻率阻隔材料来处理这些窄沟道互联,其目的是保持铜原子多孔低k绝缘。随着工艺尺寸的减小,沟道越来越窄,但是,阻隔材料并没有变薄,因此,铜的空间更小,阻抗也就越来越大。更糟的是,在工作温度时,铜材料填充区现在靠近电子的平均自由通路,因此,铜电阻率明显增大。总体上,最底层的互联电阻增大了,进一步降低了晶体管的性能,增大了功耗。

因此,随着工艺的发展,芯片设计人员目前看到了有意思的场景——密度增大了,但是,更需要综合考虑速度、功耗和成本因素。结果是,在很多情况下,芯片设计人员发现采用新工艺技术后,速度并没有很大的提高。

IC设计的新方向

28-nm工艺节点最大的好消息是显着增大了晶体管密度,也就是在给定区域中,能够容纳更多的逻辑门、寄存器和存储器。在很多应用中,前几代系统级IC已经集成了适合集成实现的大部分功能。那么,在28 nm,芯片设计人员很容易使用所有这些额外的晶体管来提高性能,降低功耗,而这是调整工艺无法实现的。或者,他们选择更小的管芯来降低成本。他们也可以选择组合使用这些方法,定制实现某些特殊的应用。

在很多情况下,芯片设计人员会选择尝试实现系统开发人员所期望的芯片级性能指标。他们可以通过使用晶体管来提高性能,在应用中,发挥内在的并行功能的优势。

发挥并行功能的优势

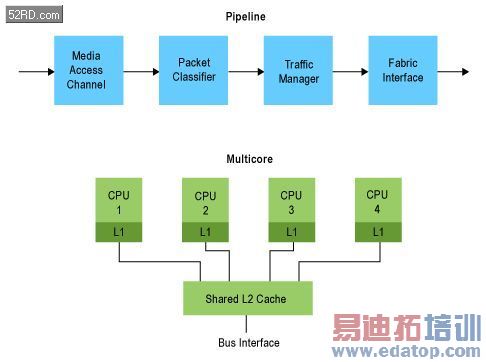

有几种方式来实现并行功能。至少与应用相关的一种方式是简单延长设计中执行单元的流水线,在指令级一次执行多条指令。对于数字算法的内循环加速器等应用,例如,数字信号处理,这一方法特别有效。但是,在通常的计算中,研究表明,同时一次执行三条指令反而会降低性能。

一种密切相关的方法是建立功能级模块流水线,这是数据包处理应用中目前常用的方法。在这种方法中,数据通过处理器链,每一处理器都对数据进行某一特殊的功能处理。这类流水线与具体应用密切相关,如果功能与状态或者数据相关,在执行过程中,设计人员尝试改变流水线的工作时,设计会变得非常复杂。

目前在并行方面最流行的方法是多处理器,很多处理器从共享存储器中采集数据和任务,并行工作。在这方面有很多变化。数字加速器通常使用单指令多数据(SIMD)群,每一处理器单元装入不同的数据,但是,都使用公共的指令流。在处理器群中,每一处理器完成固定的任务,从输入序列中采集数据,在输出序列中产生结果,彼此相互独立。还有全动态多核设计,完全相同的处理器从工作序列中采集任务和数据,执行它们,除了内部任务通信之外,彼此独立工作。

所有这些方法都有效的提高了系统级IC的处理带宽。或者,芯片设计人员可以通过并行方法来维持性能不变,但是减小了每一独立处理单元的时钟速率,支持采用更低的工作电压,以及低泄漏晶体管和相似的低功耗方法。但是,只有具体应用有足够的并行功能,处理单元保持忙状态,不会中断时,这些方法才有效。但这是很大的挑战。

可能最明显的问题是以足够快的速度实现管芯数据的输入输出,以跟上处理能力的变化。芯片设计人员能够成功的使用越来越强的并行功能以提高芯片处理带宽。但是,I/O带宽和存储器带宽都没有及时跟进。越来越有可能设计系统级IC,但实际上无法很快的移动数据以支持自己的处理速度。

由于复杂的DRAM时序,采用并行功能进一步加剧了这一问题。如果DRAM必须支持不同处理单元或者高速缓存控制器存储器不同任务的存储器申请随机散射功能,那么,页缺失的频率会明显增大,影响总带宽和DRAM传送的预测能力。非常复杂的DRAM控制器能够解决这一问题,但是,代价是增大了每一处理操作的延时不确定性。类似的,芯片设计人员会采用基于收发器的高速串行总线,例如,PCI Express? Gen3等,或者Interlaken等芯片至芯片连接技术以提升I/O带宽。但是,很多处理器单元不协调的申请会影响最佳突发或者流总线协议,降低了快速I/O的效率。

降低功耗

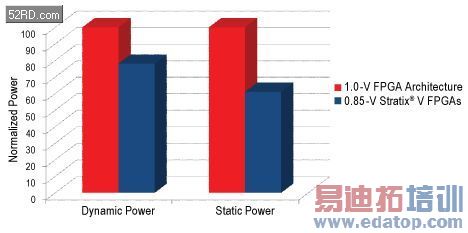

芯片设计人员可以使用28-nm工艺额外的晶体管再度提高性能指标,甚至可能利用晶体管来降低功耗。从一开始就选择应用最佳工艺来提高效率,选择晶体管阈值电压和工作电压的最佳组合。某些设计会在芯片的整个逻辑部分选择一个工作点。其他的在不同模块上采用不同的电压,只有很少的会根据特殊管芯的性能要求、温度以及固有速度来动态调整关键模块的工作电压。类似的,很多设计采用了具有不同阈值电压或者可调阈值电压的晶体管,选择足够快的晶体管,使模块甚至是某一时序通路达到时序收敛。某些设计还会关掉空闲模块的时钟或者电源。这类动态方法实际上非常有效,但是带来了晶体管成本问题,以及功耗开销,增大了延时,例如,时钟频率或者电压转换延时等。

系统设计人员的任务

芯片设计人员追求的主要策略——增强并行使用,依靠宽带外部存储器,寻找更大的I/O带宽,以及总功耗管理等,这都会影响使用IC的系统开发人员。这些影响涉及到算法设计、软件开发、电路板设计以及最终的封装和散热设计。

在算法级,越来越多的依靠并行硬件带来了变化。例如,与高速的单个处理器相比,并行处理通常能够显着增大延时——输入出现在芯片上的时间与其出现在芯片输出之间的时间差。系统设计人员必须要理解这些越来越大的延时对系统行为的影响。另一可能存在的问题是并行方法,特别是多处理,需要修改算法才能实现所需的数据或者并行任务。系统设计团队有足够的技术能力和文档来改变基本算法,或者他们能够依靠IC供应商来获得帮助吗?

对I/O带宽越来越大的需求带来了系统级难题。通过不断增加快速引脚的数量来实现所需的吞吐量,这会在电路板设计上带来难以处理的布线和信号完整性问题。相应的,芯片设计人员越来越多的采用基于收发器的高速串行总线和链路,例如,包括PCI Express Gen3和Interlaken等。DRAM供应商进一步推动了这一趋势的发展,其理念包括串行端口存储器技术组,以及Micron的混合存储器立方计划等。在所有这些情况中,当数据输入输出管芯时,高速串行链路能够显着增大带宽,降低传输功耗。但是基于收发器的链路有自己的延时问题,系统设计人员还是要理解这些延时对系统行为的影响。

功耗管理带来了另一些难题,怎样解决功耗这一问题已经从工艺工程师传递到芯片设计人员,以及系统设计人员。对于这些难题,需要首先正确的理解最终系统的应用指标。在哪些环境下需要哪些任务,每一任务需要多大的性能?在某一应用模式中,任务和每一功能模块的相对比例是多大?这些问题的答案会影响基本工艺技术的选择,以及功耗管理协议的选择。在后一种情况中,对于系统设计团队而言,非常重要的是理解系统需要什么样的IC功耗管理。电路板需要提供多种电压吗?必须要改变它们,或者接通关断它们,如果这样,控制器会有多复杂?

更重要的另一点是,软件在多大程度上理解应用指标,能够应用多少这类知识。例如,如果系统软件不能正确的预测主要模块不工作的时间,并将这一信息传递给功耗管理系统,那么,芯片级复杂的功耗管理协议实际上会浪费而不是减小功耗。

结论

在28-nm时代,系统只能通过积极的选择半导体技术,与芯片设计和系统设计积极的进行交流才能满足性能、功耗和成本需求。在后面的文章中,我们将研究供应商Altera怎样解决所有这三个难题,以及与管理设计团队密切相关的问题,从而保证系统设计实现最佳产出。

上一篇:EMI干扰 :传导是罪魁祸首

下一篇:5G WiFi时代,802.11ac设备面临的大批量测试挑战

国内最全面、系统、专业的手机天线设计培训课程,没有之一;是您学习手机天线设计的最佳选择...【More..】

国内最全面、系统、专业的手机天线设计培训课程,没有之一;是您学习手机天线设计的最佳选择...【More..】

我们是来自于研发一线的资深工程师,专注并致力于射频、微波和天线设计工程师的培养。