- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

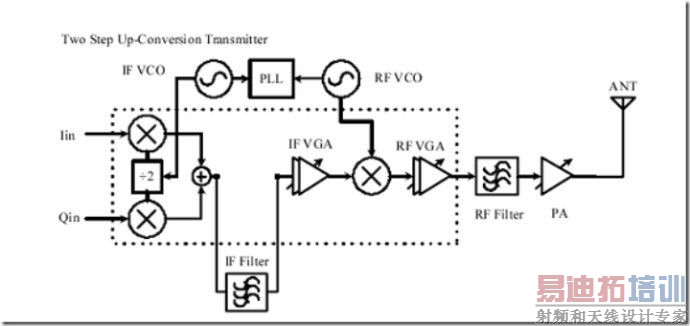

2倍频VCO是否会彻底解决VCO pulling?

在criterion的上集_磁珠(Bead)_电感(L)_电阻(R)_电容(C)于噪声抑制上之剖析与探讨,page19,提到了电源输出会产生2倍谐波的噪声。请问这个是为什么?

对于楼下因为灌水而加RD币的楼层,我已经一一把RD币扣了回去。我当初是想鼓励踊跃发言,所以杜绝……

2倍频确实相对于直接上变频会相对好一点,但是还是存在二次谐波的干扰,无法做到根本解决

目前为了解决VCO pull不是通过选用2倍频的VCO去解决的。反而现在的手机由于空间限制,电流限制等更多的采用的是DCT(零中频)架构。

DCT架构的接收机Tx Freq与Lo的频率是一样的,MTK一般LO Freq是3.6G左右,即low band Lo=4Tx,High band Lo=2Tx,经过4或2分频到mixer。

对于这种架构,如果PA产生的 low band Tx 4th harmonic或者High band 2nd harmonic干扰到RF PLL部分会产生Phase Error,大部分情况下low band 4th harmonic会比较小,不容易出问题,而high band 2rd比较大,常出现high band phase error的问题。

而来解决你说的VCO pull的问题更多的是采用其他的方式,如:

1.增加双工器的隔离度

2.提高ASM的隔离度

3.提高SAW的隔离度,甚至有一些频段离得比较近的会采用BAW FBAR工艺

4.将transceiver和PA的链路通过屏蔽盖隔开

当然以上只是仅仅讨论到了VCO PULL,其实为什么要关心VCO pull,不过是VCO输出的相位会受到干扰的牵引,这就是所谓的VCO pulling,即本振牵引,引起相位偏移。

*2也只能减弱些影响。

同样有疑问,mark以及

同样有疑问

有疑问,关注中。

我也想知道原因

电源产生的谐波个人觉得二次谐波能量强一些(当然还有三次谐波...),干扰大一些,所以用电容滤波。

如criterion 所言,VCO Pulling 干扰主要来源为PA output和ANT port端。详见:VCO_Pulling对于零中频发射机之相位误差的危害

不解决问题,

调PA输入端匹配可以 优化VCO pulling吗?

学习一下

学习一下.

学习一下

关注,学习

等待结果,学习学习

据说要5字。

学习一下资深工程师的高见

学习一下

电源为何输出2次谐波呢?同问。 2倍Lo应该是降低影响吧,但是为何不1/2呢? 不理解

资深工程师解释一下

申明:网友回复良莠不齐,仅供参考。

上一篇:LTE 信道号

下一篇:CMW500怎么测试非信令TDSCDMA的啊?