- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于载波泄露

木有人吗

调调天天调

天机不可泄露

我的理解载波泄露一般是发生在上变频时,是不同信道之间或同信道内部的干扰,一般手机测试这部分的测试项为邻信道泄露比和带内杂散,希望对你有帮助,也欢迎大家指正。

一般发生在一次上变频,因为中频距离射频很近(只有一次变频),所以滤波器对载波抑制有限,导致载波泄露到射频口,射频放大器工作带宽很宽,肯定会把载波也放大发射出去,这样会造成很多不良后果:比如临近信道干扰、功放效率降低、EMI等, 可以选择谐波混频器,或混频器后多级滤波器。

GSM的ORFS和WCDMA的ACLR,有这相同指标意义,都是在衡量对邻近信道的干扰程度。

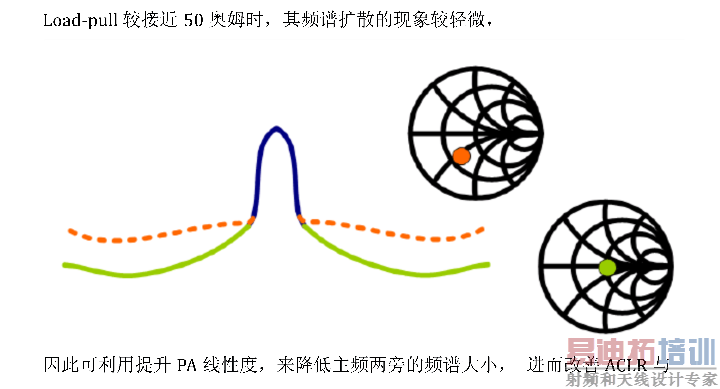

以电路观点,ACLR是衡量WCDMA整体发射端电路的IIP3,越往后级的IIP3,对整体线性度影响最大,而PA正好为发射端电路的后级,因此对于整体发射端的线性度有很大的影响。

一种可能的情况是transiver出来的信号对载波抑制不好,同时duplexer的收发隔离不够,是的载波和发射信号混频到接收频段的信道内,影响灵敏度

可以试试看用频谱仪看下发射通路的频谱

Delete!!

高手啊

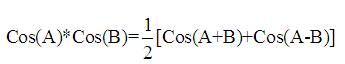

传统Double sideband Modulation (DSB)

A是LO频率B是基频频率也就是Data的频率

如此便可得到(A+B)跟(A-B)的信号频率

但这样太浪费频谱 所以衍生Single Sideband modulation(SSB)

或是

也就是说 理论上频谱只能出现(A+B)或(A-B)的单一Sideband信号频率

但实际频谱 不可能只有信号频率会有以下这些产物

IM3跟IM5就是因Tx端线性度不够 所出现的3阶跟5阶Intermodulation

IM3会影响LTE的E-UTRA 而IM5则是E-UTRA跟UTRA都会影响

所以GSM的ORFS或WCDMA/LTE的ACLR

指的是信号两旁频谱涨起的现象 也就是所谓的频谱再生

多半是IMD3或IMD5的产物 并非载波泄漏

因此调PA的Load-pull 是无法改善载波泄漏的

至于频谱上的Carrier才是载波泄漏

载波泄漏的生成原因 多半有两个

1. LO泄漏

2. I/Q讯号上的DC Offset

第一点 倘若Mixer的隔离度不够

那么LO的信号 会直接泄漏到频谱上

这就是LO Leakage

第二点 则是I/Q讯号上有DC Offset

那么该DC Offset会跟LO一同升频产生载波泄漏

如果讯号是宽带讯号 那么你会看到这情况

因为Data是基频 频率几近于DC Offset

所以跟LO升频后其LO Leakage几乎跟信号频率一样

而载波泄漏 会影响哪些性能呢?

Inner Loop power control

EVM

OOS (EDGE)

Inband Emission

LO Leakage

上图是Gain Setting与输出功率的关系图,

可看出当输出功率小于-30 dBm时,其Carrier Leakage的振幅,已经比讯号还大了,

这表示输出功率最小只能打到-30 dBm,

但WCDMA的Inner Loop Power Control(ILPC),

其Step E跟Step F,动态范围是 -50 dBm 24 dBm,

换言之, Carrier Leakage会缩减其动态范围, 使其ILPCFail

另外 如下图,由前述已知,

当输出功率处于Low Power Mode时,

其Carrier Leakage的能量,会比主讯号还大,这导致SNR变差。

而EVM与SNR成反比

因此倘若有LO Leakage的存在,

很可能输出功率越小,其EVM会越差:

或是以星座图解释DC Offset会使其星座图整个位移

这当然使EVM变差

所以EDGE里头 有一项origin offset suppression(OOS)

就是在量载波泄漏的程度多寡

而在LTE的Inband Emission规范中

也包含了载波泄漏

当然针对载波泄漏

LTE也有个别的规范

由前述已知 有载波泄漏时

其信号振幅越小 危害越大

甚至当信号振幅低到某个程度时其载波泄漏还可能比信号振幅更大

所以Spec中不同的信号功率 就有不同的Spec

信号功率越小 规范越宽松

若I/Q讯号上完全没有DC Offset

理论上是不会有载波泄漏

由下图也看到当I/Q讯号的DC Offset都为零时

其载波泄漏是最少的

但实际上不可能完全没有多多少少一定都会有

所以必须要靠校正来抑制

由上图可知 校正完之后改善了26dB

或许有人问那DC Block可不可行呢?

答案是不行

由上图可知 DC Block是高通滤波器

在Mixer之前 因为Data跟DC Offset都是低频讯号

所以DC Block会两者皆砍 我们当然不希望伤到Data

而Mixer之后信号跟载波泄漏

都升频为高频 其DC Block也挡不住

那除了校正外 我们还有其他方式抑制吗?

有!! 答案就是你的I/Q讯号Layout

因为I/Q讯号多半采差分形式

换言之倘若I/Q讯号上有等量的DC Offset

原则上最后会互相抵消

但倘若I/Q讯号不等长

那么DC Offset就无法互相抵消

自然就会有载波泄漏的问题

所以Layout时 特别要注意I/Q讯号的等长

还有一点用不到的I/QPin脚不要乱接地

例如Qualcomm的MDM9X35

因为I/Q讯号的Pin在Chip中其实都有相关联

如果你把用不到的I/Q Pin脚接地那么GND上的直流讯号

可能会流入IC内部 然后乱窜到实际的I/Q讯号上

以至于产生载波泄漏

其他详情可参照

在此就不赘述

不错啊,资深工程师多分享资料

楼上解释的相当霸气

criterion资深工程师的帖子上的图片不能显示,是咋回事

资深工程师都要出来多交流探讨

图片看不了,能否重新上传一下哈?谢谢!

非常感谢详细的回复,话说图片怎么没有显示?能共享资料吗?

图片都挂啦 修复一下呗

可参照这则帖子

看了好多遍但是有一句话比较难理解 混频器线性度不够产生DC offset,不明白这个DC offset到底是模数转换产生的还是IQ混频之后产生的就是对于DC offset不太理解能普及一下不

申明:网友回复良莠不齐,仅供参考。

上一篇:谁有sky77643 这个pa的loadpull

下一篇:MT6169 modem配置完成通路OK,但是插入sim卡 就会不断提示 modem reset