- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3长度控制

录入:edatop.com 点击:

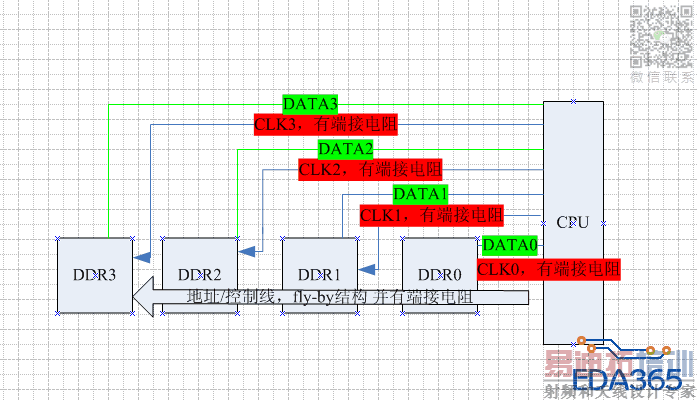

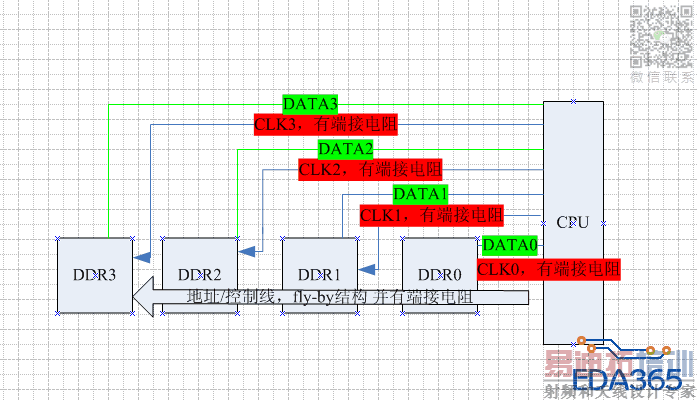

现在手上有一方案 用4片DDR3的架构,地址/控制线用的是fly-by的结构,但是MCU出了4组时钟线分别给到4个DDR,问题来了,是每组时钟和其对应的数据线做等长,还是时钟线和地址/控制线做等长?

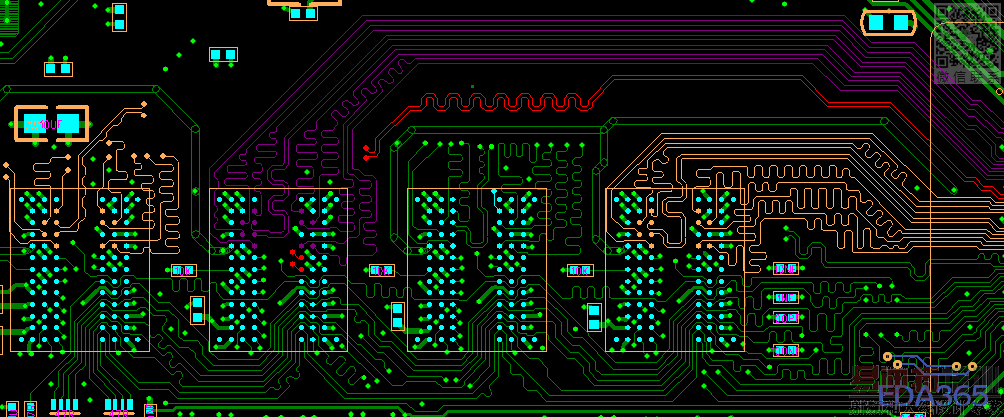

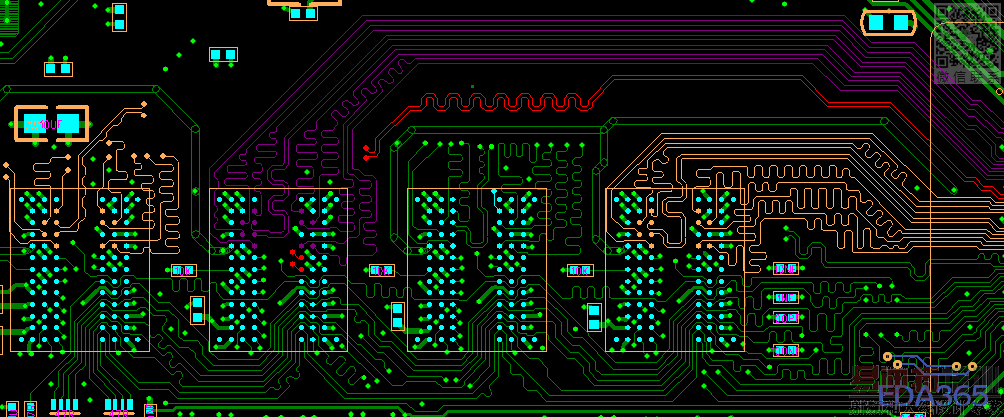

图1是结构示意图,图2 是pcb文件截图,其中以DDR2为例,红色先是其时钟线,紫色线是数据线,下方的走线是地址/控制线。

图1是结构示意图,图2 是pcb文件截图,其中以DDR2为例,红色先是其时钟线,紫色线是数据线,下方的走线是地址/控制线。

我在想布局为什么是这样的为什么不把ddr的布局整体旋转90度,这个估计是时钟参考数据吧 以前看到海思的一些芯片要求时钟和数据等长具体看看你的datasheet呗 那上面要求怎么搞就怎么搞呗

每组时钟和其对应的数据线做等长

8bit数据线与对应的dm和dqs等长。地址线与控制线等长。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PADS9.5 BGA无法扇出

下一篇:PCB图导出的元件坐标问题

射频和天线工程师培训课程详情>>