- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

USB/DVI/HDMI阻抗控制要求<供学习交流>

录入:edatop.com 点击:

1,USB pair to be routed as 90 ohms differential

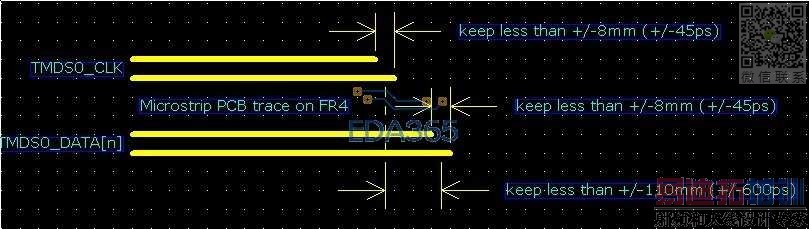

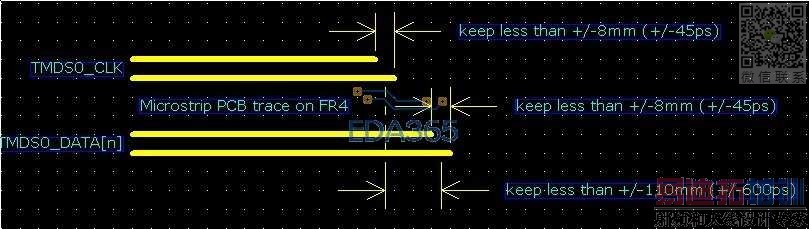

2,DVI TMDS pairs to be routed to 100ohms differential impedance

For the best design: length of length of TMDS0_DATA[n] = TMDS0_CLK

Figures are for 100% margin with 162MHz pixel clock

3,HDMI TMDS pairs to be routed to 100ohms differential impedance

For the best design: length of length of TMDS1_DATA[n] = TMDS1_CLK

Figures are for 100% margin with 270MHz pixel clock

2,DVI TMDS pairs to be routed to 100ohms differential impedance

For the best design: length of length of TMDS0_DATA[n] = TMDS0_CLK

Figures are for 100% margin with 162MHz pixel clock

3,HDMI TMDS pairs to be routed to 100ohms differential impedance

For the best design: length of length of TMDS1_DATA[n] = TMDS1_CLK

Figures are for 100% margin with 270MHz pixel clock

USB/DVI/HDMI阻抗控制要求

多谢分享。

好东西,谢谢楼主无私奉献!

收藏了,谢谢共享

收藏了,谢谢共享

MARK。

虽然看不懂,但还是要顶

非常好的东西,谢谢

感谢楼主

没有说清楚是在什么条件下的。

板厚多少?双?4?

可以参考,不过楼主能将应用条件说的再清楚点就更好了

学习一下

要是把几种接口的阻抗控制的公差也加上就更好啦。

鼠标瞎点了一下,不好意思

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PADS颜色传递使用方法

下一篇:有用DxDesigner 设计原理图的吗?

射频和天线工程师培训课程详情>>