- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基带处理器SP2704设计应用

SP2704媒体与基带处理器是LSI第三代基于StarCore DSP的多核DSP和RISC CPU平台。该款最新推出的处理器旨在满足下一代无线、有线以及企业基础设施等各种应用对高通道密度、优化成本和低功耗的要求。

这种异构计算平台专门针对低功耗和高密度应用进行了精心优化,能够为语音和视频应用提供非常高的通道密度。

StarPro 2704采用21mm×21mm的0.8mm球栅封装,配套提供LSI媒体处理套件,一款专门针对高密度、多通道应用而精心优化的综合软件库。该软件库包含众多组件,其中涵盖无线和有线音频编解码器、视频编解码器、回声抵消器与其他音质增强(VQE)模块、IP分组处理以及灵活高效的媒体处理引擎。

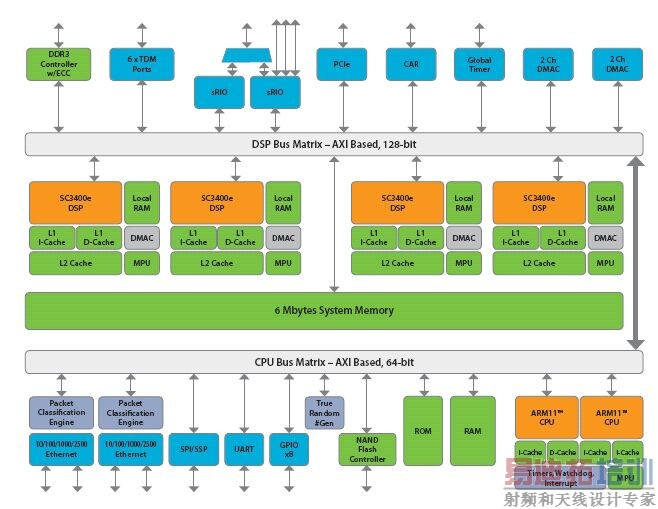

图1:SP2704媒体和基带处理器结构图。

基于ARM11 MP处理器的分组处理子系统可执行IP分组处理和路由,从而提供众多系统控制计划选项。DDR3存储器控制器拥有大容量的共享系统内存,可为外部存储器提供全面的支持。稳定可靠的外设集包括PCI Express、串行快速I/O(sRIO)、TDM和以太网接口等。通过基于多层ARM AXI主机总线的高性能总线矩阵可将DSP子系统、ARM子系统、系统存储器和I/O连接在一起。该总线矩阵是一个高效率的纵横制交换系统(crossbar switch),可提供144GB/s以上的总吞吐量。

该产品的其他特性包括:具有4个频率为750MHz的StarCore SC3400e DSP子系统,以及频率为375MHz的双核 ARM11 MP RISC 处理器。超高带宽 DSP总线矩阵可用作媒体处理功能模块的系统互连。硬件支持线速(wire-line speed)IP/UDP或者专有报头处理(验证和分类)。包含6MB共享系统存储器,带有错误检测和纠正功能。除ARM内核存储器之外,所有存储器上的纠错编码(ECC)功能都支持奇偶检验。具有两个10/100/1000/2500Mb/s以太网MAC,TDM处理模块通过6个串行端口进行TDM 流量的多路复用和解多路复用。

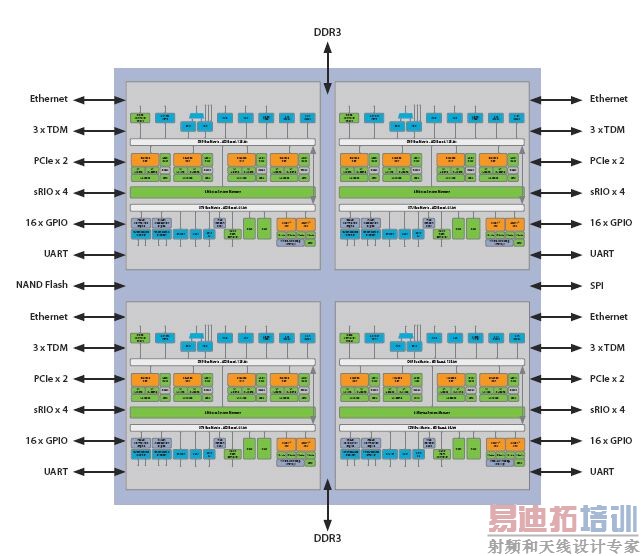

图2:SP2704媒体与基带处理器结构图。

采用两个2通道DMAC在存储器和外设之间进行高效率的数据传输。通过协处理器连接端口可以直接高速接入其它的SP2704器件或协处理器,也可用作主机接口端口。通过32位DDR3外部存储器接口可访问DMA控制器和处理器。2个符合IEEE1149.1标准的JTAG端口可实现PPB和DSS子系统的片上仿真。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...