- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP的通用语音编译码器设计与实现

摘要:实现了一种基于DSP的通用语音编译码器实验平台。在该平台上通过软件重构可以实现常用语音信号的编译码。详细介绍了应用DSP实现通用语音编译码中的关键技术,包括硬件平台设计、软件结构和接口扩展等。由于硬件和软件采用模块和结构化设计,通过开放的模块接口和子程序使得该设计具有扩展和升级容易、学生参与度高等优点。最后通过实际测试验证了设计的正确性。

关键词:语音信号处理;DSP;编码器;解码器;实验系统

0 引言

语音信号处理在通信系统中占有重要地位,也是通信工程专业的重要课程。由于课程内容比较抽象,如果只是停留在理论教学,会使学生不易理解并且感到枯燥乏味,同时也不容易体现它的实现原理以及在实际通信系统的位置和作用。语音编译码器的实现主要有三种方法:专用芯片、基于DSP和混合方法。其中,DSP5000系列以其内含硬件乘法器、硬件加法器和FFT运算器特别适合用于语音信号处理。文献提出一种基于DSP的多制式语音编解码器,文献给出一种可变速率的通用语音编解码实现技术,但都不适合实验教学。本文在文献的基础上,结合实验教学特点设计一种语音编译码器实验平台,其设计思想是采用通用的DSP,CPLD,控制器和PC机将语音信号处理过程在硬件、软件、接口和PC机管理几个方面实现模块化和开放接口设计。通过PC机或控制器,可以设置编码方式、调用不同的子程序实现不同的编码算法,同时也设置了计算机数据接口来实现编解码器的通用性,方便直观地了解语音信号的处理过程,易于不同层次、不同目的的学生参与,具有方便实现设计性、系统性、综合性和创新性实验等优点。该平台可以实现G.711,G.721,G.729和△M四种符合国际标准的编解码。为了观察信号的处理过程,在硬件电路的关键点都设置有测试点;其次,在软件设计上也尽量将程序分解成子程序由主程序调用,如初始化子程序、命令解

析子程序、信号采集与输出子程序、编译码子程序、数据接收与发送子程序等。每个子程序的人口都有相应的函数名、要传递的参数和返回的结果,这样便于学生参与各个算法子程序的设计。文中给出了详细的硬件电路设计和软件流程图,最后对实验平台进行了测试,结果正确且工作稳定可靠。

1 系统结构与硬件电路设计

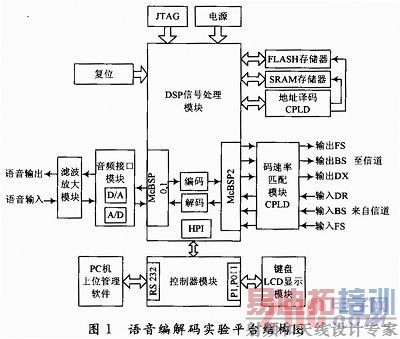

在硬件设计上根据功能分了6个模块,包括滤波器与放大模块、A/D与D/A转换器模块、DSP处理器模块、FPGA与数据接口模块、MCU控制器与PC机接口模块、键盘/显示器模块。为了防止干扰和方便学生观察信号,各模块之间的控制线通过通用底板相连,而信号通过各个模块的信号线相连。系统结构如图1所示。

图1中,抗混叠滤波器采用二阶有源低通滤波器;音频接口芯片选择TI公司性价比较高的A/D转换芯片TLV320AIC23,它可以在8~96 kHz的采样频率范围内提供16 b,20 b,24 b和32 b的采样数据,其DSP Mode是TI公司特有的与DSP连接模式,使音频接口设计非常简单,如对于PCM编码则根据AIC23的数据手册只需在其时钟输入端MCLK引脚外接一个12.288 MHz的有源晶振,配置AIC23的采样率控制寄存器的SR3~SR0= 0011,即可得到AIC23的A/D和D/A的采样率为8 kHz;DSP选择TI公司的TMS320VC5416,它采用增强的多总线和优化的CPU设计结构,内含三个多通道缓冲串口McBSP和8/16 b的增强型HPI口,不但可以满足语音编译码算法处理的需求,也方便实现主机访问;SRAM和FLASH分别采用常用的芯片CY7C1041CV33和SST39VF400(两者存储空间均为256K×16 b),外扩存储器的控制时序通过CPLD(EPM3128ATC100)实现;控制器采用AT89C52,它通过DSP的HPI口与DSP相连,其优点是可以通过DSP内部的双口RAM访问DSP内部的各种资源,而不会影响DSP的运行。同时,控制器扩展了键盘/显示和RS 232接口(预留了USB接口),不但方便用户使用,也实现了上位机软件与编译码器的通信。

系统工作原理如下:首先来自用户的语音信号先经过抗混叠滤波器模块完成信号的滤波和放大,然后送A/D、D/A模块将模拟语音信号转换成相应标准速率(如8 kHz)和采样精度(如16 b)的数字信号,数字化的语音信号通过多通道缓冲串口McBSP0送给DSP信号处理板,信号处理板将语音数据信号送到DSP内部缓冲区,在缓冲区内按用户选择的方法调用编码算法编成特定码率的码流,再将得到的标准数字码流送数据接口模块输出;另一方面,来自数据接口的码流送数据处理模块,数据处理模块由其多通道缓冲串口McBSP2接收至DSP的内部接收缓冲区,然后由DSP对其进行解码处理,解码后的数字化语音通过多通道缓冲串口McBSP0传送给D/A转换器模块转换成模拟语音信号后送信号滤波和放大模块,从而实现语音信号的采集、编码、发送和接收、解码等功能。

[p]

2 软件设计

软件设计包括DSP程序、控制器程序、CPLD程序和上位机程序四部分。DSP程序根据命令完成语音信号和计算机数据的处理等;控制器程序完成本地对编译码器的管理,并负责DSP与PC之间的通信;CPLD程序除完成系统需要的组合、时序工作外,还要提供与调制/解调器的数据接口;上位机程序完成对语音编译码器的管理。下面介绍部分程序的设计原理。

2.1 DSP程序设计

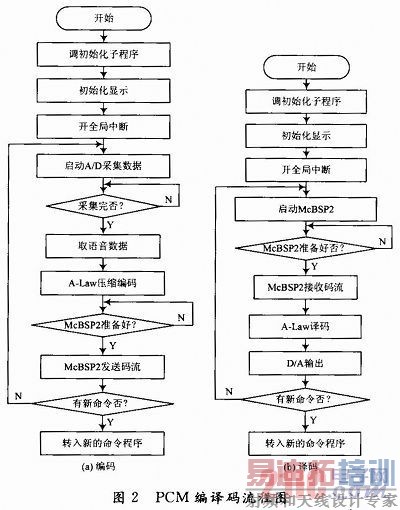

DSP程序主要包括主程序、命令解析子程序、模拟信号采集与输出子程序、编译码子程序、数据信号接收与发送子程序等。DSP完成G.711规范的A-Law编译码程序流程图如图2所示。

在DSP响应控制器程序中设置一个控制标志位CON_SEL,并分配在DSP数据空间内的0x1fffH地址,控制器根据用户从键盘输入的命令(或来自PC机的命令)向此地址写入相应的控制标志,DSP的底层程序响应该控制标志位完成相应的工作(MIC语音处理、线路语音处理和数据通信)。DSP响应控制器程序流程图如图3所示。从流程图中可以看到,对于语音处理,程序先打开中断。当A/D采集完语音数据后,即进入中断服务程序,在中断服务程序中关闭全局中断,并设置数据是否满的标志位为有效状态。主程序查询该标志位,如果有效则调语音处理子程序进行处理,处理完调用通信程序输出;而对于数据通信的处理过程是,DSP首先在内部开辟一个数据缓冲区,并打开HPI中断和全局中断,然后DSP主程序进入数据处理程序,这时接收来自单片机(或PC机)的数据通过数据口传输出去,传送完后可通过HINT去中断控制器,通知主机传送下一个数据。

[p]

2.2 控制器程序设计

控制器工作有两个状态,即本地控制工作状态和通信传输工作状态。本地控制状态就是实现对编译码器的控制与管理,而通信工作状态仅仅完成DSP与PC机之间的信息传输,这里只说明DSP、控制器和PC机之间的程序设计。由于DSP的HINT引脚和单片机的INT0引脚相连接,HINT中断有效触发的是单片机的INT0中断,所以PC机的上位机软件要响应DSP的中断只能在控制器与PC机的控制协议中完成,DSP在发送完成一个数据后无法采用中断的方式告诉上位机。为解决这个问题,上位机采用查询的方式,即在控制器中设置一个标志位send_end,初始化为0,当DSP发送完一个字节数据后置该标志位为1,上位机每发送完一个数据,通过控制器触发一次DSPINT中断,并读回send_end的值判断,若为1则传送下一个字节,否则等待控制器将当前数据发送完成。

2.3 上位机软件设计

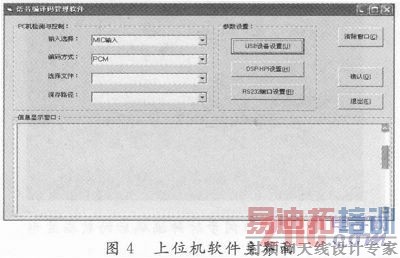

上位机软件采用学生容易掌握的VB语言实现,其主界面如图4所示。

主界面主要完成系统初始化,并显示系统需要检测和控制的内容。初始化正常后,上位机程序即可通过控制器向DSP的指令地址发送控制命令,DSP查询此地址的命令字,并根据命令字进入相应的服务程序(MIC语音、线路语音或数据通信。DSP在初始化中默认的是MIC语音处理),如果要进行线路语音处理则在控制界面上选择“线路输入语音”控制命令,这时控制子界面将用户选择的命令通过控制器送DSP,DSP查询到并判断是线路输入语音命令后即执行线路输入语音子程序,这时如果将数据输出端口与数据输入端口、对应的同步信号连接好的话,从耳机可听到经过语音编码和译码后的电脑播放的音乐,从听到的音乐比较编译码后的语音质量。如果在命令控制界面选择“计算机数据通信”控制命令,即可进行计算机数据通信实验。

3 实际测试

3.1 语音信号编译码测试

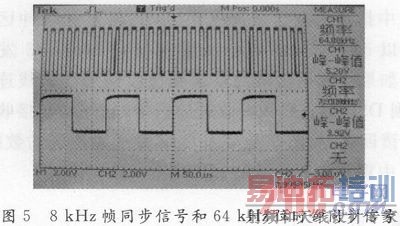

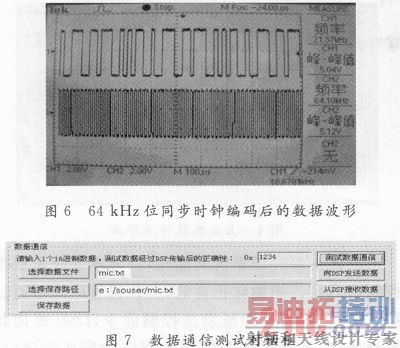

首先将PC机的线路输出用信号线连接到编译码器的LINE输入,启动编译码实验系统,然后由PC机播放MP3音乐,测试得到的8 kHz帧同步和64 kHz位同步时钟的波形如图5所示。

图6是在64 kHz位同步时钟情况下编码后的音乐数据波形,在译码器输出端用耳机可以听到MOS分在4 dB以上的音乐。 [p]

3.2 数据传输测试

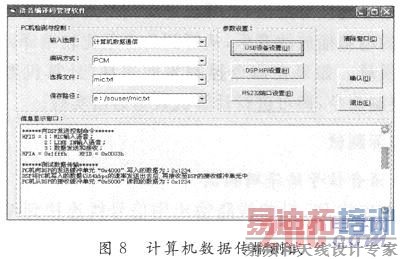

首先在上位机软件的控制界面中选择计算机数据通信命令,在弹出的数据通信对话框中输入测试数据1234,如图7所示。

DSP结束当前语音通信过程后即进入数据通信子程序,这时可以从主界面的编辑对话框中输入要传输的数据(也可以选择PC机中的文件),点击“确认”按钮,编译码实验系统即可完成数据通信,图8给出以64 Kb/s的速率传输的数据,同时PC机从DSP端读回所发送的数据,可以看到数据完全正确。

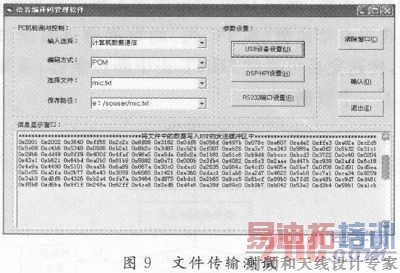

对于传输文件,先选择*.txt数据文件,然后点击“确认”,则*.txt文件中的数据将通过控制器发送到DSP中指定的发送缓冲区中,DSP将发送缓冲区中的数据以64 Kb/s的速率从数字接口McBSP2发送出去。如果将数据接口的发送和接收端用测试线连接起来,则DSP接收回到接收缓冲区中,软件从其接收缓冲区中读回数据,图9是写入DSP发送缓冲区的数据,在CCS中观察与所发送的数据完全一致。

4 结语

本文设计并实现了一种基于DSP的通用语音编译码器实验平台。该平台硬件采用模块化设计,软件采用结构化设计,非常方便学生从不同层面参与实验,也非常适合以团队的方式完成实验项目,将比较复杂、内容比较多的实验项目分解成易于实现的小模块,同时模块和结构化的设计思想非常容易实现硬件和软件的扩展和升级,可以从硬件和软件等多方面培养学生的设计、综合以及创新等能力。从仿真和测试结果可以看到设计的正确性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:DLP拼接屏的技术缺陷

下一篇:如何改善LED散热性能