- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA实现多处理器解决方案

寻求高性能处理能力的嵌入式设计人员在成本、性能、功耗上,不可避免的面临类似“百慕大三角”的困境,无法同时实现三者的最佳组合,而只能达到其中的两个目标。定制ASIC设计适用于那些能够负担得起时间、费用和风险的少数人,但是由于器件尺寸持续减小,而ASIC设计成本不断攀升,完全定制设计受成本限制,能够应用的领域越来越少。

具有多个软核处理器的FPGA嵌入式系统为嵌入式设计人员提供了强大的多种功能选项,通过定制功能配置性能最佳的片内系统不再是ASIC设计人员的专利。现在,开发人员能够赶在产品进入最终测试之前,对其嵌入式系统性能特性进行修改。开发人员还可以延长产品生命周期,将产品迅速推向市场,通过互联网对硬件和软件功能进行远端升级。

尽管术语“多处理器”会使人联想起学术文章中的“并行处理”一词,实际商用的单器件多CPU则简单明了得多。开始进行一个新设计时,开发人员必须考虑一定的性能标准。多个软核处理器之间的任务划分具有很大的设计灵活性,实现了由于规范或竞争产品变化而进行的最后一刻设计更改,同时能够与这些性能标准保持同步。

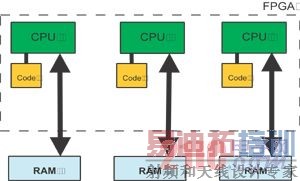

多软核处理器可作为一种分而治之的策略来提高系统整体性能,或者卸载现有处理器任务。设计人员通常采用400MHz~800MHz的分立处理器实现简单和复杂的多种器件任务。采用多个软核处理器,可根据时间和功耗要求,通过任务划分,更高效的发挥处理能力,提供同样甚至更好的整体性能。

单个FPGA中能够实现的软核处理器数量仅受器件资源的限制(如,逻辑和存储器资源)。例如,高密度FPGA可以含有几百个软核处理器,并且可以采用不同类型的软核处理器,如16位或32位、性能最佳、逻辑面积最佳处理器等。

根据任务不同,编码算法由多个处理器进行分担。专用处理器承担对时间要求严的任务,而要求不高的任务则由一个或多个其他CPU分担。这种灵活性实现了任务的逻辑分组,能够以较低的时钟频率和功耗实现较高的性能。

FPGA中的嵌入式处理器

ASIC设计人员对构建定制器件进行了多年的研究,因此,我们不难想象定制器件应包含一组合适的外设、存储器接口和处理功能。直到1990年后期,FPGA才能够提供足够的片内存储器、可编程逻辑等基本性能资源来实现经济可行的定制FPGA嵌入式处理器器件。现在,可直接使用专为FPGA设计的嵌入式IP功能(包括CPU、信号处理引擎、外设和标准通信接口等),与传统分立的嵌入式器件相比,它具有成本和性能的双重优势。

从本质上看,设计人员对问题的划分与在印刷电路板上构建一个多处理器系统相类似。每一部分分配不同的任务,一个处理器进行一般的系统管理(风扇监控、人机接口、系统控制台等),其他的则处理通信、信号处理、统计收集等系统任务。

多处理器方案将分立的处理器功能由电路板移到FPGA内部,从而降低了器件整体成本,也同时减小了电路板尺寸。这种方案需要较少的互连,减少了处理器之间的信号布线。更多的低级处理器运行在更低的时钟频率上,减少了电路板层数。

该方法还可以降低软件设计成本,减少80%由于耗时的代码编写而造成的系统整体设计时间代价。如果任务能够划分给多个处理器,那么工程师就能够直接迅速的进行源代码编写、调试和维护。产品成熟时,由于可以方便的对源代码进行分析,因此代码维护比较轻松。

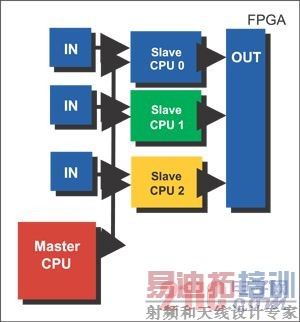

多通道应用

多通道应用采用单芯片多处理器来满足系统吞吐量要求,每个处理器专用于处理全部通道吞吐量的不同部分,它们运行完全相同的源代码,也可以根据系统要求灵活的改变算法。在有些情况下,加入主处理器来处理一般的系统管理任务,如系统初始化、统计收集和错误处理等。

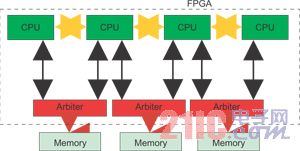

串行链接的处理器

系统结构将一个链上的几个处理器组合对待为更复杂流水线上的一级。每个CPU负责全部处理任务的一部分,共享数据存储器(片外采用仲裁或专用存储器接口,片内采用双端口存储器),将结果由一级的输出传向下一级的输入。

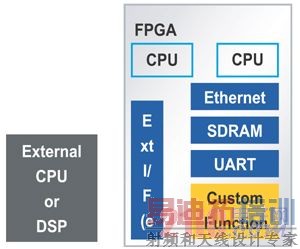

处理器协同芯片

不管CPU是否在FPGA内部,与FPGA连接的分立处理器和DSP芯片也可以使用硬件加速、外设扩展和接口桥接等。现在,可直接使用芯片间接口IP,实现对FPGA内部外设、加速逻辑和I/O接口的外部访问。

确定处理器性能

在应用软件还没有明确时,很难确定嵌入式系统的处理器性能。业界标准会有一些帮助,但是在软件完成之前,一切都具有不确定性。这使得设计人员非常谨慎,担心低估性能要求,而选择高于所需性能(价格也高)要求的器件。如果设计人员能够准确的预测所需性能,那么选择处理器将变得非常简单。这种预测要考虑对时间要求严的任务以及一个或多个低级任务所产生的负载对性能的要求。

基于FPGA的嵌入式系统提供灵活的性能,支持最后一刻更改,根据客户要求来提升系统性能。将

含有大量计算的算法转换为FPGA中的逻辑后,其运行速度比微处理器或数字信号处理器实现的相同软件算法快出几个数量级。更重要的是,硬件资源可提供给对性能要求高的算法,从而降低了对高性能CPU的需求,并降低了时钟频率和功耗,简化了电路板设计。 [p]

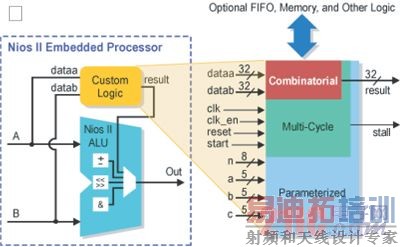

扩展指令集

多个处理器IP供应商能够扩展处理器指令集,以包含在硬件中实施的专用算法,并在FPGA中实现。采用处理器常用的加载/存储操作,数据可馈入到定制逻辑模块中,成为处理器算法逻辑单元(ALU)的一部分。在有些情况下,定制指令能够支持多周期操作,实现对FIFO和存储器缓冲等其他系统资源的访问。定制指令的典型应用包括位处理、复杂的数值和逻辑运算等。

依靠处理器加载和存储操作,定制指令与采用通用ALU资源运行同样算法相比,具有明显的性能优势。例如,64kbyte的循环冗余校验(CRC)以定制指令运行时,运行速度比软件快出27倍1。不同的应用具有不同的性能结果,但是总体上比单独采用软件快得多。

处理器IP供应商不同,开发人员如何使用定制指令也各不相同。例如,在加入定制指令时,有的必须生成一个新的编译器。然后,根据应用标准,这种定制编译器导出定制指令调用。更简单的方法是由用户在其C源代码中作为子程序来直接调用指令。由于软件设计人员能够更清楚的掌握何时使用定制指令,因此这种方法更自然一些。

提升系统性能的多种方法

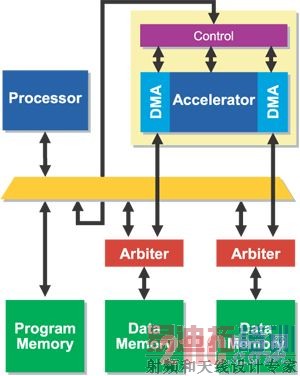

其他提升系统整体性能的方法包括利用硬件加速(也称为协处理器)、处理器协同芯片以及定制片内系统等。

与定制指令不同,硬件加速器作为独立的逻辑模块直接从嵌入式CPU获取指令,不需要CPU干预,处理全部数据缓冲。一个简单的模块框图包括带有两个1/2 DMA通道的处理模块(一个读取输入数据,另一个存储结果)以及一个控制接口,用于CPU建立、启动、停止以及工作中对各单元的轮询等。这种体系结构非常适合于对大块数据的处理,此时,CPU加载数据并存储结果成为性能瓶颈。

硬件加速器由于其固有的自治特性,能够比软件运行任务提高几个数量级的性能增益,因此加速功能通常在硬件中设计实现。

不管CPU是否在FPGA内部,与FPGA连接的分立处理器和DSP协同芯片都可以使用硬件加速、扩展外设以及接口桥接等。现在,可直接使用芯片间接口IP,实现对FPGA内部外设、加速逻辑和I/O接口的外部访问。

总结

在FPGA中采用多个软核处理器,根据时间和功耗要求划分任务,可高效使用处理能力,与分立处理器相比,具有相同甚至更高的整体性能。多个软核处理器还可以用作分而治之的策略,来提升系统整体性能或者卸载现有处理器任务,这种策略仅受目标FPGA逻辑和存储器资源的限制。

一类新的硬件开发工具、知识产权内核以及FPGA体系实现了这些技术的主流应用。在嵌入式领域,由于这些技术的成功,主要FPGA供应商进一步加大了开发和投入。在您下一个设计中,应考虑如何应用这些技术。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:SPCE061A实现的电话防盗报警器

下一篇:μPD780208单片机的功能及应用