- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CY7C68013与FPGA接口的Verilog HDL实现

0 引 言

USB(通用串行总线)是英特尔、微软、IBM、康柏等公司1994年联合制定的一种通用串行总线规范,它解决了与网络通信问题,而且端口扩展性能好、容易使用。最新的USB2.0支持3种速率:低速1.5 Mbit/s,全速12 Mbit/s,高速480 Mbit/s。这3种速率可以满足目前大部分外设接口的需要。

本文介绍了目前使用较多的USB2.0控制器CY7C68013芯片与FPGA(现场可编程门阵列)芯片接口的Verilog HDL(硬件描述语言)实现。本系统可扩展,完全可用于其他高速数据采集系统中。

1 系统构成

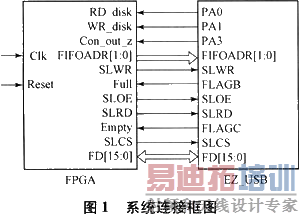

本系统主要是由FPGA和USB2.0控制器CY7C268013组成,系统框图及其信号连接关系如图1所示。可以根据实际系统的需要,用FPGA实现预定功能,如数据采集卡、控制硬盘读写等。

1.1 控制器CY7C68013

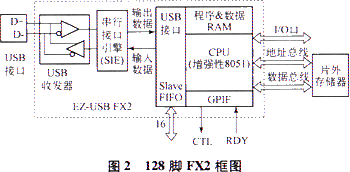

Cypress公司的EZ-USB FX 2是第一个包含USB2.0的集成微控制器,它内部集成了1个增强型的8051、1个智能USB串行接口引擎、1个USB数据收发器、3个8位I/O口、16位地址线、8.5 kB RAM和4 kBFIFO等。增强性8051内核完全与标准8051兼容,而性能可达到标准8051的3倍以上。其框图如图2所示。

1.1.1 CY7C68013结构特点

EZ-USB FX2提供了一种独持架构,使USB接口和应用环境直接共享FIFO,而微控制器可不参与数据传输,但允许以FIFO或RAM的方式访问这些共享FIFO,这种被称之为"量子FIFO"的处理架构,较好地解决了USB高速模式的带宽问题。

FX2芯片在数据传输时主要利用了4 kB的FIFO,分为7个端点:EPOIN&OUT、EP1IN、EP1OUT、EP2、EP4、EP6和EP8。其中EPO、EPlIN和EP1OUT是3个64 B的缓存,只能被固件访问,EP0是一个默认的数据输入输出端口缓存;EP1IN和EP1OUT是单独的64 B缓存,呵以配置这些端点为块传输、中断传输或同步传输;端点2、4、6、8是大容量高带宽的数据传输端点,可以配置为各种带宽以满足实际需要,端点2、4是输出端点,端点6、8是输入端点。值得注意的是,端点4、8能配置为每帧512 B,而端点2、6却能配置为每帧512 B或1 024 B,并可配置为2、3、4级,这样EP2或EP6最大能配置为4 kB的缓存。

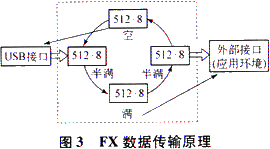

其在内部的传输控制是通过full(满)和empty(空)两个控制信号来完成的,当full为真时不能再写数据,当empty为真时不能再对FIFO进行读,其内部数据传输示意图如图3所示。

如图3所示,USB执行OUT传输,将EP2端点设成512 B四重FIFO。在USB端和外部接门端都并不知道有四重FIFO。USB端只要有1个FIFO为"半满",就可以继续发送数据。当操作的FIFO写"满"时,FX2自动将其转换到外部接口端,排队等候读取;并将USB接口队列中下一个为"空"的FIFO转移到USB接口上,供其继续写数据。外部接门端与此类似,只要有1个FIFO为"半满",就可以继续读取数据。当前操作的FIFO读"空"时,FX2自动将其转换到USB接口端,排队等候写入;并将外部接口队列中下一个为"满"的FIFO转移到外部接口上,供其继续读取。

1.1.2 Fx2接口方式

FX2有Slave FIFO和GPIF两种接口方式。

Slave FIFO是从机方式,即FX的CPU不直接参与USB数据处理,而是简单地把FX作为USB和外部数据处理逻辑(如ASIC、DSP和IDE(串行接口引擎)控制器)之间的通道,数据流并不经过CPU,而是通过FX的FIFO直接传输。FIFO通过外部主机控制,同时,FIFO提供所需的时序信号、握手信号(满、空等)和输出使能等。

可编程接口GPIF是主机方式,GPIF作为内部主机控制端点FIFO,其core是一个可编程状态机,可以生成多达6个控制输出信号和9个地址输出信号,能外接6个外部Ready输入信号和2个内部Ready输入信号。通过用户自定义的波形描述符来控制状态机,使用软件编程读写控制波形,几乎可以对任何8/16 hit接口的控制器、存储器和总线进行数据的主动读写,非常灵活。

2 接口的Verilog HDL编程实现

在本设计巾采用Slave FIFO从机方式实现FPGA对FX的控制,通过Verilog HDL编程实现。FPGA可以根据实际情况选定。我们在设计时选用Xilinx公司的Virtex-Ⅱ设备(XC2V10004FG456C)。

2.1 异步FIFO读数据

FX读数据也就是数据从FX传到FPGA的过程,其过程如下:

a)反复检测控制线状态,当读事件发生时,即控制线con_out_z=0和RD_disk=10时,转到 b;

b)分配FIFOADR[1:0]=00,这时FIFO指针会指向输出端点,表明使用端点EP2;

c)检查FIFO是否空,当empy=1时表示FIFO不空,转到状态d,否则保持在状态C;

d)赋值SLOE=0,使双向数据线FD在输出状态,采样FD数据线上的数据,并在SLRD的上升沿使FIFO指针门动加1,跳转到e;

e)假如有更多的数据需要读,转到状态b,否则转到状态a。

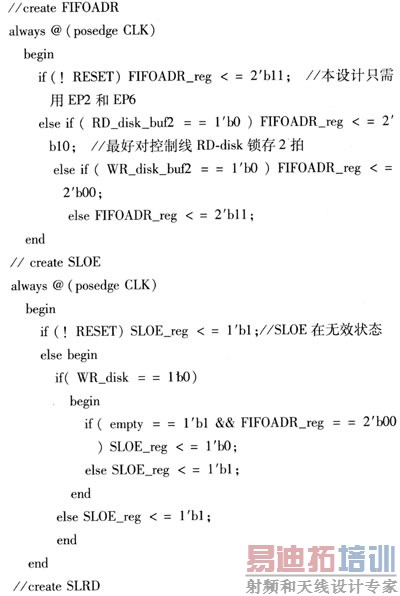

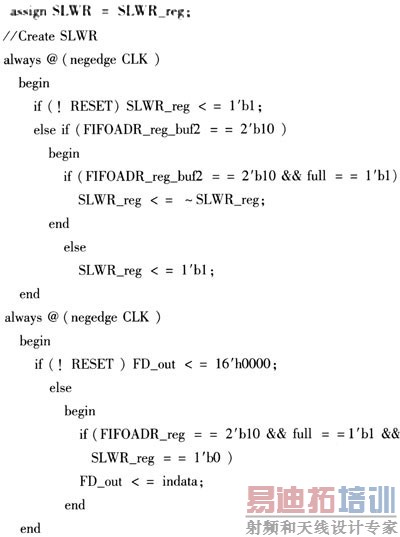

对读数据编程如下:

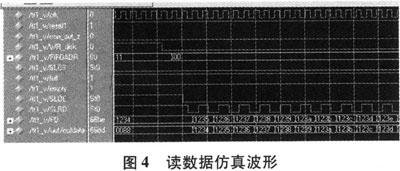

用Mentor软件Modelsim进行仿真验证,其仿真波形如图4所示。在此过程中,SLRD信号特别重要,在SLRD的下降沿把FlFO中的数据放到FD数据线上;在SLRD的上升沿把FIFO指针加1,并指向下一个单元。

2.2 异步FIFO写数据

向FIFO写数据是读数据的逆过程,也就是把FP-GA数据写入FX的FIFO,其编程过程如下:

a)查询控制信号线con_out_z和WR_disk,看是否有读事件发生,如果有,就转移到状态b,否则保持在状态a;

b)分配FIFOAFR[1:0]=10,FIFO指针指向输入端点,转向状态c;

c)检查FIFO的满标志是否为1,假如fuIl=1,表示FIFO不满,转到状态d,否则保持在状态c;

d)把外部数据indata放在FD上,同时把SLWR拉高,以使得FIFO指针自动加1,然后转到状态e;

e)假如有更多的数据要传输,转到状态b,否则转到状态a。

其程序与写FIFO数据时一样,只是在生成SLWR信号时,需要注意控制信号之间的保持延时时间约束,这可以通过仿真结果进行适当修改。

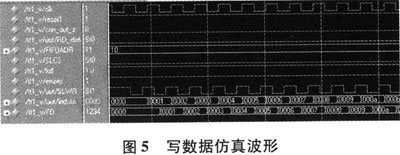

读数据信号仿真波形如图5所示。但必须注意的是,在SLWR的下降沿把indata数据线上的数据放到FD数据线上;在SLWR的上降沿把FD数据线上的数据放人FIFO,并同时使FIFO指针加1,指向下一个缓存单元。

3 结束语

现在USB2.O控制器CY7C68013已经应用到许多数据传输领域,由于此芯片灵活的接口和可编程特性简化了外部硬件的设计,提高了系统可靠性,也利于PCB(印制电路板)的制作与调试。本设计可扩展性好,因此可用于需要处理大容量的数据采集系统中。本设计已经用于对IDE硬盘的读写控制中,实现了对IDE硬盘的快速读写。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...