- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

MicroBlaze在 像高速双向USB传输中的应用

摘要:在空间飞行器的遥感过程中,测获的海量数据在实时压缩、硬盘存储的基础上,还要与PC机进行通信。为了解决数据压缩板在通用串行接口高速数据传输中双重角色(主机/外设)的矛盾,本文采用具有OTG功能的USB 芯片ISP1761实现了协议转换、主从自动切换控制以及上/下行高速数据传输。针对ISP1761支持微处理器接口的高速性能,采用Xilinx公司的Virtex4系列FPGA芯片,通过其内嵌的MicroBlaze软核处理器完成芯片初始化以及DMA数据传输控制,实现了对JPEG2000压缩后图像的45.8Mbps上/下行有效数据传输。

1.绪言

在空间飞行器的遥感测绘过程中,由于受到有限信道带宽的限制,数据的压缩处理显得 尤为重要。随着图像传感技术的进步以及对图像质量要求的提高,对不同设备中通用标准接 口之间的数据传输也有了更高的要求。通用串行接口(USB)的热插拔、高速特性使其成为各 个系统数据高速连接的通用标准。选择USB 接口进行数据传输的前提下,对各种设备的小 型化、低功耗要求,需要脱离体积较大的PC 机来实现系统的嵌入式操作。为了解决图像压 缩调试中压缩板传输数据的双重角色矛盾——直接硬盘存储中图像压缩板为主机(Host), 高速USB 硬盘为外设;电脑调试中PC 机为主机,图像压缩板为外设(Peripheral)。本文采 用具有USB OTG(On-the-Go)技术的协议芯片ISP1761 来完成同一端口的双重操作,并且 实现了自动切换。

2.OTG 技术及ISP1761 特性分析

USB OTG 在兼容所有USB2.0 特性的前提下,结合了对嵌入式应用的新特性,其中包 括低功耗、更小的USB 接头以及在同一个USB 端口上实现了双重角色(OTG)的功能—— 作为主机和外设的功能。OTG 适用于没有PC 机(主设备)的情况下,实现从设备相互之间 的对等连接。

USB2.0 协议本身支持高达480Mbps 的高速(high speed)数据传输,并且与USB1.1 规 范后向兼容,而后者仅支持全速(full speed)12Mbps 和低速(low speed)1.5Mbps。在具有 OTG 技术的USB 协议芯片之中,Philips 公司生产的芯片ISP1761 不但在同一接口具有了主 机/外设双重功能(OTG),而且实现主机/外设的高速传输(high speed 支持480Mbps)。

ISP1761采用低功耗设计,正常工作时Icc<100mA,便于嵌入式应用。

在接口形式上:ISP1761 是单片高速USB OTG 控制器,配备了一个OTG 接口和两个主 机控制器接口,OTG 接口可以通过控制线在主机/外设角色间随时转换,使得本系统可以随 时连接PC 机和USB 高速硬盘进行数据传输调试。

在数据传输上:集成PLL锁相环,可以获得稳定的传输采样;内部FIFO进行数据缓冲; 支持DMA传输方式,支持HNP (Host Negotiation Protocol主机通信协议)和SRP(Session Request Protocol)对话请求协议技术,采用请求/应答机制进行快速数据交换。

在控制方面:采用通用处理器接口,可以方便的连接到各种CPU单元。特别是支持RISC 处理器接口,能够和Xilinx FPGA软核MicroBlaze直接相连,实现高速控制。

3. MicroBlaze 系统结构及其ISP1761 连接方法

MicroBlaze嵌入式软核是一个被Xilinx公司优化过的可以嵌入在FPGA中的RISC处理器 软核,MicroBlaze采用的数据总线和指令总线是分开的,总线接口有LMB和IBM的OPB两种, 其中,LMB为有效的块RAM传输提供简单的同步协议,而OPB接口提供片上、片外设备和 外设存储器之间的连接,MicroBlaze还提供Xilinx CacheLink(XCL)的接口,XCL为Caches和 特定的外部存储器控制器提供一个快速的从设备方仲裁流接口,MicroBlaze也支持高达8个 快速单一连接端口(FSL), FSL提供一个快速的非仲裁流通信机制,而每一个又可分主接口和 从接口。

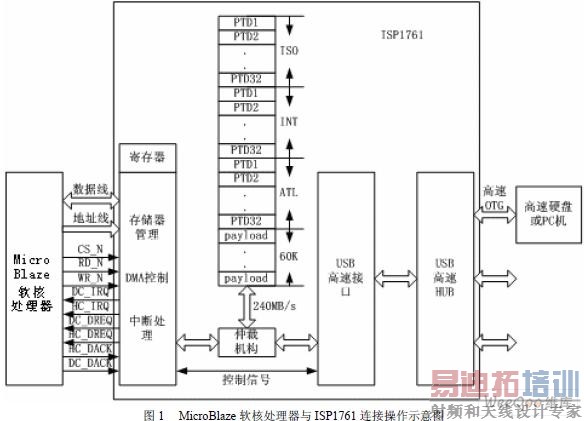

MicroBlaze 软核处理器与ISP1761 连接操作示意图如图1 所示。

内部可寻址的主机控制器缓冲存储器(即内部RAM)大小为63kB,包括传输描述和有效载 荷PTD(Philips Transfer Descriptor)和payload两部分,PTD区域和payload区域都被分成三个 部分,ISO(Isochronous)、INT(Interrupt)、ATL(Acknowledged Transfer List),可以进行 如图2所示的分区管理。无论是与MicroBlaze还是与USB硬盘进行数据传输都需要访问1761内部 RAM,即数据必须通过PIO模式或DMA模式传输到PTD区域和payload区域才能进行协议转换等操作,具体区域需要由ISP1761内部的仲裁机构来裁定。

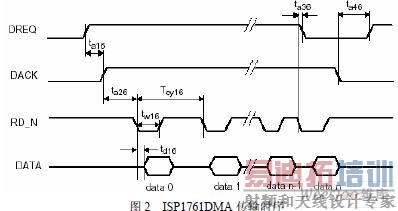

因为ISP1761的初始化主要是对内部寄存器赋值,因此采用PIO模式。通过CS_N、WR_N、 RD_N来访问寄存器和存储器。当USB接口进行高速数据传输时,则采用DMA方式。通过DACK、 WR_N、RD_N来访问。ISP1761的DMA传输长度支持1,4,8,16个字,在DMA传输开始的时 候,DREQ有效。DMA访问时序如图2所示.

4.调试系统硬件实现以及工作过程

4.1 调试系统硬件组成

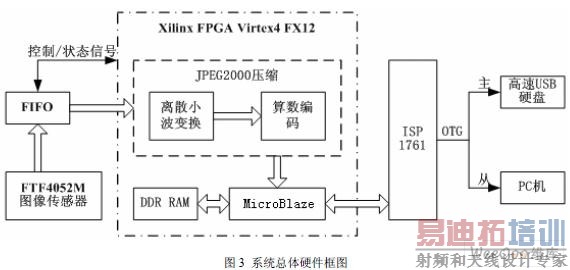

本系统所实现的是测绘图像数据压缩以及 USB 接口的数据传输。如图3 所示,由图像 传感器获取的图像数据经过FIFO 缓存后,经由FPGA 进行JPEG2000 标准下的图像压缩, 压缩程序由Verilog HDL 硬件描述语言实现,压缩后的数据流在MicroBlaze 软核处理器的控 制下,暂存到DDR RAM 中,进行连续相关图像比较及其处理,最后将图像数据存储到高 速USB 硬盘中。但在调试的过程中,需要对压缩算法进行验证和*估,即将需要存储到高 速USB 硬盘的数据流直接连接输入到PC 机中,在PC 机中进行数据显示、处理和识别等方 面的*估,因此调试中要频繁的将同一个USB OTG 高速接口在高速USB 硬盘和PC 机USB 接口中调换。

设计中 CCD 传感器采用2200 万像素(4008×5344)的超大分辨率全帧CCD 图像传感器 FTF4052M。FIFO 采用IDT 公司的IDT72V2113,容量为512K×9bit。FPGA 采用Xilinx 公 司的Virtex4 FX12,它集成PowerPC405 硬核处理器和MicroBlaze 软核处理器,可以通过IP 核方便的连接SRAM 和DDR SDRAM 进行数据暂存或高速缓冲存储,DDR RAM 采用 HYB25D256160BT,软核也可以针对ISP1761 的预留MicroBlaze 接口直接对其进行高速控 制,其中JPEG2000 压缩部分为自己编制已做成用户自定义IP 核,直接添加到MicroBlaze 软核处理器中。

4.2 MicroBlaze 软件配置流程

系统采用 ISE EDK(Embedded Development Kit)中的BaseSystem BuilderWizard 来快速构建基于MicroBlaze 软核处理系统。在XPS(Xilinx Platform. Studio)平台下进行硬核配置。 首先定义内部所用各种存储器(BRAM,DDR RAM)以及应用总线(LMB,OPB)和接口, 之后添加JPEG2000 的IP 核,对用户IP 核进行各种导入操作,包括总线形式选择、主从配 置、分配地址空间、添加端口信号、将端口信号连接到FPGA 管脚上,并且定义成外部管 脚。软件工程设计主要包括:软件工作环境设置,对设备驱动进行调整,添加应用软件,自 己编写的应用C 固件程序添加到软件工程之中,最后产生位流文件。

4.3 OTG 芯片控制流程

OTG 引脚可以分别连接到PC 机和高速USB 硬盘,而OTG 的主机/外设作用选择取决于 ISP1761 中的ID 引脚,引脚值由连接到USB mini-AB 插座上的插头类型决定。如果ID 为低 (mini-A 插头),为主机A-device。如果ID 为高(mini-B 插头),为外围设备B-device,这样 就实现了智能主从选择,方便随时改变硬件进行压缩调试。

ISP1761引脚VBUS开/关之间的时间(session)是交换数据过程。主机和外设都可以开始一 个数据传输过程,在一个传输过程里面主机的作用能够通过HNP在A、B设备中随时改变。如果 主机开始一个数据传输,通过使能电荷泵来有效VBUS。外设检测到VBUS有效后,通过使能DP线 上的上拉电阻来确定自己外设地位。主机检测到远程上拉电阻则也确定了自己的主机地位。主机 就可以和外设进行通信。结束通信则通过无效VBUS来实现。

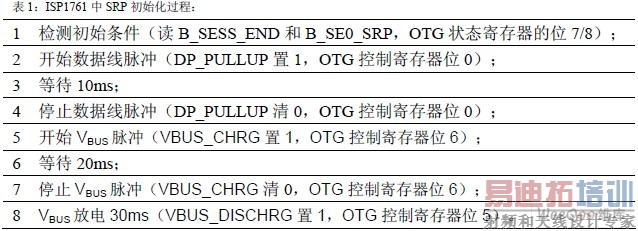

如果外设开始一个数据传输,必须通过数据线脉冲或者VBUS 脉冲来初始化SRP。当主机检 测到SRP 事件,则有效VBUS(只有主机才能有效VBUS),这时就确定了自己的地位。SRP 初 始化过程如表1 所示。主机对两件SRP 事件有反应:数据线脉冲或VBUS 脉冲。当用数据线脉 冲时,ISP1761 能够检测DP 脉冲。这意味着仅为外围设备必须通过DP 来初始化数据线脉冲。

当主机通过 OTG 描述符而检测到支持HNP 的外设时,主机就会通过使用SetFeature (b_hnp_enable)命令使能HNP hand-off,之后进入悬空状态。外设信号就会通过无效自己的 上拉电阻来获得主机地位。而主机则认可了自己的外设地位。此时,外设就作为主机来进行各种 通信,直到外设结束通信,两者又返回各自状态。HNP 是对话时用来在默认主机(A-device) 和默认外设(B-device)之间传输主机控制。如果B-device 想利用总线,就给A-device 给发送 断开信号。这样,A-device 就获得外设地位,B-device 则获得主机地位。

5.结束语

通过将压缩后的协议转换前图像、读出高速 USB 硬盘中的图像、连接到主机USB 接口 采集的图像三者对比后达到完全一致,验证了通过单片协议芯片ISP1761 实现了USB OTG 标准下的高速数据传输,实现了同一压缩板端口的上/下行数据调试。 CCD 传感器数据量 为100Mbps 的情况下,采用JPEG2000 标准对图像数据进行无损压缩,实测压缩率约为2.1: 1,因此通过USB 接口实现了约45.8Mbps 的上/下行(OTG)有效数据传输,远远超过USB 低速、全速的传输速度,实现了真正意义上的高速(high speed)数据传输。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...