- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种视频处理系统设计与实现

1 引言

在视频处理领域,由于处理的数据量大,算法复杂度高,使得处理的实时性成为难题。如果使用专门的视频算法器件,在保证实时性的同时却使系统的灵活性大大降低。tms320dm642是TI公司C6000系列DSP总最新的定点DSP,其核心是C6416型高性能数字信号处理器,具有极强的处理性能,高度的灵活性和可编程性,同时外围集成了非常完整的音频、视频和网络通信等设备及接口,特别适用于机器视觉、医学成像、网络视频监控、数字广播以及基于数字视频/图像处理的消费类电子产品等高速DSP应用领域。笔者针对市场客户的需求,设计并实现了一款以TVP5150为视频输入解码器,以PCM1801为音频输入采集电路,以TMS320DM642型DSP为核心处理器的多路视频采集兼压缩处理PCI板卡,并将其应用于构建高稳定性、高鲁棒性和多媒体数字监控系统,取得了较好的社会效益和经济效益。

2 系统设计方案

2.1 系统的硬件结构

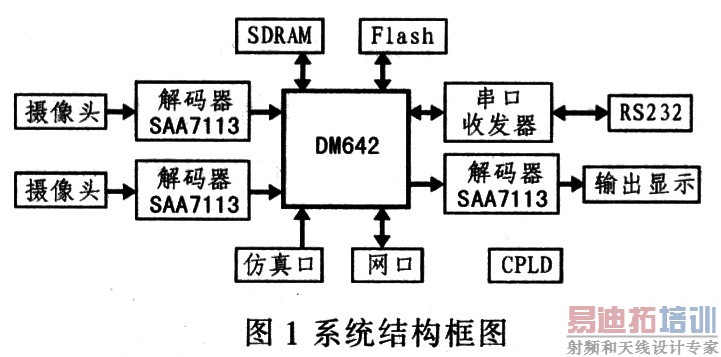

图1给出系统的结构框图。以DM642为核心,DM642的最高时钟频率为720MHz,最大处理能力为5760MIPS。DM642基于C64x内核,采用了增强型超长指令字结构,集成了8个独立的功能单元(6个32位的算术逻辑单元和2个32位的乘法单元)和64个32位的通用寄存器,在一个周期内可以完成4个16位的乘累加运算或者8个8位的乘累加运算。该芯片的片上外设也是相当的丰富,包括时钟高达133MB可与SDRAM、FLASH等外部存储芯片实现无缝链接的外围存储器接口(EMIF总线);三个可配置的视频接口,同时支持三路视频输入或者输出,非常适合数字图像和视频处理;一个10/100Mit/s的以太网接口;十六个通用输入输出口GPIO,以及I2C、PCI和HPI等众多协议接口。

2.2 系统电源设计

DSP(digital signal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。其工作原理是接收模拟信号,转换为0或1的数字信号。再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

DSP系统电源设计模块是关键,高精度的供电才能保证系统正常工作。系统采用5 V电源驱动2个MOSFET的DC—DC调整器(TPS54310)分别供给DSP的核心电压CVDD(1.4V)和外围电压DVDD(3.3 V)。在3.3 V和1.4 V电源之间连接肖特基二极管,保证DM642内核和外部端口同时供电。TI公司的TPS543lO的输出精度是1%,完全满足DSP工作要求。

2.3 视频输入与输出

DM642集成有3个视频(Video Port,VP)口,每个视频口是由20 bit数据线、2个时钟信号VPxCLK0(输入)和VPx-CLKl(输入/输出)、3个控制信号VPxCTL0、VPxCTLl和VPx-CTL2组成。时钟信号作为视频源的时钟信号输入/输出,控制信号作为视频源的同步信号输入/输出(行同步、帧同步、场标志,视频采集使能等)。每个视频口被分为上(B)、下(A)2个通道,VP0的A通道与McBSPO复用,VPl的A通道与McB—SPl复用,VP0和VPl的B通道与McASP复用,VP2则为单功能引脚。每个视频口可被配置为视频输入口或视频输出口,但是上(B)、下(A)2个通道只能同时被配置为输入口,或同时被配置为输出口,不能一个通道配置为输入口,另一个通道配置为输出口。

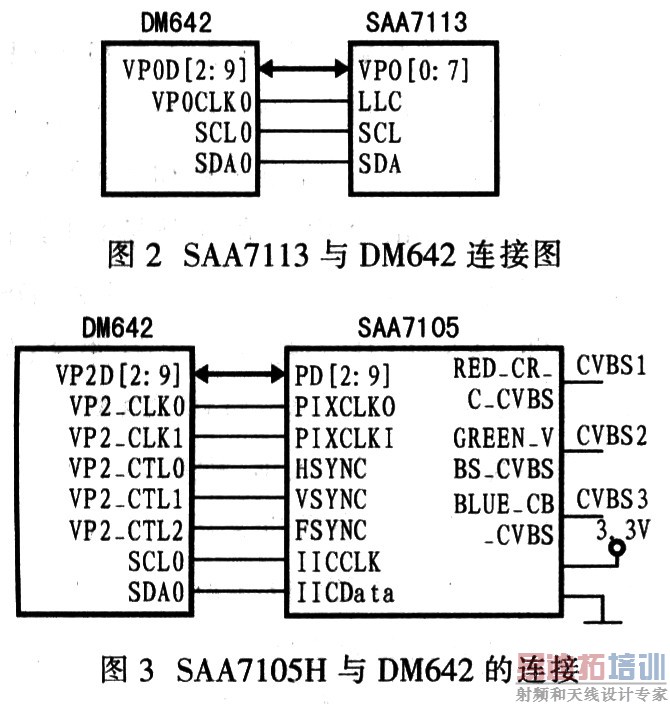

系统将VP0和VPl配置成为单通道视频输入和McASP口,VP2配置成为单通路的视频输出口。VPO与VPl配置为单通道视频输入口时,VPxCLK0作为视频源的输入时钟,VPxCLK1未用。而VPxCTL0、VPxCTLl和VPxCTL2则分别作为视频源中的时基码控制。当CAPEN信号无效或在EAV和SAV时基码之间时,将不对视频数据流进行采样。BT.656视频数据流采集的起始、水平同步、垂直同步等,受输入信号CAPEN和视频通道控制寄存器VCxCTL(x=A、B)中的VCEN、EXC、HRST、VRST、FLDD等控制位组合控制。当配置为单通道视频输出口时,VPxCLK1作为视频源输出时钟,VPxCLK0作为输入时钟。而VPxCTL0、VPxCTLl和VPxCTL2分别作为输出视频的HSYNC/HBLNK/AVID/FLD、VSYNC/VBLNK/CSYNC/FLD、CBLKN/FLD。3个VP口均作为8位视频接口,使用lO位数据总线中的高8位,即VPxD[9:2]。系统的视频解码和视频编码器分别选用Philips公司的SAA7l13H和SAA7105H,图2给出视频解码和DM642的连接图。图3给出视频编码和DM642的连接图。

当SAA7105H工作在VGA输出时,其工作时钟的上升沿和下降沿都要接收数据,图3中VP2与SAA7105H的连接方式,只用到VP2的8位数据线,因此VP2在每个时钟周期只有在上升沿输出8位数据,无法满足SAA7105H的工作要求。

2.4 地址空间映射

DM642的程序/数据空间以字节为单位进行统一编址,整个寻址空间为4 G字节。其片上存储器,片上外设及外部存储器接口(EMIF)均映射到此4 G字节空间中。

DM642的CEO空间被配置为64 bit SDRAM接口,分配给外扩的SDRAM使用。SDRAM的工作时钟由DM642的ECLKOUTl提供,其可由软件配置为EMIF的ECLKIN或CPU时钟/4、或CPU时钟/6,最高为133 MHz。一般情况下,配置为ECLKIN,即100 MHz。SDRAM在子空间的具体定位为:Ox8000 0000~Ox81FF FFFF。

DM642的CEl空间被配置为8Mx8 bit的Flash,在CEl子空间占据的具体空间定位为0x9000 0000~0x9007 FFFF。

DM642外部地址总线只有A[22:3],总共20根,所以CEl子空间最大的寻址范围为lMx8 bit。系统中CEl子空间除了分配给Flash以外,还分配给状态,控制寄存器、UARTA、UARTB等资源使用,其中Flash只占据CEl子空间的前一半的寻址空间,即最大的可寻址范围为512Kx8 bit,而Flash的设计容量为8 Mx8 bit,所以为寻址到Flash所有的地址空间,采用分页技术来实现对Flash的访问。

2.5 I2C总线

I2C(Inter-Integrated Circuit)总线是由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。是微电子通信控制领域广泛采用的一种总线标准。它是同步通信的一种特殊形式,具有接口线少,控制方式简单,器件封装形式小,通信速率较高等优点。由于连接到I2C 总线的器件有不同种类的工艺(CMOS、NMOS、双极性),逻辑0(低)和逻辑1(高)的电平不是固定的,它由电源VCC的相关电平决定,每传输一个数据位就产生一个时钟脉冲。

I2C总线由数据线SDA和时钟SCL构成串行总线,可发送和接收数据,在CPU与被控IC之间、IC与IC之间双向传送。在数据传送过程中共有3种信号,分别是开始信号、结束信号和应答信号。其中,开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据;结束信号:SCL为低电平时,SDA由低电平向高电平跳变,结束传送数据;应答信号:接收数据的IC在接收到8 bit数据后,向发送数据的IC发出特定的低电平脉冲。

DM642集成有一条I2C总线。DM642为总线的主设备。系统用I2C总线连接了以下从设备:2路视频解码器SAA7113H的控制口、1路视频编码器SAA7105H的控制口和1路实时时钟RTC。每个I2C总线的从设备均对应一个从设备地址,I2C总线以此从设备地址区分所访问的是哪个从设备。DM642通过I2C总线配置上述器件的寄存器。

2.6 网络接口

DM642的网络接口由EMAC与MDIO两部分组成的。其主要功能有:符合IEEE802.3协议;支持传媒无关接口(MII);8个独立的发送与接收通路;同步的10/100 Mbit的数据操作;广播及多帧的传送。

系统选用LXT971ALC作为10/100Base一TX以太网收发器。LXT971ALC的MII接口与DM642的MII接口对接。DM642的MII不支持TXER,它通过求反发送帧CRC来指出网络错误,所以LXT971ALC上的TXER引脚直接接为无效。系统只采用10/lOOBase-TX方式,信号经Hll02 1:1变压器变换成TX+、TX一、RX+和RX一信号,连接到RJ45连接器上。RJ45连接器选用406549一l,其上带2个LED指示灯,绿色LED,用作指示连接状态;黄色LED正常情况下用于指示数据传输。

3 系统调试

3.1 视频通道的驱动

系统中视频解码通道使用SAA7113,编码通道使用SAA7105H。这2个器件需要经过寄存器配置才能正常工作,因为寄存器数量众多,直接逐个配置寄存器相当复杂。系统开发了基于DSP/BIOS的应用程序,可以调用FWID API函数,实现对视频通道的驱动。以下是几个接口函数的使用说明:

(1)初始化工作 FVID_croat(name,mode,*status,

optArgs,*attm)参数说明:String name:device driver的名字,该device driver在DSP/BIOS中定义;Int mode:指定设备的打开模式为输入/输出;Int*status:该参数是application送给mini—driver的一个状态指针,由mini—dIiver来返回状态的;PtroptArgs:用于初始化FVID channel的具体参数,用结构体的形式打包,并将指向该结构体的指针传送给mini—driver进行处理;FVID_Attrs *attrs:FVID_Attrs结构参数为空,表示FVID_alloc,FVID_free,FVID_exchange calls为非block形式,无论成功与否,立刻返回。

(2)发送控制命令到mini—driver FVID_control(disChan,VPORT_CMD_START, NULL)参数说明:FVID_HandlevidChan:fvid通道句柄;Int cmd:cmd命令;Ptr args:cmd命令附带的信息。该函数发送一个控制命令给mini—dTiver,将由mini—driver做相应的响应,在这里通知vport端口开始工作。

(3)给VP口分配缓冲区FVID_alloc(fvidChan,bufp)参数说明:FVID_handle fvidChan:fvid通道句柄;Ptr bafp:分配的缓冲区指针。该函数从mini—ditver获取缓冲区指针。

(4)FVID_exchange(fvidChan,bufp) 参数说明:FVID_handle fvidChan:fvid通道句柄;Ptr butp:交换的缓冲区指针。该函数将转换好的图像数据发送给mini—driver处理,并传回空缓冲区指针,FVID_exchange函数相当于顺序执行FVID_free和FVID_alloc函数。利用FVID的API函数可方便配置和驱动视频通道,实现视频的采集和输出。

3.2 VGA输出

VGA(VideoGraphic Array)接口,即视频图形阵列,也叫DSub接口。VGA接口采用非对称分布的15针连接方式,其工作原理是将显存内以数字格式存储的图像信号在RAMDAC里经过模拟调制成模拟高频信号,然后再输出到显示设备成像。视频编码器SAA7105H支持VGA输出,SAA7105H被配置为VGA输出时,送输出缓冲区的数据必须为RGB格式,而非YUV4:2:2。用户可以自行编写相应的转换函数,或者调用TI img64.lib库中的IMG_ycbcr422p_rgb565函数实现视频格式的转换。

3.3 程序从Flash的引导

在系统上调试程序时,利用仿真器把程序下载到SDRAM内执行。当程序调试完毕应用时,应该把程序烧写到外部Flash里,实现系统每次上电后程序从Flash引导加载自动运行,省去每次利用仿真器下载程序。

DM642是以ROM方式引导系统的,当DSP上电或复位时,内核处于复位状态,并自动以ROM的读写时序从Flash的第0页起始地址开始复制lK字节的代码到DSP的片内内存起始地址为O的地址空间。然后释放CPU,使其从0地址开始运行程序。

Flash烧写根据不同的硬件设计,烧写步骤略有不同,但基本过程相同。系统Flash的烧写过程:①把引导程序文件boot.asm添加到要烧写的工程中,在BIOS中添加BOOT段,修改相应的CMD文件,编译原工程生成新的。out文件;②使用hex6x工具把生成的COFF格式的。out文件转化为。hex文件;③用FlashBurn建立。ccd文件;④用FlashBurn打开建立的。ccd文件,先擦除Flash,然后烧写Flash。

按照上述步骤烧写程序到Flash,在系统上电后程序将自动执行。应该注意的是,烧写程序后的系统仿真环境将难以进去,解决的办法是一边反复按复位键,一边打开仿真环境则可进去。

4 结语

系统研究并实现了一个通用的基于DM642的视频处理系统。采用了针对多媒体应用开发的专用媒体处理芯片DM642,该芯片配有丰富的外设接口,减小了系统硬件设计的复杂度,提高了系统的性价比;通过外接的SDRAM编程实现MPEG一2、MPEG-4、H.264等多种视频压缩编解码算法,灵活性大,实用性强,优于专用的视频编解码系统;由于DM642的高速运算能力,实时性强也是系统的一大优点。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...