- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

板子画完了,如何检查遗漏未布线的线路?

第一个是tools-Verify Design-connectivity发现有isolate的线路,并全部依此连上后,再次Verify,显示如下,我理解的是此刻connectivity已经完整了。

但是使用File-Report-statistics生成的报告却如下,显示的是总共有多少Connection 但是部分连接到是多少 未连接的有多少。

Statistics Report和之前用Verify产生的报告就矛盾了,我到底该依哪一份报告呢?

铺铜以后,目测原文件的飞线是没有了。当然也只是目测,还是要以报告为准啊。谢谢大家了

我都是信tools-Verify Design-connectivity ,至于File-Report-statistics不知道是否考虑了如A和B引脚在原理图中连接在一起然后再一点接地,结果你在PCB中对A和B引脚是分开就近打孔接地,这样A和B没有直接相连,不知道软件统计时是否觉认为你有一个未连接?个人认为而已,没什么依据的,不知道是否这样,也请指导真相的朋友解答一下。

我也是相信DRC检查的,应该没有问题。楼上说的可能是报告认为没有连上的原因之一,我想可能还包括你的线有没有连到圆心的问题。这点目测不太能看出来。

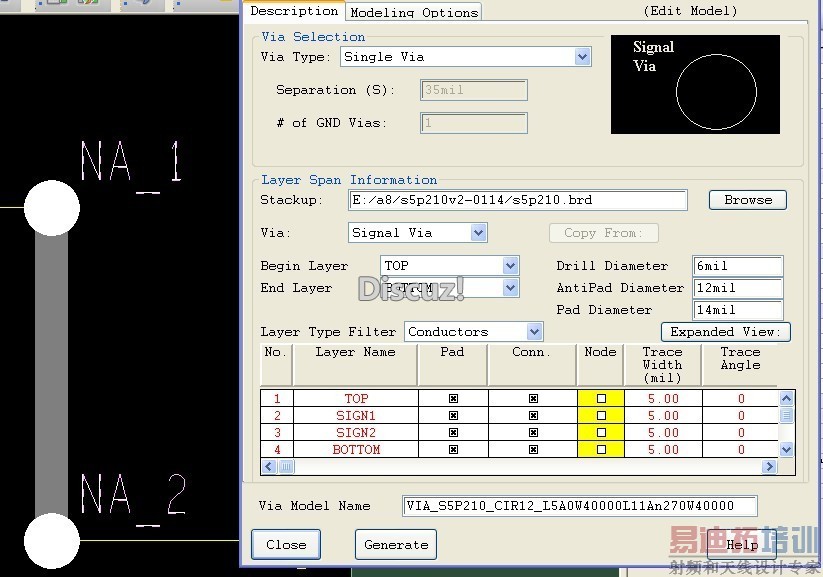

说的有道理哈,受教了。感觉PADS还是有点bug的,例如我在Route的时候将VIA打到同Net的连线上的时候,飞线并没有消失(VIA的NET和两条连线是一样的)必须要把该VIA和同net的PAD再连接一次飞线才会消失。可能是我操作方法不对吧?

第一次用PADS,还在摸索中,目前看来就用Verify的结果吧。谢谢了!

嗯就用Verify的结果了,谢谢你!

首先,您的板子是否有多层覆铜接地?这种结果有可能是因为一层上(往往是元件面)覆铜之后,由于走线和元件布局的原因,有很多块被隔断的孤立的铜被认为是未完全连接的,而实际上这些孤立铜层上都有过孔在另一个接地平面上连接上了,所以DRC不会报错,不知道是不是这种情况

有可能,有些地方确实没法走线进去了,只有通过覆铜+VIA的方式.Connectivity没问题的话 应该就还好。另外请问一下有没有遇到过Connectivity 检查没问题,但是依然有飞线的情况?

曾经有过一次忘了更改了哪个设置,所有GND的飞线就都出现了,不过只要重新做一次connectivity的检查,应该就不会还有飞线出现的

好的!感谢!有了高手帮忙,心里也要稳当些了!

tools-Verify Design-connectivity这个完全可以相信!

好!THX!

学习!

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:一个板子封装的中心点放在第一脚,怎样快捷的把坐标改在元件的中心点?哪位能.

下一篇:收集问题了.明天开PCB探讨会.有有问题吗?可以提出来明天帮解决.