- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

大家给些意见啦

录入:edatop.com 点击:

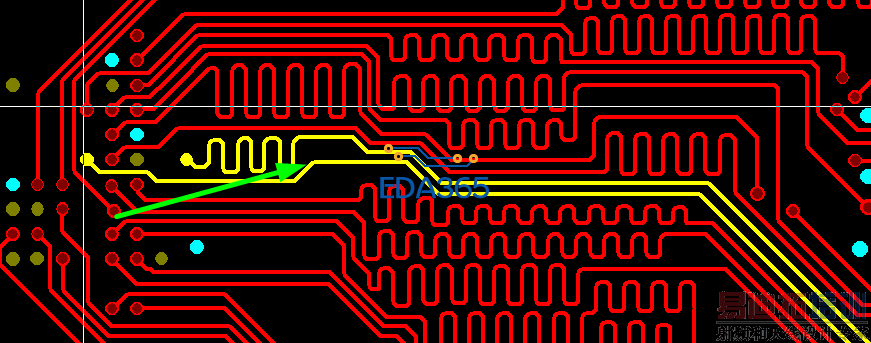

小弟是个菜鸟, 看了大师的DDR教程 用的是大师教程里的文件,看完教程之后自己把数据和地址的走完了,第一次走 大家给些建议。小弟先在这里谢谢了

J-0708.rar

J-0708.rar

这个论坛有点荒凉了。 一个帖子7个小时没人回复。

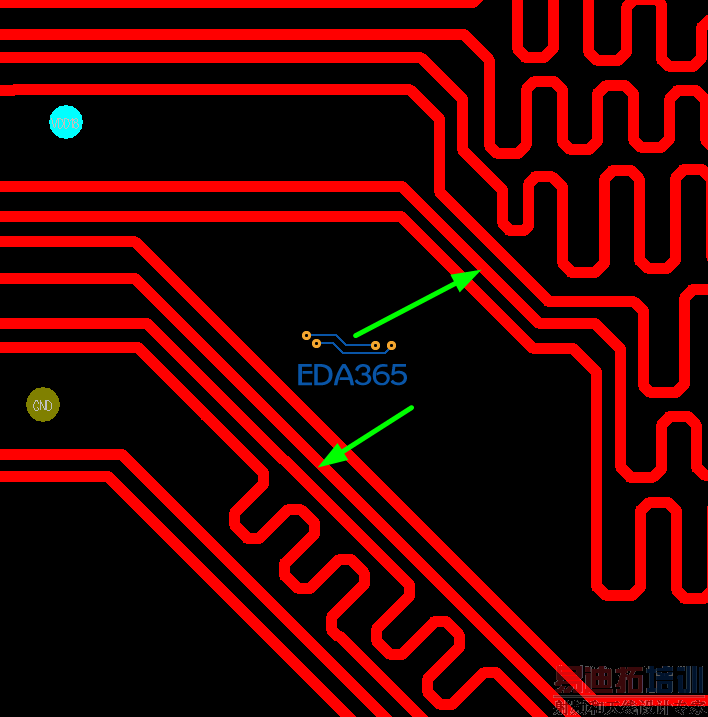

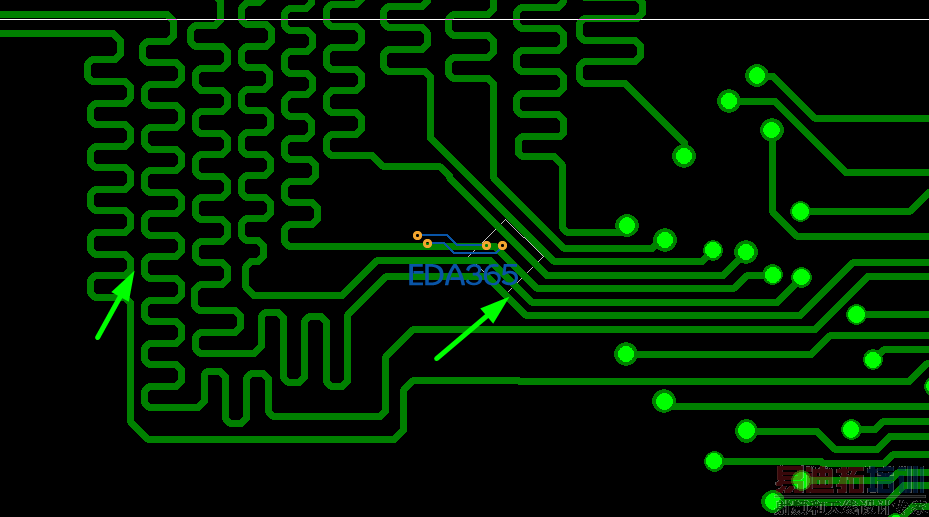

DRAM0_CLK#和DRAM_CLK是一对差分线。请等长等宽与其它走线保持三W原则。

图中走线有突起。

多谢 小弟明白了

有两个比较大的问题:

1,差分时钟没按差分进行

2,没做到3w,串扰不好解决

1、差分时钟没按差分进行?大哥的意思是:等长蛇形时可牺牲耦合,此外就必须时刻紧耦合?曾经看过一篇论文说差分线之间的耦合只占20%左右,更多是对地耦合,故差分线走线层需紧靠"地"平面看过两份走这种DDR2 时钟差分线的设计,别人好像对CK和CK#都不太严格于紧耦合而侧重等长,两块板子都能跑起来(可能运行的频率不太高吧),当然可靠性就很难考究了,所以有时自己为了容易走线很多时候也心存侥幸。希望大家提出一些权衡的办法。

走过、路过、看过

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:求助:新画的GSP板搜星效果差,上PCB

下一篇:检查网络测试点的布通率

射频和天线工程师培训课程详情>>