- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

51系列单片机IO引脚的驱动能力与上拉电阻分析

单片机输出低电平时,将允许外部器件,向单片机引脚内灌入电流,这个电流,称为“灌电流”,外部电路称为“灌电流负载”;单片机输出高电平时,则允许外部器件,从单片机的引脚,拉出电流,这个电流,称为“拉电流”,外部电路称为“拉电流负载”。

这些电流一般是多少?最大限度是多少? 这就是常见的单片机输出驱动能力的问题。

早期的 51 系列单片机的带负载能力,是很小的,仅仅用“能带动多少个 TTL 输入端”来说明的。P1、P2 和 P3口,每个引脚可以都带动 3 个 TTL 输入端,只有 P0 口的能力强,它可以带动 8 个!

分析一下 TTL 的输入特性,就可以发现,51 单片机基本上就没有什么驱动能力。它的引脚,甚至不能带动当时的 LED 进行正常发光。记得是在 AT89C51 单片机流行起来之后,做而论道才发现:单片机引脚的能力大为增强,可以直接带动 LED 发光了。

看

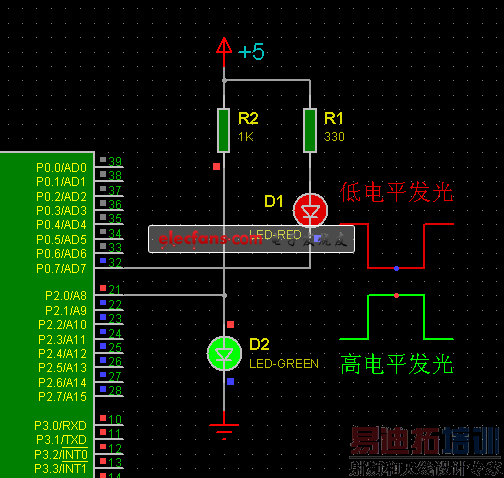

看下图,图中的 D1、D2 就可以不经其它驱动器件,直接由单片机的引脚控制发光显示。

虽然引脚已经可以直接驱动 LED 发光,但是且慢,先别太高兴,还是看看 AT89C51 单片机引脚的输出能力吧。

从 AT89C51 单片机的 PDF 手册文件中可以看到,稳态输出时,“灌电流”的上限为:

Maximum IOL per port pin: 10 mA;

Maximum IOL per 8-bit port:Port 0: 26 mA,Ports 1, 2, 3: 15 mA;

Maximum total I for all output pins: 71 mA.

这里是说:

每个单个的引脚,输出低电平的时候,允许外部电路,向引脚灌入的最大电流为 10 mA;

每个 8 位的接口(P1、P2 以及 P3),允许向引脚灌入的总电流最大为 15 mA,而 P0 的能力强一些,允许向引脚灌入的最大总电流为 26 mA;

全部的四个接口所允许的灌电流之和,最大为 71 mA。

而当这些引脚“输出高电平”的时候,单片机的“拉电流”能力呢? 可以说是太差了,竟然不到 1 mA。

结论就是:单片机输出低电平的时候,驱动能力尚可,而输出高电平的时候,就没有输出电流的能力。

这个结论是依照手册中给出的数据做出来的。 [p]

51 单片机的这些特性,是源于引脚的内部结构,引脚内部结构图这里就不画了,很多书中都有。

在芯片的内部,引脚和地之间,有个三极管,所以引脚具有下拉的能力,输出低电平的时候,允许灌入 10mA 的电流;而引脚和正电源之间,有个几百K的“内部上拉电阻”,所以,引脚在高电平的时候,能够输出的拉电流很小。特别是 P0 口,其内部根本就没有上拉电阻,所以 P0 口根本就没有高电平输出电流的能力。

再看看上面的电路图:

图中的 D1,是接在正电源和引脚之间的,这就属于灌电流负载,D1 在单片机输出低电平的时候发光。这个发光的电流,可以用电阻控制在 10 mA 之内。

图中的 D2,是接在引脚和地之间的,这属于拉电流负载,D2 应该在单片机输出高电平的时候发光。但是单片机此时几乎没有输出能力,必须采用外接“上拉电阻”的方法来提供 D2 所需的电流。

哦,明白了,外接电路如果是“拉电流负载”,要求单片机输出高电平时发挥作用,那就必须用“上拉电阻”来协助,产生负载所需的电流。

下面做而论道就专门说说上拉电阻存在的问题。

从上面的图中可以看到,D2 发光,是由上拉电阻 R2 提供的电流,D2 导通发光的电压约为 2V,那么发光的电流就是:(5 - 2) / 1K,约为 3mA。

而当单片机输出低电平(0V),D2 不发光的时候,R2 这个上拉电阻闲着了吗? 没有!它两端的电压,比 LED 发光的时候还高,现在是 5V 了,其中的电流,是 5mA !

注意到了吗? LED 不发光的时候,上拉电阻给出了更大的电流!并且,这个大于正常发光的电流,全部灌入单片机的引脚了!

如果在一个 8 位的接口,安装了 8 个 1K 的上拉电阻,当单片机都输出低电平的时候,就有 40mA 的电流灌入这个 8 位的接口!

如果四个 8 位接口,都加上 1K 的上拉电阻,最大有可能出现 32 × 5 = 160mA 的电流,都流入到单片机中!

这个数值已经超过了单片机手册上给出的上限。如果此时单片机工作不稳定,就是理所当然的了。

而且这些电流,都是在负载处于无效的状态下出现的,它们都是完全没有用处的电流,只是产生发热、耗电大、电池消耗快...等后果。

呵呵,特别是现在,都在提倡节能减排,低碳...。

那么,把上拉电阻加大些,可以吗?

回答是:不行的,因为需要它为拉电流负载提供电流。对于 LED,如果加大电阻,将使电流过小,发光暗淡,就失去发光二极管的作用了。

对于 D1,是灌电流负载,单片机输出低电平的时候,R1、D1 通路上会有灌电流;输出高电平的时候,那就什么电流都没有,此时就不产生额外的耗电。

综上所述,灌电流负载,是合理的;而“拉电流负载”和“上拉电阻”会产生很大的无效电流,这种电路不合理。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:DSP双模手机的小灵通网络优化分析

下一篇:一种LED闪光驱动方案介绍