- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于PCIE/104总线的高速数据接口设计

摘要:PC/104作为一种工业嵌入式的总线标准,由于其小尺寸结构、低功耗,以及软件通用性而被广泛用于航空航天、工业控制等领域。这里主要介绍了下一代总线技术PCIE总线在PC/104标准下的应用。阐述了数据接口卡的系统组成和各单元的功能,以及驱动在linux操作系统下的实现原理。自行设计并实现了板卡原理图和PCB,同时简述了高速PCB仿真方面的知识,并针对PCIE差分线进行了版级仿真。最后利用PLX公司提供的开发套件在Linux操作系统下完成了板卡驱动的开发和调试。

关键词:PCIe总线;PC/104;嵌入式;PCB仿真

0 引言

PCIE总线是由Intel公司提出用来取代现行PCI总线的下一代总线技术,被公认为未来总线的发展方向,目前已经成功应用在了商业机上。相对于目前流行的PCI总线,它具有如下特点:

采用了串行点对点模式,数据总线从并行走回向串行无疑是一个趋势,如现在流行的SATA总线、PCIE总线和rapidIO总线都是串行总线。现在串行总线在速度上的优势可以说是毋庸置疑的。PCIE总线在每个方向上都有X1,X2,X4,X8,X16或X32个信号对,用户可根据不同的需求采用不同的配置。同时串行信号还具有管教更少,便于调试的优点。

PCIE采用了基于数据包的协议来编码事物,而不是PCI体系结构的总线周期。数据包被串行发送和接受,并被字节拆分来通过物理链路。链路上实现的通道越多,数据包发送的数据越快,链路的带宽也越宽。同时PCIE还定义了各种类型的数据包,如存储器读/写请求、I/O读/写请求、配置读/写请求、消息请求和完成数据包等。

PC/104标准是一种嵌入式的总线标准,具有功耗低,尺寸小,堆栈式结构的特点。随着目前各种应用数据传输量的增大,现行的PCI总线在带宽方面已经略显疲态,而新近瑞士逻辑提出的PC/104 Express标准,使得PCIE总线技术被成功地应用在了PC/104标准的板卡上。本文采用了PLX公司的PEX8311桥接芯片,完成了PCIE到局部总线接口的转换,应用PLX公司提供的开发工具在Linux操作系统下实现了板卡的驱动应用。在软硬件两方面进行了设计,完成了PCIE/104板卡的功能,升级了系统的总线。

1 PCIE/104高速信号接口卡的系统

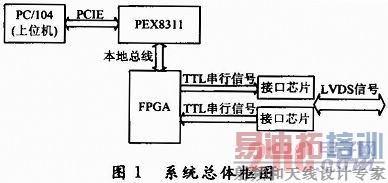

PCIE/104高速信号接口卡的系统设计方案如图1所示。

外部传感器采集到的数据通过LVDS,RS 422等电平方式,以固定的不同串口波特率传到FPGA内部集成的各自对应的双口RAM中。当写入了固定字节后,设定标志位stage为1,同时发出中断信号LINT#给PEX8311。PEX8311产生了assert_INT1信息,并通过PCIE接口发给上位机。上位机保存好现在的任务后,通过PCIE开始发出存储器读命令给PEX8311。PEX8311获得命令后,向FPGA发出本地总线申请信号,FPGA作为本地端的控制器将本地总线控制权交给PEX8311。PEX8311开始读数据,首先要进行的是读取标志位,在读取了标志位后,上位机就知道是哪几路串口信号需要读入。然后,把标志位清掉,这样相当于清掉了中断信号。接着,中断服务程序在进入到各个串口的RAM中,来读取相应的数据。在多路串口信号传输过来时,针对该系统,采用的是优先满足高速串口的原则,也就是采用高速串口的标志位作为中断信号,每次产生中断后查询其他标志位。数据到上位机后待处理。该系统目前实现的是两路串口,而多路串口原理相同。 [p]

1.1 硬件总体概述

主要包括以下几部分,PEX8311桥接芯片负责完成本地总线和PCIE总线的相互装换;FPGA选用了spartan-3an 1400K。这里在内部实现了3个模块,首先完成双口RAM模块;其次完成了多路串口数据的接受与协调模块;最后还要实现PEX8311芯片本地端控制器模块。

1.1.1 PEX8311芯片介绍

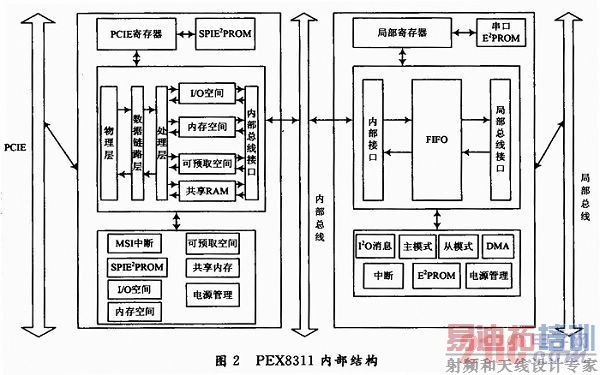

PEX8311是PLX Technology公司推出的一款专用于将DSP,FPGA等处理器总线接口升级为PCIE的桥接器件。利用PEX8311灵活的局部总线可以方便地连接多种存储器、缓存器及。FPGA,DSP等逻辑芯片,使复杂的PCI-E接口设计简单化。PEX8311兼容PCI Express 1.0标准,其本地总线和寄存器与PCI9056兼容,能够提供完整的本地总线到PCI-E的接口,包括地址转换、包生成与解码、信号中断支持及并/串转换等。

PEX8311的特点如下:

(1)集成了单通道、全双工2.5 Gb/s传输的PCI Express端口;

(2)可配置局部总线宽度,支持8位、16位和32位的总线方式;

(3)支持单路和多路总线操作模式;

(4)高性能的DMA数据传输,支持数据块模式、集散模式、循环队列管理模式和命令模式;

(5)支持端点和根复合体模式;

(6)芯片小型封装,适合紧凑的电路板设计;

(7)芯片低功耗设计;

(8)3.3 V的I/O并兼容5 V系统;

(9)启动配置的串行E2PROM支持(SPI和Microwire接口);

(10)有8 KB的通配共享RAM。

PEX8311的内部结构如图2所示。

[p]

1.1.2 PCIE/104总线标准介绍

PC/104是最早由瑞士逻辑提出的一种工业总线标准,它由最早的PC/104总线发展到PC/104+总线,直到目前的PC/104 Express,分别对应ISA总线、PCI总线和PCIE总线。由于它是一种堆栈型的嵌入式总线,所以将PCIE总线应用在这个标准上与普通的PCIE金手指有一些不同。为了满足PC/104的嵌入式堆栈结构,使其能够实现从板子上、下都可以连接,必须采用PCIE Switch芯片,这里使用的是PERICOM公司

制造的PI2PCIE2412款Switch芯片。电路原理图如图3所示。

图3中接受、发送和差分时钟这3对差分信号线通过转接芯片变成了6对差分信号线。由主机板卡发出选择信号(cpu_dir),分别控制设备板卡是在主机板卡的上面还是下面。同时采用MAX6306芯片来链接PEX8311的复位端和PCIE接插件的复位端,同时实现了手动复位和LOCAL端的复位。

1.1.3 PEX8311的外围电路配置与LOCAL端接口的控制

PEX8311有几个类别的模式选择,分别是根联合体模式(Rootcomplex)与终端模式(Endpoint),根据需要这里选择了终端模式。此外PEX 8311还区分C模式,J模式,M模式。这三种模式解释如下:C模式的地址线与数据线是分开的,J模式下地址线与数据线是复用的,而M模式是针对了Motor的本地端CPU设置的。三种模式通过模式选择管脚选择,这里选择C模式作为工作模式。PEX8311有1.5 V,2.5 V,3.3 V三种电源供电以及一个模拟电源1.5VPLL。在配置寄存器方面,PEX8311有两个配置寄存器,分别是采用Spi-Compatible接口的PCIE配置寄存器和采用了Micro-Wire-Compatibel接口的本地配置寄存器。采用了Spartan-3an 1400 k来提供控制接口与高速缓存,选择这款FPGA主要因为它是有内部FLASH,不用再加外部的E2PROM。

由于PC/104是一种嵌入式的板卡,体积比较小,所以用这款FPGA是可以节省板上的空间。FPGA内部程序的编写是关键之一。这里采用Verilog,实现对PEX8311的控制,当上位机响应了中断后,对PEX8311发出读数信号。PEX8311通过LHOLD申请控制本地总线,待收到FPGA发出的LHOLDA响应信号后获得本地总线的控制权,并立即启动4 B突发模式。FPGA在收到有效的LW/R读信号和ADS地址选通信号后,发出Ready本地准备好应答信号。PEX8311开始从双口中读取数据,传输最后一个数据时,PEX8311发出BLAST信号,双口RAM使得读使能和输出使能无效。

1.2 系统软件部分的实现

该系统的软件部分是在Linux下实现的,在Linux中所有的设备都被看成文件来对待。在Linux内核中,设备驱动作为文件系统的一个模块存在。它向下负责与硬件系统的交互,向上通过一个通用的接口挂接到文件系统上面。从而和系统的内核链接起来。设备驱动为应用程序屏蔽了很多细节。使得应用程序对外设的操作就和操作普通的文件是一个样子的。利用PLX公司提供的开发工具,驱动的开发是比较方便的,本文系统中主要用到的是要编写一个中断服务程序:系统在收到中断,保存现场。进入中断服务程序。首选读取标志位,再马上清中断,之后读取响应RAM中的数据。最后恢复现场,完成操作。

2 系统PCB设计和高速信号的完整性分析

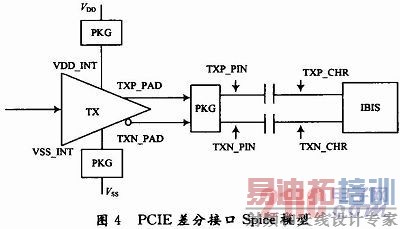

由于PCIE的传输速率较高,单向速率达到2.5 Gb/s。所以对板子的布线有严格的要求。叠层这里选用了8层PUCB板,有4个电源层,使得每个信号都能够屏蔽在电源层与地层中间。从而减少了信号的电磁辐射。对于PCIE的差分线部分:微带线要求差分线宽5 mil,间距小于12 mil,差分线间距离大于20 mil,同时与地层间距为3.5~5.5 mil。带状线要求线宽4 mil,间距小于11 mil,间距大于20 mil。且对于收发差分线,差分线长差距不能大于5 mil。这些都是为了能达到PCIE规范的要求,即单端阻抗55 Ω,差分阻抗100 Ω(偏差10%)而设置的。 [p]

经过ploar软件计算,将以上的数据输入进去,再加入PCB厂家提供的介电常数等参数,最后得出的阻抗完全满足设计需求。多层板的高速信号设计很有必要进行信号完整性仿真,应用厂家提供的IBIS模型,采用Hyperlynx对板子进行了本地端和时钟端的信号完整性仿真。并根据仿真对布线提供了约束条件。而针对PCIE的高速差分端总线,因为在高速信号仿真方面IBIS模型还不够精确,所以,PLX公司对其两对收发端口提供SPice模型,如图4所示。

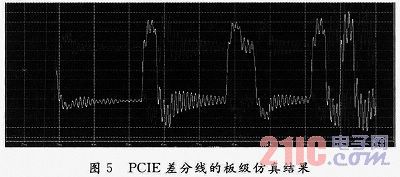

将上诉模型导入HSpice中,同时引入PCIESwitch芯片给出的IBIS模型与板子上面的差分线trace的rglc模型。输出端的仿真效果图如下,可以看出差分信号的幅值是可以满足PCIE规范的电气要求的。

3 结语

PC/104作为一种嵌入式总线标准已经被很多控制系统所采用,而PCIE/104接口的提出将未来最为流行的串行差分总线结构,引入到了这种嵌入式总线标准,从而为各种高速、高带宽的嵌入式系统提供了选择。目前该系统由于采用了PCIE总线,相比采用PLX9054实现的PCI接口具有明显的优势。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:TMS320C32的中断编程方法介绍

下一篇:汽车用仪器检定系统研制