- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于双FPGA+ARM架构的 像压缩系统

目前的图像压缩存储方案大都无法支持高分辨率图像。另外,在一些DSP解决方案中,因为DSP接口不灵活以及DSP本身处理能力的限制,很难支持高分辨图像压缩。

本设计开发出了一套基于双FPGA+ARM架构的高速计算机屏幕图像压缩系统。系统通过对图像压缩系统任务的划分,利用FPGA的并行计算能力和灵活的编程方式,完成图像压缩算法。对于压缩后的码流,系统采用ARM管理,基于linux的嵌入式ARM系统能够以文件的形式存储码流,另外,ARM对网络和音频常用设备能方便地管理。系统支持主流接口(VGA,DVI),压缩后的码流可以存储在本地硬盘,也可以通过网络发送到远端服务器。双FPGA的设计对计算机屏幕图像压缩更为方便,原始图像经过前端预处理FPGA进行帧间检测,以决定该帧图像进入主FPGA的压缩模式,主FPGA为核心压缩引擎,负责完成高速图像压缩算法。

1 系统架构与实现

系统整体架构如图1所示,采用双FPGA+ARM架构,主要包括图像前端预处理、图像压缩模块和码流管理部分。

前面一块FPGA完成前端预处理,如分辨率检测、色彩转换和图像分析等功能;后面一块FPGA用来实现图像实时压缩,其中ARM对系统进行管理,如压缩后码流管理、网络管理和音频录制等。

1.1 预处理模块

本系统同时支持VGA、DVI两种主流显卡接口。采用AD9888[2]作为视频模数转换器,TI公司的TFP403[3]为DVI接收芯片。Xilinx公司Virtex4[4](XC4VLX40)完成图像预处理,主要包括图像数据的采集、色彩空间转换和帧间检测。前端处理模块如图2所示。

1.1.1 图像数据采集

预处理FPGA接收到的图像数据为接口芯片送来的图像数据,包括像素时钟信号(PCLK)、场同步信号(VSYNC)、行同步信号(HSYNC)以及数据信号(R[7:0],G[7:0],B[7:0])。图像数据的采集包括判断图像分辨率和提取图像数据两个步骤。

当前的计算机屏幕分辨率很多,工业VGA标准规定了各种分辨率的像素时钟及场、行同步信号时序,根据相邻场同步信号(VSYNC)之间行同步信号(HSYNC)数目,以及相邻行同步信号(HSYNC)之间像素时钟(PCLK)数目识别VGA信号分辨率。根据场同步信号(VSYNC)和行同步信号(HSYNC)提出图像数据。

1.1.2 色彩空间转换

VGA输出为RGB信号,而人眼对图像的亮度分量更为敏感,所以,对图像数据进行色彩空间转换,将RGB信号转换为YUV信号,转换公式:

系统实现时采用4:2:2采样模式,FPGA采用定点化处理后,得到亮度分量Y 和色度分量UV。

1.1.3 帧间检测

帧间检测的核心思想是对比相邻两帧图像,判断每个像素点是否变化。以3×3的块为判断单元,如果有变化则将该像素位置和像素值都存起来;如果没有变化则不传输这些信息。当得到了一个4×4的块以后把这个16个点的信息作为一个整体传给后面的模块,然后统计1帧图像总的码流大小。如果该值低于一个设定的阈值,则认为当前帧没有变化,直接传当前帧变化部分的像素和位置信息到后面的码流整理模块;如果统计后码流的大小大于设定的阈值,则将当前帧送入LX100中进行压缩。

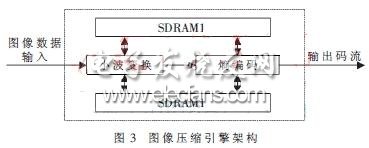

1.2 图像压缩模块

图像压缩为系统核心模块,该压缩引擎包括小波变换和熵编码,算法全部由系统主FPGA完成。该FPGA芯片选用Xilinx公司的Virtex4[4]系列FPGA(XC4VLX160)。图像压缩引擎结构如图3。

在系统算法设计中,图像小波变换采用了基于离散小波变换的空间推举算法(SCLA)[5]。不同于传统的离散小波变换(DWT),SCLA对行与列同时进行变换,其乘法次数是小波变换算法中最少的,而重建图像质量也很高,PSNR值优于JPEG,接近JPEG2000。编码算法采用了改进的无链表零树编码算法(SLC),该算法综合了多层次零树编码算法(SPIHT[6])和无链表零树编码(LZC[7])的特点,在性能上优于LZC,逼近SPIHT,而且易于硬件实现。

系统的架构由FPGA和两片外部SDRAM实现。SDRAM用于缓存小波变换后的小波系数。FPGA完成小波变换算法SCLA和熵编码算法SLC。SCLA算法由5个流水线小波滤波器完成,每个滤波器完成一层小波分解,而小波分解运算需要乘法器,在FPGA芯片选型时,根据小波滤波器中需要乘法器的个数选择FPGA。在本系统中,5个流水的小波滤波器包括36个乘法器,对于亮度分量Y和色度分量UV两路数据并行处理,则需要72个乘法器,而在Virtex4系列FPGA(XC4VLX160)中有96个DSP单元。由小波变换得到小波系数,系统设计时采用2片外部SDRAM和FPGA片内SRAM结合的方法缓存小波系数。对于亮度分量Y和色度分量UV两路数据并行处理以提高系统吞吐量,SDRAM1和SDRAM2分量用来缓存Y和UV的小波系数。熵编码算法SLC负责对小波系数编码,该算法以一棵小波树为基本处理单元,即当前端小波系数构成一棵小波树时,熵编码模块便启动编码,从而完成一帧图像所有小波树的编码。 [p] 1.3 码流管理模块

对于图像经过FPGA压缩后的码流,系统采用ARM芯片进行管理,该芯片为Cirrus Logic公司的工业级嵌入式处理器EP9315[8]。该处理器具有ARM920T核,最高主频达200 MHz,并具有丰富的外围接口,包括网络、USB、音频等。FPGA和ARM之间通信由I2C总线完成,当FPGA完成一帧图像压缩后,通过FPGA的GPIO发送一个终端信号给ARM,并准备好一帧码流长度等信息。ARM中断服务程序响应该中断,通过I2C接口读走码流长度,通过映射SRAM的方式从FPGA读取压缩码流到ARM内存,然后以文件的形式存储码流到本地硬盘,或者通过网络发送到远端服务器。

2 实验结果与性能

2.1 算法性能验证

系统设计初期,用软件对算法的性能进行了验证。在PC上对一组Lena等标准图像进行压缩,得到不同的重建图像,对重建图像求解PSNR值,式(2)为PSNR计算公式。其中Mean Square Error(MSE)表示原始图像和重建图像对应像素的均方误差值。

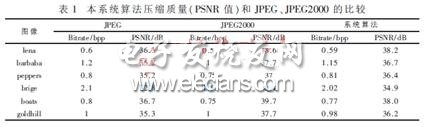

表1为本系统采用算法与JPEG及JPEG2000对标准图像压缩后重建图像的PSNR比较。从表中可以看出,本系统采用算法远优于JPEG,接近JPEG2000。PSNR值的比较以压缩比(对应表中Bitrate)为基准,即在相同压缩比的情况下对比PSNR值。

2.2 硬件实现和硬件压缩

硬件系统电路板采用10层板制作工艺,电路板面积为30.8 cm×16.7 cm,在100 MHz工作频率下对系统测试,结果表明系统工作稳定。表2为系统对1 600×1 200、1 280×1 024和1 024×768三种常见分辨率的计算机屏幕进行的记录,记录的图像源采用了各类计算机屏幕常见图像,如Word文档、PPT文件、动态雷达图像和一段视频。其中,PPT的平均翻页速度为60 s。由表2可以看出,系统对于Word文档、PPT文档等只有局部变化的图像能够达到非常高的压缩比,压缩帧率约为60帧/s。

本文结合应用提出图像压缩算,以FPGA为核心计算平台,设计了一套计算机屏幕图像记录系统。系统实现了对1 280×1 024×24 bit图像每秒记录27帧,对1 600×1 200×24 bit图像每秒记录17帧,对PPT、Word文档等只有局部变化的屏幕图像每秒可记录60帧,且压缩后重建图像质量优于JPEG,与JPEG2000接近。同时,对于压缩后的码流,系统采用ARM以文件的方式管理,有利于码流本地存储以及通过网络传输等灵活的应用。另外,系统支持多种输入接口,提高了硬件系统的灵活性,具有广阔的应用前景。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:一种DSP与PCI总线的接口设计

下一篇:基于DSP双路音频信号实时处理系统设计