- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的视频应用OSD设计

近年来,数字视频监控系统在银行、高速公路、楼宇等各个领域取得了广泛的应用。在数字视频监控系统中,OSD(On Screen Display)技术是不可或缺的部分。OSD为用户提供友好的人机界面,能够使用户获得更多的附加信息。

系统构成

本文介绍的系统是基于TI DSP TMS320DM6

3与FPGA的完整视频监控系统,支持1路视频的输入和1路视频输出,此外还提供网络接口。

视频输入采用TI的高性价比视频解码器TVP5150A来实现,TVP5150A可实现两路复合视频输入或一路S-video视频信号的采集。通过I2C进行寄存器配置,输出数字视频信号遵循ITU656标准。

TVP5150A解码后的数字视频信号通过DM6

3的视频端口1传送给DSP,由DSP进行必要的视频处理,由网络接口输出给远端设备。另一方面,DM6

3把从网络接收的视频数据处理后,通过视频端口2,经过FPGA,由SAA7105显示输出,具体结构如图1所示。

输出部分采用SAA7105实现。SAA7105是NXP公司的一款高性能视频编码器,可提供复合视频输出、VGA视频输出以及HDTV高清视频信号的输出。SAA7105的控制也通过I2C实现,接收复合ITU656标准的数字视频信号。

视频处理部分采用的是TI的DSP TMS320DM6

3来实现。DM6

3主频可达600MHz,有2个20位的视频端口,视频端口支持BT.656、Y/C等数字视频接口,DM6

3还集成了网络MAC,可实现网络接入。

硬件性能的发展速度总是很难满足软件的需求。在视频处理越来越复杂的应用中,DSP承担着繁杂的视频处理任务,资源变得非常紧张,所以在本系统设计中,采用了FPGA实现OSD的设计,可以减轻DSP的负担。

OSD实现部分选用的是赛灵思公司的XC3S250E。XC3S250E是赛灵思SPARTAN-3E系列的FPGA,有25万个逻辑门。

图1:基于TMS320DM6

3与FPGA的完整视频监控系统架构示意图

OSD实现

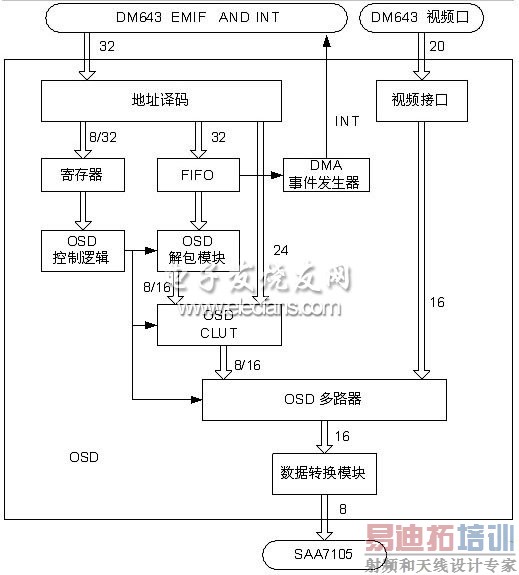

SAA7105无法实现OSD功能,而由XC3S250E来实现。主控芯片DM6

3只需要通知FPGA要显示的内容和位置,具体的工作由FPGA执行。OSD的逻辑框图如图2所示。

图2:OSD功能框图 [p]

OSD FPGA通过EMIFA从DSP DM6

3接收OSD数据和控制指令,通过DSP的视频端口1接收视频数据,并将OSD的信息叠加到视频数据上,输出给视频编码器SAA7105。OSD的各功能模块描述如下。

地址译码模块的数据端口与DSP DM6

3的EMIFA低32位数据接口,接收DM6

3发出的数据与控制信息,这些数据和控制信息是DM6

3发出的原始32位数据。地址译码模块将接收到的OSD数据,如OSD的内容等,以32位数据格式放入到FPGA的内部FIFO中。而控制信息主要是通过一组控制寄存器对OSD实现控制。

与DSP直接连接的模块还有视频接口模块。视频接口模块与DSP的视频端口2相连,存储来自DSP视频端口的数据与控制信息。这些控制信息被直接传输给OSD多路控制模块,同时控制信息也直接控制视频解码器SAA7105。

OSD控制逻辑把从控制寄存器组得到的控制信息输出到OSD的各个功能模块,实现对OSD的控制。寄存器组主要分为两个部分:一是异步寄存器组,向OSD发送如复位、OSD使能和选择数据宽度的控制信息;另一个是同步寄存器组,主要控制OSD的位置信息。

OSD解码模块根据控制逻辑的控制信息,从FIFO中取出要显示的数据,以与视频数据同步的方式输出到OSD CLUT模块。从FIFO中获得的数据是原始的DSP 32位数据,而OSD CLUT模块需要的数据是8/16位的,所以OSD解包模块需要以一定的规则将32位数据解包,以视频端口的频率将32位数据以8/16的宽度传输给OSD CLUT模块。

FIFO模块的另外一个功能是向DMA事件发生器模块传递FIFO的状态信息,如FIFO满或FIFO空。DMA事件发生器监控这些事件,如果发生,则以中断的模式发送给DM6

3,以实现对FIFO的正确读写操作。

OSD CLUT模块为从OSD解包模块接收的每个象素的数据查找YCbCr的对应值,并控制这些OSD CLUT数据的输出顺序。这种转换关系是由DSP通过24位的数据端口传送过来的。OSD CLUT模块的数据直接输出给OSD多路控制器模块。

OSD多路控制模块根据从OSD CLUT模块接收到的Alpha控制位确定输出视频数据,如果当前为OSD信息,即Alpha控制位有效,则输出OSD数据给数据转换模块。否则,输出从视频接口模块接收的原始视频数据,以此来实现OSD功能。

OSD多路控制器输出的数据并没有直接送给视频解码器,而是通过数据转换模块,根据具体的应用条件,进行必要的数据格式转换。由SAA7105的接口时序可知,当SAA7105配置为复合视频输出时,其要求的数据为单时钟沿数据,此时数据转换模块不作任何工作,将从OSD多路控制模块接收的数据原封不动地传输给SAA7105;如果SAA7105配置为VGA或HDTV输出模式时,需要双时钟沿数据,此时数据转换模块将从OSD控制器接收到的单时钟沿数据转换成双时钟沿数据,输出给视频解码器SAA7105。

由此可见,FPGA完成了OSD的所有工作。如果要显示OSD内容,DM6

3只需要通过EMFIA口向FPGA发送控制指令即可,这些指令当然包括OSD的内容及位置信息。

OSD控制

由XC3S250E实现的OSD设计根据接收到的OSD位置及内容信息进行OSD显示,对OSD显示的内容没有任何限制,非常灵活方便。下面以OSD汉字显示为例说明OSD的控制操作。

要正确的显示汉字,就必须将输入的汉字内码转换成对应的区位码。这一功能我们通过函数Uint32 Code_Converse(unsigned char *CodeNPointer),其输入为指针,指向要转换汉字。返回值为该汉字对应的区位码。OSD的显示由函数OSDHZ

isplay实现:

void OSDHZ_ Display{

Uint8 *pFrame

Uint32 pitch

OSDUTIL_Point* loc

Uint32 CodeQ

OSDHZ

ont *font

Uint8 fgColor

Uint8 bgColor

}

其中,Uint8 *pFrame为OSD输出的Buffer缓冲区;Uint32 pitch为每行显示的象素值;OSDUTIL_Point *loc为第一个字符的显示位置;Uint32 CodeQ为要显示汉字的区位码;OSDHZ

ont *font为显示汉字所用的字体;Uint8 fgColor显示汉字的前景色;Uint8 bgColor显示汉字的背景色。

所以,如果需要显示汉字,只需要将汉字进行必要的码制转换,然后将转换后的区位码,给出显示的位置,输出给OSD FPGA即可。当然要显示汉字,汉字字库是必不可少的。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...