- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于TMS320 F28335信号处理板的设计与实现

摘要 介绍了基于TMS320F28335测斜仪系统信号处理板的设计与实现。概述了TI公司TMS320F28335的功能特性和部分外围接口、信号处理板的基本硬件结构及具体功能应用;分析了系统的软件结构、各个模块软件的具体实现方式。整个系统,完成了从模拟信号采样到DSC数字信号处理以及EEPROM的读写和上位机通信过程。利用TMS320F28335的中断技术,实现了各个功能模块分别在各自的中断线程中正常运行,而不会引起相互间的干扰,造成系统混乱。

关键词 DSC;TMS320F28335;AD7656

TMS320F28335是,TI公司最新推出的一款32位浮点数字信号控制器,兼顾了DSP强大的处理核心和MCU丰富的片上外设。由于功能强大、性能稳定可靠,加上丰富的片上资源,在工业控制、环境探测、信号处理等嵌入式领域使用较为广泛。本文首先介绍了TMS320F28335的特征和性能以及部分片上资源,然后介绍信号处理板的硬件设计以及硬件中各功能模块的工作方式,最后对信号处理板的软件系统加以详细说明。

1 TMs320 F28335结构特点

TMS320F28335采用高性能静态CMOS技术,具有150 MHz的工作频率。系统组成包括:包含浮点运算单元的CPU、片内存储器、中断管理模块、片内集成外设。TMS320F28335的CPU采用与TMS320F28x相同的32位定点低功耗CPU,但其中包含一个浮点运算单元(FPU),其32×32位的MAC操作及8级流水线技术使程序的执行不用高速存储器也能达到较高的速度。中断扩展模块(PIE)共支持58个外设中断,能够快速响应中断。片上存储器包括最高达512 kB的闪存与68 kB的RAM,代码安全性模块具有128位密码保护,用来保护Flash/OTP和部分SRAM,从而保证了相关寄存器的数据安全。BOOTROM中固化的代码,提供了多种DSC启动方式。

TMS320F28335支持最多88个通用I/O口(GPIO),GPIO的多路开关寄存器(GPIO MUX)可以将一个引脚最多设置成4种可选工作模式:3种独立的外设模式和1种通用的I/O模式,提高了引脚的利用率,使硬件设计时的布线更加简便合理。GPIO0-GPIO63引脚可以连接到8路外部中断,使DSC能够对外部设备进行有效的中断控制。

TMS320F28335内部首次引入了6路直接存储器存取(DMA)模块,为数据在CPU不参与运算的情况下在外设和存储器之间进行传输提供了一种硬件方法,为其他系统函数的执行释放了带宽。另外,DMA可以重新布置内存中的数据,优化CPU处理。DMA模块是基于事件工作机制的,它需要外设中断触发开始数据传输,6个DMA通道可以分别设置中断触发源,并且每个通道包含自己的独立PIE级中断,以便CPU能够控制DMA传输的起始或完成。

同时,TMS320F28335中包含了多种串行通信外设,其中最多可以包括2个CAN通信模块,3个SCI(UART)模块,1个SPI模块和2个McBSP模块,并加入了1个I2C模块。这些外设加强了DSC的通信功能,为多控制器联接提供了丰富的资源。此外,TMS320F28335支持IDLE,STANDBY和HALT这3种低功耗工作方式,并可通过关闭各个独立片上模块的时钟,降低整体功耗,适合于电池供电等低耗电量硬件系统。

2 硬件系统设计

2.1 方案概述

该系统主要功能是DSC通过ADC采样芯片对12路模拟信号进行同时采样。在DSC中进行数据处理后通过异步串行收发器上传到上位机。同时,上位机也可以通过异步收发器向DSC发送预先制定的命令,来控制信号处理板的工作模式和状态。

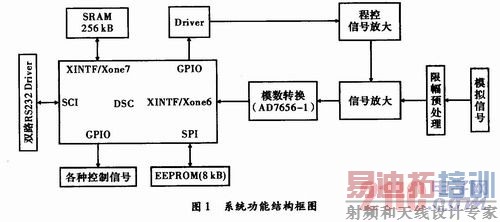

按照功能要求,整个硬件电路可分为3部分:电源模块、数字部分和模拟部分。其功能结构框图如图1所示。

[p]

2.2 电源模块设计

整个处理板的外部输入电压为5 V和±12 V,分别通过对应的电压转换芯片为模拟和数字部分提供不同的电压幅值。对于数字部分,电源模块需要为DSC提供1.9 V的核电压,同时为DSC的外围和其他芯片提供3.3 V的外围电压。本系统选用LT1963AES8集成芯片提供1.9 V,LT1963AEST-3.3集成芯片提供3.3 V。对于模拟部分,系统要求输入ADC的信号幅值范围在±12V内,所以系统分别选用LT1086IT-12和LT11 75IT把输入的±15V电压转换成±12V。

2.3 数字电路设计

数字部分电路主要是以DSC为中心的应用电路。该部分主要是对ADC传送的数据进行处理、存储,同时完成DSC同上位机的通信和数据传输。由图1可以看到,它包含以下几个部分。外围SRAM扩展,EEPROM扩展电路,SCI上位机通信接口电路。

2.3.1 外围SRAM扩展

考虑到TMS320F28335片内的RAM资源有限,加上程序空间和数据空间RAM仅为34 kB,16位数据宽度,从而需要对片内的RAM进行扩展,来满足较大量程序的运行。本系统选用Cypress公司的CY7C1011CV33-12ZSXE集成芯片,利用TMS320F28335提供的XINTF接口完成片外RAM的扩展。

XINTF是TMS320F28335所提供的一个非复用异步总线,用来完成外部异步器件的扩展。XINTF可以映射外设到3个固定的内存映射区域,当外部资源挂接到某个区域时,则需要通过XINTF的一个片选信号来进行外部资源的选定。

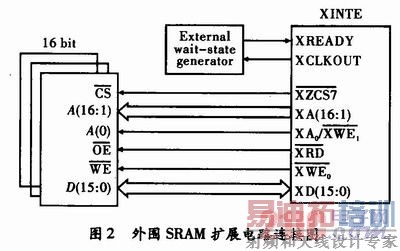

CY7C1011CV33-12ZSXE是一个CMOS的静态RAM存储器,其容量大小为64 kB,16位数据宽度。图2是外围SRAM扩展电路连接图。

如图2所示,本系统选用ZONE7区域作为RAM的外围扩展。DSC通过其XZCS7管脚向片外SRAM发送片选信号。WE信号用来控制DSC对片外SRAM的读写,当DSC的XWEo管脚为低电平,则DSC对片外RAM进行读写操作;XWEo为高电平,同时DSC的XRD管脚为低电平,则为读操作。 [p]

2.3.2 EEPROM扩展

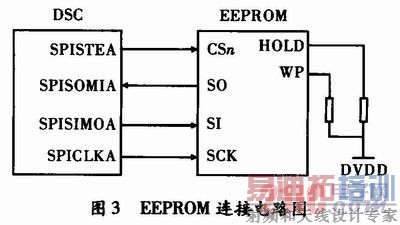

考虑到系统在加电后,需要对一些设备的状态进行一些初始化,而这些初始化的数据在设备运转时又需要不断改变。因此,在设备运转过程中,实时将数据加以保存,以至于设备断电后数据依旧存在。本系统利用TMS320F28335的SPI接口外扩了一个EEPROM保存设备运转时实时获取的初始化数据。本系统选用Atmel公司的AT25160集成芯片。该芯片的容量为2 kB,其宽度为8位数据宽度。模块电路如图3所示。

如图3所示,DSC通过SPISTEA管脚发送片选信号选中EEPROM,通过SPICLKA管脚发送SPI传输时钟,而数据的写入和读出则分别通过SPIS-IMOA和SPISOMIA管脚完成。EEPROM中的HOLD管脚用来暂停与主设备间串行数据传输,WP管脚则用来进行对EEPROM的写保护,如果其为低电平,则主机无法向其写人数据。系统对两管脚输入高电平,保证EEPROM在读写操作过程中一直可以进行而不被中断。

2.3.3 SCI上位机通信接口

为了实现上位机同DSC异步的通信和数据传输,本系统利用TMS320F28335所提供的SCI接口来完成所需要求。SCI是一个2线的异步串行端口,即常说的UART。其数据的收发支持全双工通信,内部收发均有一个16级的FIFO来缓存数据。为了保证数据可靠,SCI提供奇偶校验,数据溢出检测等操作。SCI接口输出信号的电平是LV—TTL电气标准,通过RS232收发转换器加以驱动,获得RS232电气标准的信号,以便上位机接收。

2.4 模拟电路设计

模拟部分电路主要是以ADC为中心的应用电路。其主要实现模拟信号的处理,采集等工作。其中核心部分为AD转换。

AD转换部分,主要是通过数字采样来完成模拟信号到数字信号的转变。本系统选用的ADC芯片是美国模拟电气公司的AD7656。模数转换芯片AD7656是高集成度、6通道6 bit逐次逼近(SAR)型ADC,内含1个2.5 V基准电压和基准缓冲器。该器件的功耗比最接近的同类双极性ADC降低了60%。AD7656在每通道250kb·s-1采样速率下的精度是同类产品的两倍。可以由引脚和软件选择模拟电压范围:10 V或5 V;模拟电源电压范围为4.75~5.25 V,因而大范围的工作电压使其无需电平转换等其他措施便可以直接与DSC相连;提供有并行和串行接口。可以工作在-40~85℃。标准模式5 V供电,250 kb·s-1时的功耗为140 mW,待机时仅为100μW。基于iCOMS技术制造的AD7656可以满足工业领域对分辨率、多通道、转换速率和功耗等方面的较高要求。

AD7656支持和DSC的并口、串口数据传输,通过SER/PAR SEL管脚的高低电平的选择,来控制采样后数字信号的传输方式。当其为高电平,则使用串行传输方式,反之则使用并行传输方式。本系统选用并行传输方式。在具体的转换过程中,每片AD7656内部的6条采样通路可以分为A、B、C共3组,其中每组通路包含2路通路。3组通路可以同时采样,也可以单独采样,而每组内的两条通路同时采样。管脚CONVSTA,CONVSTB,CONVSTC分别用来对A、B、C采样通路进行控制。当一个上升沿电平到达任一管脚,则该管脚对应模数转换的2路通路被启动,开始完成模数转换。当把三管脚连接,3组采样通路,即所有的6条采样通路同时采样。系统选用3组通路同时采样。

当DSC连接有多片ADC时,则需要通过CS片选管脚来进行ADC的选择。当采样开始,BUSY管脚将从低电平变为高电平,在整个采样的过程中,BUSY一直保持高电平,当采样结束,BUSY则从高电平变为低电平,此时DSC就可以开始读取数据。本系统则利用该管脚作为DSC外部中断源的输入管脚。当BUSY上电平由高变低,则通知DSC产生中断,来进行数据的读取。

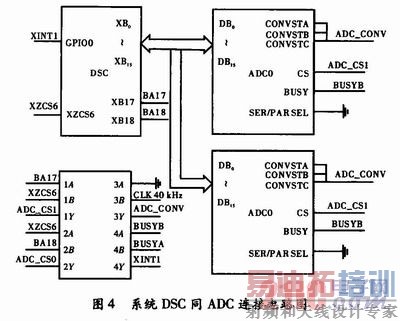

本系统选用2片AD7656完成12路数据采样,通过DSC的XINTF ZONE6把ADC设备映射到DSC上,进行数据传输。通过地址译码和逻辑控制实现2片ADC同DSC的连接。具体结构如图4所示。

图4中左下角为逻辑部分,通过DSC的地址线BA17和BA18完成对ADC的选择。可以得到ADC0和ADC1在DSC中的地址映射为0x180000和0x1400 00。而外部输入40 kHz的时钟,作为ADC的采样频率。两个ADC对应DSC的同一个中断,当任意一片ADC采样完毕,都会引起DSC的中断,从而进行采样数据的读取。 [p]

3 系统软件设计

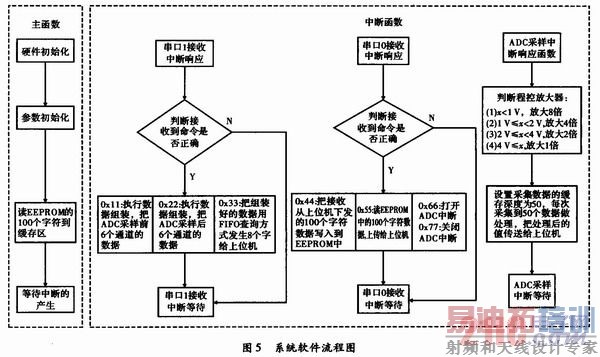

如前所述,整个信号处理板一共有12路模拟信号通路,通过传感器接收到12路模拟信号。2片AD7656把12路模拟信号转换为数字信号传送给TMS320F28335,在TMS320F28335中对这些采集到的数据做相应处理后通过SCI传送给上位机。同时对有必要保存的数据通过SPI接口保存到EEPROM中。整个采集、通信过程由上位机发送相关的命令来加以控制。程序的流程如图5所示。

在主函数中,程序首先完成相应模块的初始化,设定好CPU运行的时钟,选定好各个模块的工作模式,然后读取EEPROM中的设备初始化数据,后进行入等待状态。此时CPU等待ADC采样的数据,当ADC采样过程结束,则进入ADC中断响应函数,在此函数中,主要完成数据的读取,对于小信号,通过程控放大器放大其幅值,然后存储到自定义的缓存区中。两个串口工作方式均由上位机发送命令,从而触发SCI的串口收中断服务函数。然后在中断服务函数中完成对应命令要求。系统选用串口1完成采集数据向上位机的传输,串口0完成向EEPROM发送需保存的数据和一些相关操作。而SCI0和SCI1分别对应DSC外设中断的INT9.1和INT9.3,外部中断XINT1对应INT1.4。程序设置两个串口的传输速率均为38.4 kb·s-1。

在设备工作时,由于SCI1的中断源是上位机的命令发送,系统规定上位机每20ms发送一个数据接受命令,因此SCI1的中断响应周期为td= 20 ms。而由于采样率为40 kHz,因此ADC的中断服务函数响应周期为0.025 ms。系统规定采集一组数据的个数为50,那么采集一组数据的时间即为tc=1.25 ms,所以在一次SCI1中断过程中,ADC会采集16组数据。考虑到串口传输的波特率为38.4kb·s-1,因此传送一个16位的数据时间为tt=0.417 ms。而一组数据采集时间加上串口数据传输的时间为tc+tt=1.667 ms<<td,因此在上位机的发送命令到达时,串口发送寄存器的数据总是准备完毕的,而不会发送随机数据。

4 结束语

所设计的信号处理板以TMS320F28335为核心处理器,利用AD7656完成模拟信号采样的功能硬件平台。TMS320F28335片内集成了丰富的外围资源,通过驱动软件的配置和硬件系统的设计,可以方便、高效地完成大量数字信号的处理和运算。AD7656的6路模拟信号采集和16位高精度的模拟信号采样,较好地完成了模拟信号的数字化转换,减少了模拟信号采样的失真。实验证明,信号处理板所采集到的数字信号的误差值约为1.37 mV,可达14位的采样精度。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...