- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种新型扫频仪的设计

摘要 选用了一种基于DSP与FPGA结构的新型射频扫频仪的设计方案,重点讨论了其扫频信号源的设计。分析了频率合成技术的发展趋势,介绍了PLL技术和DDS技术的原理,并在此基础上给出了以PLL+DDS方式实现的扫频信号源设计。

关键词 DSP;扫频仪;PLL;DDS

频率特性分析仪即扫频仪是在示波器基础上发展起来的一种频率特性图示仪,在工程实践和科学实验中都有着广泛的应用,是现代信息产业中一种重要的电子测量仪器。随着现代电子信息技术的飞速发展,扫频仪也向着数字化、小型化、智能化的方向发展。DSP、FPGA等技术的应用,解决了传统扫频仪体积庞大、操作繁琐、分立元件多、价格昂贵等问题。

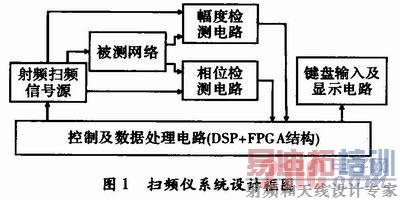

1 扫频仪系统设计

该系统的设计主要由控制及数据处理电路、扫频信号源电路、幅度检测电路、相位检测电路、键盘输入及显示电路构成。控制及数据处理电路采用DSP+FPGA的结构设计,DSP具有强大的数据处理能力、较高的运行速度和稳定的性能,而FPGA容量大,灵活性强,能够进行编程、除错、再编程和重复操作,可以充分地进行设计开发和验证。因此由DSP芯片和FPGA可编程逻辑器件所组成的控制及数据处理模块外围电路少,运算速度快。

DSP作为主控芯片完成整个系统的控制及采集后的数据处理,FPGA的应用使DSP接口控制简单容易实现。编写DSP程序,可以设置频率起止点和步进,完成频率扫描。

2 DDS+PLL结构频率合成法原理

2.1 频率合成技术

频率合成是由一个或几个参考频率源产生一个或多个频率的系统元件的组合。随着技术的进步,尤其是迅速发展的通信领域对于频率精度和稳定度的要求越来越高,频率合成技术也受到了越来越多的挑战。总地来说,频率合成技术的发展经过了3个阶段:(1)直接频率合成技术;(2)锁相频率合成技术(PLL);(3)直接数字频率合成技术(DDS)。

直接频率合成由于采用了大量的混频、分频、倍频和滤波,使得频率合成器体积庞大、成本高、不易调试、指标难以达到需求,已逐渐被模拟或数字锁相环频率合成技术代替。 [p]

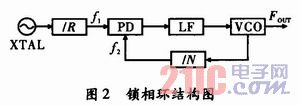

2.2 数字PLL技术

锁相频率合成是利用锁相环路(PLL)技术实现频率的加、减、乘、除,主要由鉴相器(PD),环路滤波器(LF)和压控振荡器(VCO)组成。锁相环原理如图2所示。

PD检测f1与f2相位差,输出平均值与该相位差成比例的直流电流。PD产生的脉冲电流经过LF产生调节电压,该电压驱动VCO来增加或减小输出频率直到PD平均输出为零。输出信号FOUT为

![]()

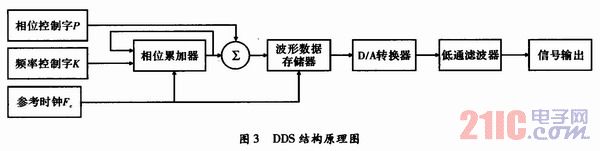

2.3 DDS技术

DDS技术从相位的角度出发直接进行频率合成,能够实现较高的频率分辨率和较快的频率转换时间,典型的DDS由相位累加器、波形存储器、数模转换器、低通滤波器和参考时钟FC这5部分构成。其结构原理框图如图3所示。

经过对频率控制字K的线性累加,最终得到其输出频率FOUT与时钟频率FC之间的关系

![]()

其中,N为相位累加器的位数。

当K=1时,得到DDS的频率分辨率为FC/2N。DDS技术有多种硬件实现方式,为了达到功耗低、集成度高且便于调试的设计目标,现代频率合成系统常采用专用的DDS芯片完成设计。

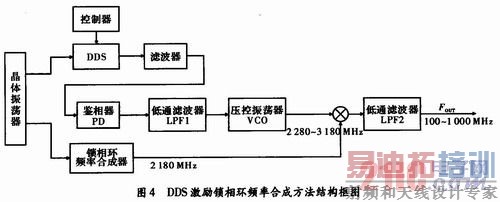

2.4 DDS+PLL结构的频率合成法

由PLL工作机理可知,当输出频率和分辨率越高时,倍频次数N很大,相位噪声恶化。而全数字结构的DDS也有不足:输出频率低,输出谱中杂散多,故难以应用于射频频率段。适当地组合PLL和DDS技术实现优势互补,可以使合成信号兼顾两者的优点,DDS+PLL频率合成主要有3种:(1)DDS激励锁相环;(2)PLL内嵌DDS;(3)PLL与DDS环外混频。 [p]

DDS激励锁相环方式电路简单,但是DDS的杂散和相位噪声在带内被恶化,其频率分辨率也会由于PLL的倍频作用下降到原来的1/N。PLL内嵌DDS难点在于系统中的带通滤波器很难实现,杂散抑制也难以获得比较高的指标。设计要求实现100~1 000 MHz的全程扫频信号源,而环外混频方式只能在一个较窄的频率范围内实现。综合考虑成本及电路实现的难易程度,该方案选择DDS激励锁相环的方式实现射频扫频信号源的设计。由于输出的频段较宽,将频段搬到较高的频段实现,降低相对带宽,然后下混频得到所需频段。实现原理框图,如图4所示。

3 扫频信号源电路设计

设计使用晶体振荡器,一路由锁相环频率合成器产生2180 MHz信号作为混频射频信号,可以选择博威公司的固定锁相频率源MPS2180;另一路由主控芯片DSP控制DDS产生71.25~99.375 MHz的信号,经过滤波之后由PLL电路锁相至2 280~3 180 MHz。低通滤波器(LPF2)的作用是滤除混频后产生的高频分量,采用Mini_Circuits公司的低通滤波器LFCN-1400,通带范围DC~1 400 MHz,在1 000 MHz时的插入损耗为0.41dB。

AD9959是Analog Devices公司生产的一款高采样频率、高精度的DDS芯片,由4个直接数字频率合成器内核构成,每个通道均可提供独立的频率、相位和幅度控制。最高采样频率500 MHz,最高输出时钟频率250 MHz,频率分辨率可达0.12 Hz,能够满足系统的设计要求。设系统时钟为Fs,FTW为频率控制字,则DDS输出频率与控制字的关系为

![]() [p]

[p]

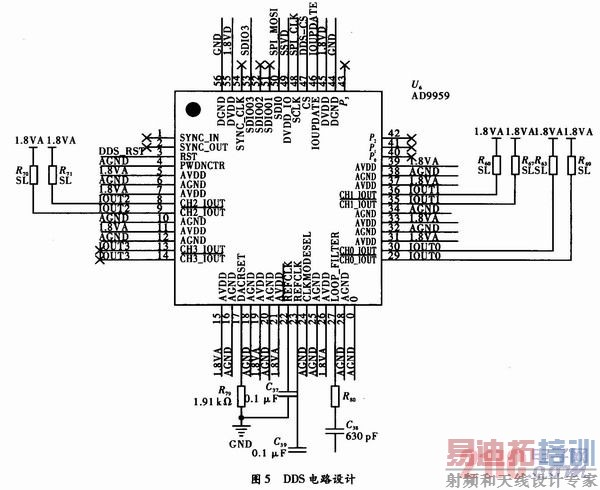

系统选用25 MHz有源晶振,通过设置寄存器中的倍频参数,使AD9959内部的锁相环电路倍频产生500 MHz的系统时钟,这一设置在DDS上电复位后完成。参考AD9959的技术手册,设计电路如图5所示。

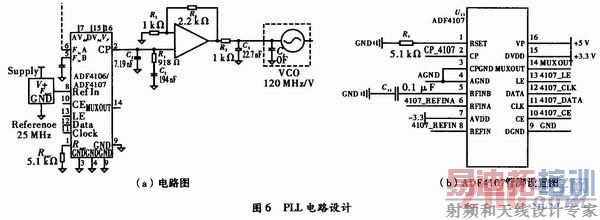

设计锁相环电路,对DDS输出信号完成32倍频,频率步进为10 Hz。后续混频电路将该路信号作为本振信号,所以其相位噪声和杂散指标对最终输出信号的相位噪声以及杂散有着直接的影响。考虑鉴相频率范围、相位噪声等指标,设计选用Analog Devices公司的PLL频率合成器ADF4107。ADF4107由低噪声数字鉴频鉴相器、精密电荷泵、可编程参考分频器、可编程A和B计数器以及双模预分频器(P/(P+1))组成。A(6位)、日(13位)计数器与双模预分频器(P/(P+1))配合,可实现N分频器(N=BP+A)。此外,14位参考分频器(R分频器)允许PFD输入端的REFIN频率为可选值。如果频率合成器与外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环。ADF4107最高鉴相频率为104MH z,相噪基为-219 dBc/Hz,采用ADIsimPLL软件可以方便的仿真并设计出外部锁相环路滤波器。

4 结束语

该扫频仪系统采用DSP+FPGA结构的设计方案。信号源是设计中的一个重要环节,决定了整个系统的指标和设计复杂度。本文在介绍PLL和DDS原理的基础上选用DDS激励PLL完成射频扫频信号源的设计,充分利用了DDS输出频率的灵活性和高分辨率,以及PLL电路的高输出频率,实现了优势互补。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:道路照明中大功率LED路灯散热方案

下一篇:友尚Maxim

EZCascade&

#8482;技术简化视频显示器设计