- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

LVDS技术在某成像光电跟踪产品中的应用

摘要:针对远距离高速信号传输的需求,提出了利用LVDS传输的实现方法,介绍了LVDS的技术原理和特点,并根据某成像光电跟踪产品的结构组成,详细介绍了该产品中LVDS系统的设计实现,并根据设计及调试过程中曾经出现的问题,总结了终端电阻匹配、通道设计、印制板布线等方面的设计要点及注意事项。通过内外场试验,验证了该产品LVDS通讯设计,不仅解决了高速率、大容量、长距离的图像数据传输问题,并具备良好的环境适应性及电磁兼容性。

关键词:LVDS;差分信号;数据传输;噪声

在当今电子设计领域,由集成电路芯片构成的电子系统朝着大规模、小体积、低电压、高速度的方向飞速发展,导致电路的布局和布线密度变大,同时信号的频率仍在不断提高。采用降低电压的办法不仅可以减少高密度集成电路的功率消耗和芯片内部的散热,有助于提高集成度,而且可以提高信号频率、降低信号间的串扰,是集成电路发展的一个方向。而采用LVDS(Low Voltage Differential Signaling)传输则可以有效克服共模噪声,可用于远距离高速信号传输。

1 LVDS技术简介

LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mb/s的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。LVDS在两个标准中被定义:IEEE P159613(1996年3月通过),主要面向SCI(Scalable Coherent Inteface),定义了LVDS的电特性,还定义了SCI协议中包交换时的编码;ANSI/TIA/EIA-644(1995年11月通过),主要定义了LVDS的电特性,并建议了655 Mb/s最大速率和11 923 Gb/s的无失真通道上的理论极限速率。在两个标准中都指定了与物理通道无关的特性,这保证了LVDS能成为多用途的接口标准。

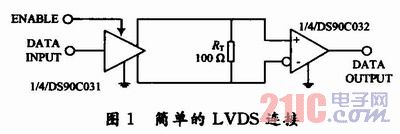

图1给出了典型的LVDS互连方法。这里使用的是DS90C031 LVDS驱动器芯片和DS90C032LVDS接收器芯片,其中DATA INPOUT和DATA OUTPOUT是TTL电平。驱动器和接收器主要完成TTL信号和LVDS信号之间的转换。LVDS驱动器由一个驱动差分线对的电流源组成,通常电流为3mA。LVD8接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约300 mA的电压。当驱动器翻转时,它改变流经电阻的电流方向,接收器产生有效的逻辑“1”和逻辑“0”状态。

应用LVDS具有许多优势:

(1)高速率。由于LVDS逻辑状态间的电压变化仅为300 mV,因而能非常快地改变状态。例如当信号电平在333 ps内变化300 mV时,压摆率仅0.9 V/ns,低于将信号失真和串扰减到最小时的标准压摆率1 V/ns。如果使用上升和下降时间不大于比特宽度2/3的老标准,那么具有333 ps跃变的信号能在1 Gb/s下工作,仍保有很大的余地。

(2)低功耗。随着工作频率的增加,LVDS的电源电流仍保持平坦,而CMOS和GTL技术的电源电流则会随频率增加而呈指数上升,这得益于使用恒流线路驱动器。电流源把输出电流限制到约3.5 mA,同时也限制跳变期间产生的任何尖峰电流。由于没有尖峰电流,就有可能获得1.5 Gb/s的高数据率而不明显增加功耗。恒流驱动输出还能容忍传输线的短路或接地,而不会产生热问题。LVDS降低了终端电阻压降,因此还降低了电路的总功耗。

(3)噪声性能好。LVDS产生的电磁干扰低,这是因为低电压摆幅、低边沿速率、奇模式差分信号,以及恒流驱动器的Icc尖峰只产生很低的辐射。传输通路上的高频信号跳变产生辐射电磁场,场强正比于信号携带的能量,通过减小电压摆幅和电流能量,LVDS把该场强减到最小;差分驱动器引入了奇模式传输,在传输线上流过大小相等、极性相反的电流,电流在该线对内返回,面积很小的电流回路产生最低的电磁干扰;当差分传输线紧耦合时,串入的信号是作为共模电压出现在接收器输入的共模噪声中,差分接收器只响应正负输入之差,因此当噪声同时出现在2个输入中时,差分信号的幅度并不受影响。共模噪声抑制也同样适用于其他噪声源,比如电源波动,衬底噪声和接地回跳等。

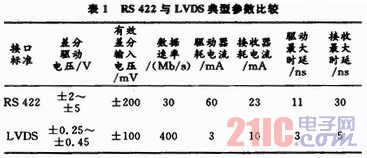

(4)具有故障安全(fail-safe)特性确保可靠性。LVDS驱动器和接收器还能实现热插拔,因为恒流驱动解决了损坏问题。另一特点是接收器的故障保护功能,它能防止在输入引脚悬空时产生输出振荡。除上述各种优点外,LVDS只需要简单的端接电阻。这些电阻可以集成到芯片之中,与每条传输线配备多个电阻和电容元件相比,大大降低了所需的费用。另外,LVDS能容忍传输线通路微小的阻抗失配,只要差分信号在紧耦合的传输通路中通过平衡不连续处,信号仍能保持其完整性。非阻抗受控连接器、电路板过孔和芯片封装对差分信号的影响要比对单端信号的影响小得多。表1给出了RS 422与LVDS之间的简单比较,LVDS的优势是显而易见的。

[p]

2 LVDS在某成像光电跟踪产品中的应用

2.1 系统应用简介

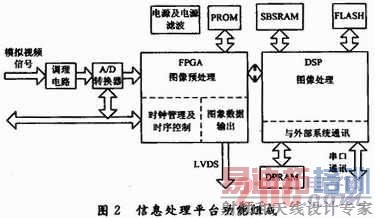

某成像光电跟踪产品信息处理平台采用FPGA+DSP的设计框架,结构框图如图2所示。

该信息处理平台在FPGA和DSP外围增加调理电路、A/D装换器、PROM、SBSRAM、DPRAM、FLASH、电源及电源滤波电路等。FPGA+DSP架构最大的特点是结构灵活,适于模块化设计,能有效地提高算法效率,因而非常适用于成像系统的信息处理。从图2可以看出,该系统通过FPGA,利用LVDS标准电路设计完成图像数据的输出。在该系统中,LVDS有三路差分输出,其中两路传送数据(DA,DB),一路传送时钟(C)。传送格式的要求如下:DA(DAX)为发送16位数据线,传送系统给图像采集设备的所有数据。包括每帧开头发送一个帧计数,帧正程发送图像数据(实时图像数据、滤波图像数据及二值像数据,按DSP要求传送)。图像数据为12位或14位,按需要传送。16位数据的分配如下:最高位为奇偶校验位,“1”表示奇数,“0”表示偶数;次高位为正逆扫信号,“1”表示正扫,“0”表示逆扫;在每帧的开头,图像数据输出之前,添加2个验证字——FDB18540,作为接收方判断每帧数据传送的起始点;帧正程开始后,传图像数据14位,如传的是12位图像数,则其14,13位填0,后12位为图像数据。

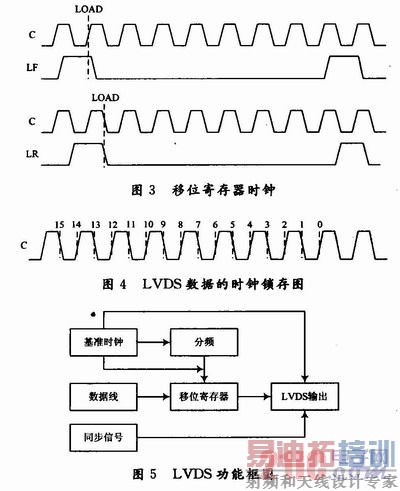

DB(DBX):发送同步信号,每字同步,与首数据最高位同时发出,宽度为半个时钟C(CX):时钟信号,始终保持。在LVDS设计实现过程中参考XAPP233的设计方法,16位数据通过并转串移位寄存器进行移位处理,将偶数位锁存于传送时钟的上升沿,奇数位锁存于传送时钟的下降沿。其输入/输出采用DDR技术,保证双沿触发。移位寄存器时钟示意图如图3所示。最终输出数据的时钟锁存的位置如图4所示。LVDS电路功能框图如图5所示。

[p]

2.2 系统中LVDS设计的要点

该系统中LVDS应用于FPGA+DSP的高速数字处理平台,在设计及调试过程中,曾出现由于终端电阻匹配不当带来的噪声较大的问题、由于通道选择不当带来的信号畸变问题、以及印制板布线不当带来的信号串扰及噪声等问题,通过这些实际问题的解决总结了以下几点。

2.2.1 终端电阻

不管使用的LVDS传输通道是PCB线对还是电缆,LVDS要求使用一个与通道相匹配的终端电阻(100±20)Ω,以防止信号在通道终端发生反射,同时减少电磁干扰。该电阻终止了环流信号,应该将它尽可能靠近接收器输入端放置。该系统使用了两个阻值各为50 Ω的电阻串联,并在中间连接点通过一个电容接地,很好地滤去了共模噪声。

2.2.2 通道(电缆和连接器)选择

使用受控阻抗通道,差分阻抗约为100 Ω,不会引入较大的阻抗不连续性;当电缆长度小于0.15 m时,大部分电缆都能有效工作,当电缆长度在0.15~10 m之间时,CAT3(Categor 3)双绞线对电缆效果好(本系统采用该设计),当电缆长度于10 m,并且要求高速率传输时,建议使用CAT5双绞线对。

2.2.3 印制板设计

尽量使用多层板设计(该系统最终采用8层PCB板),保证LVDS信号、地、电源、TTL信号分处于不同的PCB层,或者至少处于不同的分区;使TTL信号和LVDS信号相互隔离,最好将TTL和LVDS信号放在电源/地层隔离的不同层上;使LVDS驱动器和接收器与LVDS端间连接尽可能短。电源层和地层应尽可能使用粗线。

2.2.4 板上导线

微波传输线(microst rip)和带状线(stipline)都有具备良好的性能;前者一般具备更高的差分阻抗,不需要额外的过孔,后者则在信号间提供了更好的屏蔽。

2.2.5 差分线对

差分线对使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开集成芯片后立刻尽可能地相互靠近(距离小于10 mm),这样能减少反射并能确保耦合到的噪声为共模噪声。使差分线对的长度相互匹配以减少信号扭曲,防止引起信号间的相位差。而且2条差分线之间应尽可能保持平行,以避免差分阻抗的不连续性。不要仅依赖自动布线功能,而应仔细修改以实现差分阻抗匹配并实现差分线的隔离。尽量减少过孔和使用90°折线来改变线迹走向,避免其他引起线路不连续性的因素。

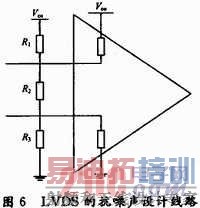

2.2.6 抗噪声设计

如果电缆感应到的噪声超过LVDS接收器内部线路设计的容限,接收器就会不确定地开关或振荡。在本系统中通过外加电阻来提高噪声容限,如图6所示。图6中R1,R3是可选的外接电阻,用来提高噪声容限,R1,R3取12 kΩ,R2取100Ω。

3 结语

该系统经过内场的高低温、振动、电磁兼容等试验,同时经过外场绕飞、系留及靶试。内外场试验表明,某成像光电跟踪产品利用LVDS稳定可靠地进行了图像数据的传输及测试,解决了高速率、大容量、长距离的图像数据传输问题,并具备良好的电磁兼容性。另外,该项技术不仅在某成像光电跟踪产品中得到可靠验证,目前还被推广应用到其他数据传输系统中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:大功率LED心情灯的设计制作

下一篇:基于TMS320F2407的主动振动控制系统