- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

讨论电容摆放位置

解析一下。帮帮忙搭救啊。

你看的是什么资料?讲的挺详细的,能否发我一份?whylove0707@163.com

谢谢,找到了

从平面到芯片,这里是电容的天下了。芯片周围很多的去耦电容。

1 ]4 h! U; S& L1 . b从小电容到大电容先介绍一下,小电容通常作为去除高频噪声(这里有频率使用范围问题,但是我没详细研究,说不出来,只是知道),大电容滤除低频(也有储能作用)。

1 {2 B& c- V0 M4 Z# @电容去耦的一个重要问题是电容的去耦半径,小电容的去耦半径很小,通常是优先最靠近芯片管脚,大电容可以放在外面,他的去耦半径比较大。(当然,能靠近,尽量近,可惜一般BGA下太多的小电容,你不太可能放的下,只能稍微往外放)

6 b% V. S$ W" m. M(不同的电容,谐振频率不同,去耦半径也不同,这个是原话)# B5 I# i' j/ C" A; i7 G. C

还有一点要注意,在放置时,最好均匀分布在芯片的四周,对每一个容值等级都要这样。通常芯片在设计的时候就考虑到了电源和地引脚的排列位置,一般都是均匀分布在芯片的四个边上的。因此,电压扰动在芯片的四周都存在,去耦也必须对整个芯片所在区域均匀去耦。

$ w; }: E/ j; S2 8 w, W* Z$ e

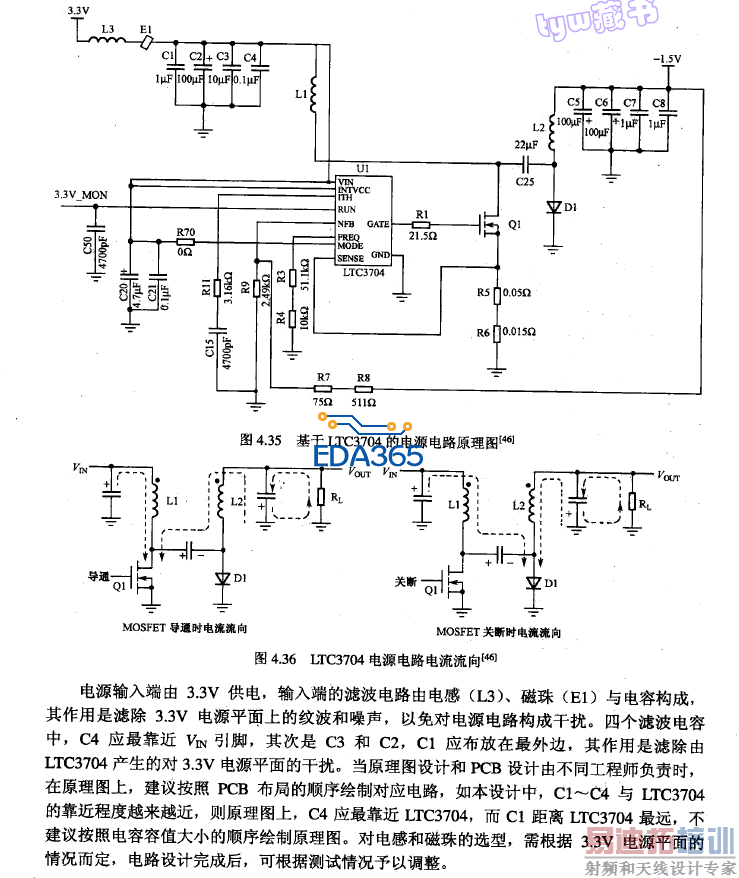

注意:C1(1uF),C2(100uF)C3(10uF)C4(0.1uF),如果按照先大后小的规则,应该是C2,C3,C1,C4依此靠近芯片的Vin管脚,但是这个书为什么会要C1在最外面呢?

小电容的去耦半径小,要尽量靠近芯片放置。大电容的去耦半径大,可以放的稍微远一点。

先说明,问了高手

C1.C2与前面的电感磁珠形成滤波器,所以才会把12这样放

是啊,对你负责啊

8楼兄弟是对的。

LC滤波和单纯的电容滤波不一样。

L3和C1看成一个整体.

呵呵,此贴目的是让一些新人,不要一看到一堆电容就一味想着“先大后小”不变的规则布局,还得考虑各个模块功能的差别,希望大家可以通过这个例子认识到这点。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:pads新手dxf问题,谢谢

下一篇:走圆弧线