- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

采用可定制微控制器来优化算法的设计

Atmel公司的CAP可定制微控制器为这种挑战提出了一种可行的解决方案。CAP是一块基于微控制器的系统级芯片,能提供基本的处理能力,以及高密度的金属可编程(MP)数字逻辑块,这些块可以进行个性化,提供类似于DSP或其它专用的功能执行硬件。CAP同时具有合理的开发周期与具有吸引力的单位批量价格的成本好处。专用CAP的开发流程包括基于开发板的仿真步骤,这个开发板使用高密度的FPGA来仿真算法执行功能,这种功能随后硬化在金属可编程模块中。

从全球定位系统到音视频媒体流处理,这些应用都需要实时地执行复杂的算法,很多这些算法都需要遵从定期更新的行业标准。工程师开发这些应用面临的挑战是在单位成本、外形尺寸和功耗,以及严格的成本和开发时间约束下,优化这些算法的执行,这些产品通常是大批量生产。终端用户产品必须能以合理的成本对处理算法进行升级。

硬件/软件的权衡

最佳算法实现的基本经验是,硬件是为了实现更高的性能,软件是为了实现灵活性。实际上,这种经验很难以实际应用。硬件的选择受限于微控制器内核的基本算法函数,以及DSP内核的乘法/累加和线性函数处理,虽然FPGA所具有更高灵活度,但其缺点是外形尺寸、功耗以及批量时的单位成本。可选的标准单元ASIC可以提供更高的性能,但是因为开发时间和成本而常常不能采用。

软件被移植到选用于硬件实现的微控制器或者MCU/DSP组合上。一旦硬件/软件的划分完成以后,再要做出改变将非常难,而且非常耗时,除非是基于FPGA进行批量生产。通常,只有在应用开发的最后阶段软件才可以运行于目标硬件,并确定处理算法的实现是否为最佳。

CAP算法实现流程

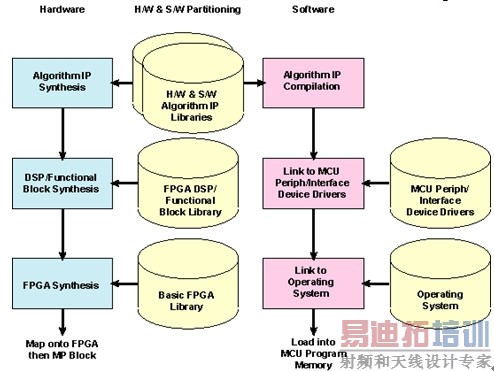

CAP使应用开发工程师能获得FPGA和ASIC两者的优点。CAP应用开发周期的第一阶段使用基于FPGA的库和工具来实现算法的初步硬件/软件划分,然后将基于硬件的功能映射到类似于DSP的架构,或者在FPGA中实现的其他处理单元。同时,微控制器对基于软件的算法处理进行编译,微控制器可以在其地址空间中看到FPGA/MP模块,并采用分布式DMA架构优化功能和存储器模块之间的数据流。图1显示了硬件/软件划分以及使用IP模块库来实现算法的整个步骤,IP模块包含硬件模块以及他们相关的软件驱动程序。

图1:CAP算法硬件/软件划分和实现流程。

在硬件上,首先利用IP库或FPGA提供商的工具来对算法模块进行综合;然后这些再与来自FPGA提供商的库的DSP或类似功能模块进行综合;最后的步骤是将这些高层的结构映射到基本的FPGA架构上,以在CAP开发板上配置FPGA。

在软件上,算法所要求的IP模块被编译,然后与Atmel公司的低层器件驱动程序库链接起来,这些器件驱动程序处理多个外设阻止的操作以及CAP SoC的外部接口。如果有要求,该代码可以链接到操作系统、用户界面以及顶层控制模块来实现这个系统的运行。全部的代码组被加载到用于微控制器内核的程序存储器中,微控制器内核是CAP的中心架构单元。

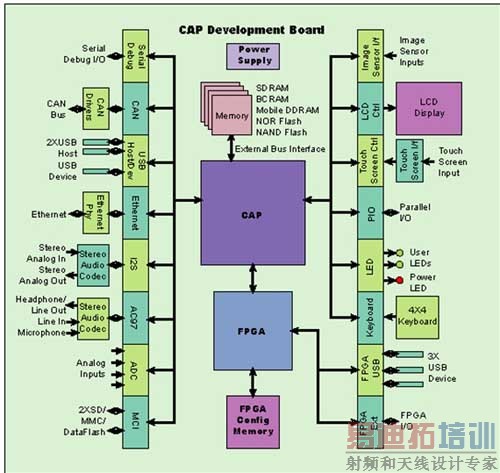

CAP开发板的基本架构如图2所示。设备的固定部分是在CAP芯片中,它以标准的微控制器加片上存储器、外设和接口实现的,所有这些在图中显示为外部连接。各种存储器都可以连接到外部总线接口(EBI)。

图2:CAP开发板。

开发中算法的硬件部分通过其配置存储器映射到FPGA中,软件被加载到微控制器所选择的外部或内部程序存储器中。这样,所配置的开发板以接近运行速度仿真最后的CAP器件,包括非常难以进行仿真的多任务处理进程间通信和中断。这种仿真步骤使算法实现能在真实使用条件下彻底调试。它还使可以利用衡量标准来确定最初的硬件/软件划分以及之后不同模块的综合/编译是否是最优化的。如果要求改进,这些可以使用前面介绍的相同设计流程来实现,除了延长开发时间外,并不会增加额外的成本。可以通过硬件/软件的分割以及硬件/软件实现的多次设计迭代来获得最佳的设计。

CAP金属编程和制造流程

一旦所开发的设备的功能被固定下来,对FPGA进行编程所使用的最终RTL代码被映射到(由Ateml公司或授权的第三方设计公司)金属层来对CAP金属可编程模块进行个性化。苛刻的布局后仿真能确保金属编程CAP的功能与仿真版本的功能相同。

原型很快地生产出来,应用开发人员可以对设备的硬件/软件功能进行最后的验证,特别是用来检查算法是否是最佳的。在最糟糕的情况下,如果原型并不令人满意,从仿真阶段的额外返工成本和时间是合理的,远远低于标准单元ASIC的完全掩模替代的成本和时间。在原型得到批准后,便开始个性化CAP设备的批量生产,使用原型生产的相同流程。

设计师根据现场反馈,并根据任何数据处理算法的升级,基于在金属编程之前开发板的最终FPGA配置的修改,从而可以快速开发出基于CAP的设备改进版本,并比最初的版本成本更低。

本文结论

Atmel公司的CAP可定制化微控制器解决了复杂算法优化的挑战。特别是,它使得算法实现的硬件/软件分割能在接近运算速度和实际使用条件下进行仿真。然后,所选择的实现被硬化到金属可编程模块中,这个模块能提供最佳的性能和功耗,并且非常具有吸引力的批量单位成本。 在不需要额外开发成本的情况下可以对算法实现多次迭代设计,以确定哪一个是最优的。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...