- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA和NiosII的逆变焊接电源控制器

摘要:设计了基于FPGA和NioslI软核的全数字逆变焊接电源控制器,采用变参数PID和改进的I-I型双闭环电流-弧长控制策略,并应用于数字化MIG焊接电源系统中。介绍了该电源控制器各模块的功能及设计方案,分析了MIG焊接电流和弧长的控制问题,并进行了仿真和实际焊接试验。

关键词:FPGA;NioslI;变参数PID;双闭环控制;数字MIG逆变电源

1 概述

脉冲金属惰性气体保护焊(pulsed metal inert gas welding),简称MIG焊。MIG焊在工艺上具有以下优点:焊接保护作用好,焊缝金属纯净,焊接过程稳定,焊缝成形好等。目前,国内逆变焊机多采用以DSP为核心或以MCU+DSP为核心的控制结构。当需要实时采集焊接数据并传送到上位机上时,单个DSP将难以胜任,以DSP为核心控制器的一种改进的处理方案是采用MCU+DSP或者多个DSP配合完成焊接控制和实时通信等环节。该方案无疑增加了系统的成本和复杂程度。

采用高密度的FPGA取代传统的模拟驱动型控制芯片,可大大提高控制器电路设计的集成度,同时提高逆变电源控制器设计的灵活性和电源系统的抗干扰能力、控制精度。但是,FPGA作为核心控制器也存在缺点,其存储能力和软件的扩展接口能力有限。

NioslI软核可以根据用户的要求来定制和拓展,FPGA内部引入NioslI软核采用SOPC的设计思路,可以弥补单独使用FPGA的缺陷,使得基于FPGA硬件逻辑的并行快速性充分发挥的同时,软件接口和扩展通信能力也大大加强。本文采用嵌入NioslI软核的FPGA作为逆变电源的核心控制结构。

2 逆变电源控制器的硬件设计

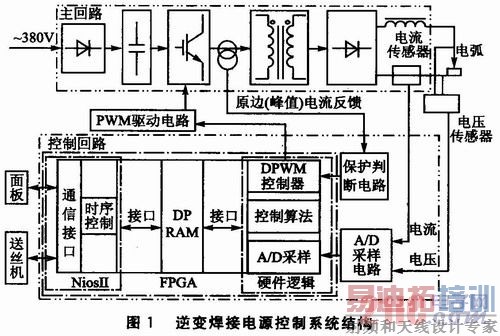

全数字逆变焊接电源控制系统的硬件结构如图1所示。主要分为两部分:焊接电源主回路和控制回路。主回路的工作过程为:380 V工频交流电整流滤波后变为520 V左右直流电,经逆变环节变为高频方波交流电,经中频降压变压器和输出整流-滤波环节后变为低压直流电供焊接使用(受控环节为桥式逆变过程)。控制回路的核心器件为FPGA,其内部设计包括:FPGA硬件逻辑部分、NiosII软核部分,以及DPRAM和接口逻辑。

2.1 FPGA硬件逻辑设计

FPGA硬件逻辑设计主要包括ADC采样控制器、DPWM控制器以及双闭环控制算法的设计。

2.1.1 ADO采样控制器

全数字逆变焊机工作频率为20~40 kHz,采样速度要求较快;为了满足电源输出控制的精度,要求采样精度要足够高。另外,由图1可知,系统需要同时采集电源的输出电压和电流两路信号。采用ADI公司的AD7863。

其转换速率为175 ksps,并行输出接口,转换精度最高为14位,内置两个独立A/D转换器。根据其数据手册中提供的ADC转换时序,可以将ADC控制器分为7个状态:S0,空闲状态;S1,启动转换;S2,A/D正在转换,Busy信号置高电平;S3,转换完成,Busy信号置低,发送读取命令;S4,读取第一个转换值;S5,读完第一个转换值,发送第二个读命令;S6,完成第二个通道的读取,转移至S0。 [p]

根据以上的设计思路,采用VHDL语言描述、以状态机的形式设计ADC控制器。

2.1.2 DPWM控制器

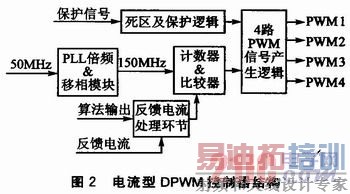

数字PWM(DPWM)控制器作为连接控制算法与焊接电源主回路的桥梁,作用至关重要。在以DPWM方式控制的逆变电源系统中,DPWM一般可以分为电压型DPWM和电流型DPWM两种方式。电流型DPWM反馈电流和锯齿波叠加后,与控制信号直接比较,DPWM信号可以迅速输出电流的变化,动态性能较好,因此本文采用电流型设计方案。

DPWM控制器一般需要满足:占空比可变,而且PWM占空比更新快;有足够的死区时间保证IGBT可靠关断;能快速抑制不正常输出电流的突变,以防止焊接电源负载在短路、焊接电弧、断路之间切换时造成系统不稳定;当出现过流等异常现象时,能快速封锁DPWM驱动信号,保护主回路。

此外,为了避免系统输出出现极限震荡现象,要求DPWM控制信号的分辨率要高于采样分辨率。本设计中,ADC有效采样分辨率设置为10位,采用150 MHz的计数频率和30 kHz的逆变器开关频率,由式(1)可推算出DPWM控制信号的分辨率:

![]()

其中,fCLK为计数(时钟)频率,fSW为逆变器开关频率,![]() 为DPWM控制信号的分辨率。代入实际数据可得,计数上限为5000,即至少13位的分辨率,高于ADC的采样分辨率。综合上述分析,电流型DPWM控制器的结构如图2所示。

为DPWM控制信号的分辨率。代入实际数据可得,计数上限为5000,即至少13位的分辨率,高于ADC的采样分辨率。综合上述分析,电流型DPWM控制器的结构如图2所示。

2.1.3 双闭环控制算法

(1)电流控制方案

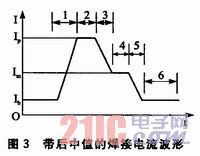

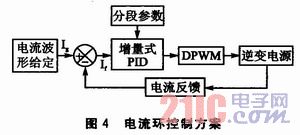

脉冲MIG焊一般采用带后中值的焊接电流波形,如图3所示。焊接过程的要求各阶段电流稳定,且峰值电流Ip、基值电流Ib、中值电流Im以及电流变化斜率都应精确控制,以保证焊缝质量。因此,保证控制脉冲参数的精度为电流控制的基本要求。闭环形式的PID算法最为常用,但是各阶段的电流变化斜率不尽相同,即使反复选择PID算式的kp、ki、kd参数,也只能折中各阶段的控制指标。变参数PID控制则可以分段设定kp、ki、kd参数,优化控制效果。本文采用变参数PID作为控制方案。

根据波形的6个阶段,将PID参数分为6组,分别分段调试取优后存储。工作时控制器根据当前的焊接电流阶段选择最优PID参数,以充分保证焊接电流的各个指标。这里采用增量式PID方案,变参数PID电流环控制方案如图4所示。

[p]

(2)弧长控制方案

焊接电弧的稳定对于焊接质量的提高和保证焊接电源适应不同的焊接工况十分重要。由于焊接电弧电压直接影响弧长的变化,而电弧电压随着焊接电流的改变而变化,因此弧长控制和电流控制是关联的。

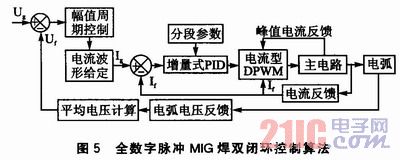

当前对焊接电弧的调节主要有2种方式:以脉冲峰值电流Ip和基值电流Ib均保持不变的I-I方式,以及脉冲电压Up和基值电流Ib保持不变的U-I方式。I-I方式由于Ip和Ib均为恒流外特性,可以达到稳定的熔滴过渡,并且通过控制脉冲电流波形可以精确地控制熔滴过渡行为。但I-I方式是通过调节脉冲频率来实现电弧长度的调节,存在调节速度慢且弧长变化时脉冲周期剧烈变动等缺点。本文采用在不影响熔滴过渡过程的前提下对Ip和Ib进行阈值范围内微调变化的方式,不但可以减小电流脉冲频率变化的剧烈程度,而且可以加快电弧动态调节过程。这样电流控制构成内环,弧长(压)控制构成外环。双闭环控制算法如图5所示。

2.2 NiOSIl软核设计

NiosII是专门针对Altera公司FPGA的32位嵌入式CPU。它是一个完全由Altera FPGA的逻辑单元和嵌入式RAM块实现的RISC结构的软核CPU。NiosIICPU提供3种不同的配置:NioslI/f(快速型)、NiosII/s(标准型)和NiosII/e(经济型)。可以通过SOPC Builder来选择所需的NiosII软核,根据具体的应用需求来定制它的外围设备,还可以通过自定义指令和外围模块来增加NiosII系统的功能。这里考虑到功能需要和FPGA内部资源占用率,选用NioslI/e型CPU。

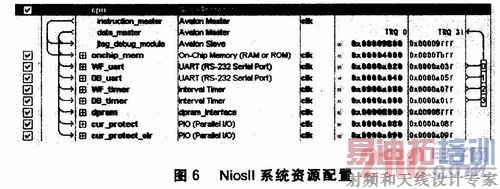

在本设计中,NiosII/e型CPU任务有:与面板通信,将电流波形和其他焊接参数传送到FPGA的DPRAM中,并且读取DPRAM中的焊机数据传送到面板上;负责保护气体起停、快送丝、慢送丝等焊接的时序控制。因此NiosII软核的软件设计包括:与DPRAM接口、焊接时序控制,以及控制送丝机和面板通信。根据上述要求,通过SOPC Builder配置的NioslI软核系统资源如图6所示。

2.3 DPRAM和接口逻辑设计

NioslI和FPGA硬件逻辑之间的数据交换可以采用DPRAM、SPI和SCI等形式。DPRAM采用并行传输,传输速度快,通信协议简单,而且FPGA中一般有DPRAM的宏模块可供使用。因此,本文采用DPRAM作为各种焊接波形数据和工艺参数的存储媒介。采用FPGA内部DPRAM宏模块,只需根据需要修改位数、容量等参数。考虑本设计的需要,DPRAM选择16位,容量为1K字。采用DPRAM作为通信中间环节,关键问题是如何合理解决以下2个问题:

①DPRAM与NiosII的接口。可以通过为NiosII添加I/O口以模拟DPRAM读写时序进行接口,也可以直接利用NiosII中的Avalon总线和DPRAM互连。采用I/O口模拟读写时序速度较慢且浪费FPGA的内部逻辑资源,本文采用自定义逻辑模块将Avalon总线与DPRAM进行连接,根据Avalon总线的读写时序设计接口模块。

②DPRAM与FPGA硬件逻辑的接口。本文结合SOPC Builder帮助文件中给出的DPRAM读写时序,设计简单的逻辑实现接口。

[p]

3 仿真与实验

3.1 ADC控制器仿真

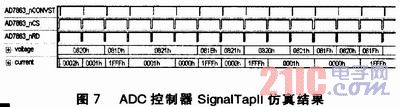

ADC控制器可以使用QuartusII自带的SignalTapII逻辑分析仪进行仿真验证。SignalTapII逻辑分析仪可以直观地观测ADC控制器采集到的当前ADC的转换结果,准确而高效。为了加快仿真速度,对ADC的转换值不加滤波处理;为避免最低位剧烈抖动,仿真时仅仅采用高12位,去掉最低两位的结果。参考电压5 V,将电压通道接到了模拟地(理论值为0000h),电流通道连接到2.54 V左右的模拟电压(理论值为0820h)。 SignalTapII仿真结果如图7所示。

可见,所设计的ADC控制器能够稳定地控制AD7863工作,除了稍有抖动之外(未加滤波环节),采样结果准确可靠。

3.2 DPWM控制器仿真

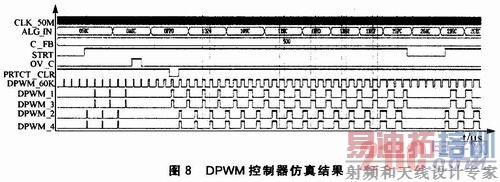

为了验证所设计的DPWM控制器是否合理,在保证仿真有效的前提下做如下约定:保护清除按键和DPWM启动按键信号均以直接数字量置位来代替;将算法输出信号ALG_IN视作给定;反馈电流数字量设为恒值500;死区时间设定为3.0μs,最小脉宽占空比为2.4%。

仿真环境为QuartusII-7.2,仿真结果如图8所示。启动信号STRT有效之前DPWM输出全部封锁,输出均为低电平;STRT有效后,在给定小于最小脉宽时输出最小脉宽,随着给定的增大,脉宽变大;当检测到过流信号(OV_C)时,4路DPWM输出立即置低(即全部被封锁),且置低状态能一直持续到保护信号PRTCT_CLR清除后才结束。可见DPWM的输出严格受控。

3.3 焊接试验波形

3.3.1 静态负载焊接试验

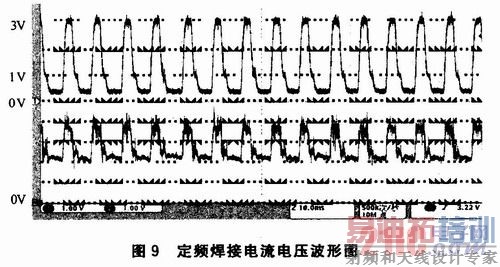

在静态负载条件下,NioslI通过DPRAM给定定频100 Hz和带后中值的脉冲电流。电流脉冲参数为:峰值300 A,峰值时间4 ms;中值100 A,中值时间1 ms;基值电流30 A。采用6段PID参数。实际输出的电流和电压波形如图9所示。

图9中,上面为通道1,波形为输出电流,每格1 V,代表实际焊接电流100 A;下面为通道2,波形为输出电压,每格1 V,代表实际焊接电压10 V。可见,焊接电流波形与给定的脉冲波形(如图3所示)基本一致。

3.3.2 动态负载焊接试验

双闭环控制策略下,死区时间3.0μs,最小脉宽占空比为2.4%。电流脉冲参数为:峰值450 A,峰值时间3 ms;中值150 A,中值时间2 ms;基值电流50 A。6段PID参数。给定平均电弧电压为30 V,保护气体成分为20%CO2+80%Ar,保护气体流量为25 L/min,碳钢焊丝直径为1.2 mm,送丝速度为4.5 m/min。试验结果表明,当焊枪大范围抖动时,为了调节电弧的平均电压以保证焊接电弧稳定,电源系统实时地稳定电弧,且电流脉冲的频率变化均匀,峰值、基值分别随焊枪的抖动而上下微调。

4 结论

本设计采用FPGA+NioslI软核为控制核心,设计了全数字化脉冲MIG逆变焊接电源控制器。试验结果证明:数字化的设计思路增强了系统的稳定性和灵活性;一块FPGA在保证控制器功能的前提下,大大降低了开发成本,缩短了开发周期;在FPGA内部实现6段变参数PID以及改进的I-I电流-电弧双闭环的控制策略,脉冲电流跟踪效果良好,焊接电弧调节稳定,动态性能良好,实际焊接效果出色。本设计的核心逻辑都是基于统一性较好的VHDL语言设计,并采用模块化的设计方案,因此便于推广和移植。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高品质LED供电电源的设计

下一篇:LED灯光系统设计方法