- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的高速数据处理系统设计

随着光纤传感技术的发展,光纤传感器已成功应用于周界入侵探测等安全防范领域。目前,已经应用于光纤微扰动传感器或相似系统的数据处理方案比较多,有DSP、FPGA、FPGA+DSP、labview等多种方案。但是目前的解决方案大多是对信号进行前期处理,实现PGC解调或者是滤波等功能,仅仅对实验方案进行验证,扰动判别和定位等工作需要上传到PC机上进行。

然而,PC机不是专用的数据处理器,与专用数据处理器相比,PC机体积大、功耗大、处理速度慢。而且在通常的实时信号处理中,专业处理芯片外围电路比较少,一般来说一块电路板就可以完成所需功能,功耗大大减少,而且相比PC机庞大的体积,可以使系统更紧凑,节约空间。FPGA由于其高度的并行和灵活的配置特性,以高速、实时、低成本、高灵活性的优点应用于数字信号处理领域。本文叙述了采用FPGA

实现光纤微扰动传感器的数据处理的具体方案,提供了一种高速实时数据处理方法。本系统的主要工作是通过基于FPGA的嵌入式系统,实现数据采集、数据存储、LCD显示、USB数据传输和数据处理,完成光纤微扰动传感的扰动识别和定位功能。

1 系统结构和硬件设计

1.1 系统结构

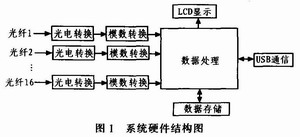

光纤微扰动传感器采用马赫-泽德/马赫-泽德(M-Z/M-Z)混合干涉仪方案作为传感方案。而马赫-泽德/马赫-泽德混合干涉仪方案是通过测量两路光信号到达测量端的时间差来确定扰动位置的一种方案。根据传感方案的特点,本系统应该先将所得的光信号转换为数字化信号,然后再对信号进行处理,所以根据系统的特点,系统结构图如图1所示。

从结构框图中可以看出系统由以数据处理核心,光电转换、模数转换、LCD显示、数据存储和USB通信等外围功能模块构造而成。由于光纤微扰动传感器的传感采用的是光纤,所以首先需要将信号经过光电转换和A/D转换,将信号转换为适于FPGA处理的数字信号。然后,在FP-GA中进行数据处理,判断接收信号是否是入侵行为。如果存在入侵行为,则同时将采集到的信号存入存储器,并在LCD上显示入侵位置;如果没有入侵行为,则在LED上显示正常,采集到的数据释放。USB通信模块只在系统和PC机相连的时候,将存储器中数据上传到PC机中。

1.2 系统硬件设计

马赫-泽德/马赫-泽德混合干涉仪方案将扰动位置求解问题就转化为测量两路信号到达测量端的时间差,因此求扰动点的位置的问题转换为求两路信号的时间延迟估计问题。对于时间延迟估计问题,目前大多采用相关检测方法计算。系统采用相关检测算法,需要进行大量互相关计算。互相关计算的具体实现是由大量的乘法和加法组成的,所以对数据处理速度要求很高。计算量很大,不过比较适合并行计算。系

统的数据处理部分采用的是XC4VSX25,Virtex-4 SX系列是Virtex-4平台中专门为了高性能数字信号处理(DSP)应用解决方案而设计的。XC4-VSX25中含有128个XtremeDSPSlice,而每个XtremeDSPTMSlice包含1个18×18位带补数功能的有符号乘法器、加法器逻辑和1个48位累加器。每个乘法器或累加器都能独立使用。

XC4VSX25中含有多个XtremeDSP Slice,而且FPGA中的XtremeDSP Slice可通过IP核的形式方便地调用。同时XtremeDSP Slice中每个乘法器或累加器都能独立使用,在XC4VSX25中可方便地将乘法器和累加器组合,构成所需要的数据处理结构,所以采用XC4VSX25为系统的数据处理器。

光电转换部分采用PINFET,是目前比较通用的光电转换器件。模数转换模块采用的是12位双通道差分输入SAR型AD7356,结构简单实用。大容量存储模块采用SUMSUNG公司具有200 μs的页写速度的1 GB容量K9K8G08UOM型Flash,可以满足系统的实时性,并能够存储较长时间的扰动信号。LCD模块采用的是3.3 V单电源供电的320x240大屏幕点阵液晶ZXM320240E1,有足够的空间将多路的情况同时显示在屏幕上,而且由于系统选用FPGA的管脚电压为3.3V,可以避免电平转换,电路简洁。USB通信模块采用的是集成了8051单片机的CY7C68013A型USB控制器。

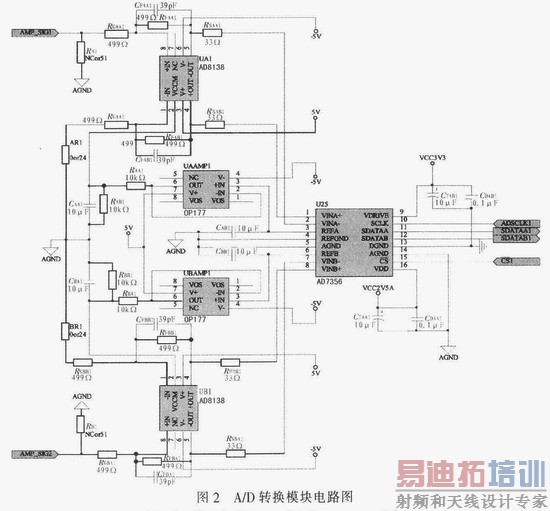

其中A/D转换部分由于系统要求16路.每路12位1~5 M采样速率,并且由于系统的扰动定位算法采用相关检测法,是对时间延迟进行检测,因此需要在A/D转换的过程尽量减小因为转换而带来的时间延迟误差。选用12位双通道差分输入SAR型AD7356,该A/D为双通道型,所以两路信号的转换是同时进行,减小了因转换带来的时间延迟。而且AD7356的采样频率由输入时钟信号决定,因此可以很方便的改变系统的采样频率,满足系统1~5 M的采样速率要求。 [p]

另外,比较各A/D转换器的复杂程度发现多通道(4路或以上)A/D由于其设计的多功能性,导致结构复杂,使用比较繁琐,而AD7356采用16引脚的TSSOP封装,外围电路简单。另外该A/D采用单2.5 V供电,可与FPGA共用电源,使系统的供电系统简洁。而高速A/D转换器的输入是差分式,如图2所示,使用AD8138单端至差分转换驱动AD7357的差分输入。

系统中有模拟地和数字地之分,同时A/D转换器由于其特殊性,处于模拟地和数字地之间,所以对于AD7357的管脚连接应注意。AD7357的REFA和REFB管脚需要通过10μF的退耦电容连接到REFGND管脚,而REFGND管脚则需要连接到AGND管脚。而A/D转换器要求AGND和DGND之间

的电平相差不能超过0.3 V,所以需要将AGND和DGND连接起来。为了避免模拟电路和数字电路之间的干扰,一般情况需要对地分割,但是本系统有多个A/D转换器,所以使用统一地,通过对器件合理摆放来减小模拟和数字电路间的干扰。 [p]

2 数据处理设计

2.1 数据处理结构

本系统的数据处理结构如图3所示,首先是采集一定长度的信号存储到双口RAM中,然后经过扰动识别决定是否需要进行扰动定位计算。由于扰动识别和定位计算需要将采集到的数据保存到数据处理完毕,所以FPGA中的双口RAM要有足够的空间,在数据处理的同时继续存储采集到的数据。而在工作时,由于采用了高速的AD7356,最高采样速率可以达到5 M/s,所以要求扰动识别和定位计算速度足够快。

扰动识别部分由于采用的是平方后积分并与阈值比较的模式,属于顺序计算,耗时不多,数据处理耗时的主要部分是扰动定位计算。扰动定位计算采用的是相关计算,其所消耗的时间在计算速度固定时,由数据长度L和相关长度(移位次数)n决定。进行一次相关计算的计算量为Ln次乘法和(L-1)n次加法。

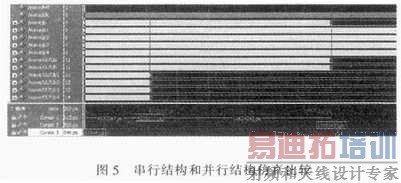

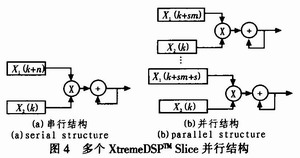

在FPGA数据处理方面,当资源成本为主要制约时,根据速度要求,采用串行结构实现或DA结构实现;当速度成为主要制约时,则根据资源成本因素,采用并行结构实现或DA结构实现。而DA结构主要是通过对资源合理的利用来减小资源的空闲时间,从而提高系统的速度。但是对于本系统,在计算过程中各资源几乎是在全速运行,DA结构并不能提高系统的速度,所以需通过并行结构(图4)来提高系统运行速度。通过图4可以看出,如果采用串行结构,整个相关计算由1个XtremeDSP Slice(或者1个单核处理器)完成,每完成一次互相关运算,整个数据段移位一次,共移位n次。因此为了及时处理采集到的数据,串行结构的计算速度至少是采集速度的n倍(根据传感长度不同,n最大可达2 500)。而AD7356最高采样速率可以达到5 M/s,因此计算速度过快,单个XtremeDSP Slice不可能完成。而如果采用s个XtremeDSP Slice并行结构,则一次互相关计算相当于串行结构时的s次互相关计算,而本来需要移位n次完成的计算,现在只需要m(图4中变量m=n/s)次移位,每次移位s,即可完成。因此,每个XtremeDSP Slice的计算速度为采集速度的m倍,可以有效减少对计算速度的要求。

[p]

2.2 仿真实验结果

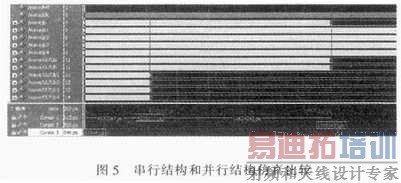

为了比较串行结构和并行结构的计算速度,在Xilinx 7.1ISE平台中(Virtex-4器件的最低版本要求),选用Virtex-4系列的XC4VSX25器件,用Verilog HDL语言设计串行结构和并行结构,并在ModelSim中对两种结构进行仿真比较。由于仿真时间长度的限制,采用5位128长度的三角波模拟采集到数据,并将XtremeDSP

Slice的计算速率设定在250 M/s,仿真波形结果如图5所示。

从图5中可看出,采用串行结构,计算耗时约为15.8 ms,而采用4个XtremeDSP Slice的并行计算结构,计算耗时约为4.2 ms。从仿真结果的比较可知,串行结构耗时约为并行结构的4倍。因此,在本系统中并型结构的计算速度是正比于并行度的,这与理论上并行计算可以成倍减少计算时间的分析一致。

3 结束语

通过以XC4VSX25为核心的嵌入式系统,实现数据采集、数据存储、LCD显示、USB数据传输和数据处理,完成光纤微扰动传感的扰动识别和定位功能,具有高速、实时、低成本、高灵活性的优点。本系统利用系统内特有的硬件结构XtremeDSP Slice实现高效高速的数据处理,同时在ISE软件中XtremeDSP Slice以IP核形式使用,无需自己构造乘法器和加法器,既节省了大量FPGA资源又大大减少开发难度。通过仿真比较可以看出,本系统中并型结构的计算速度是正比于并行度的,因此可以通过提高并行度来提高系统的计算速度,满足高速实时的数据处理要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...