- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

H.264算法的DSP移植与优化

摘要:在TMS320DM643平台上实现H.264基档次编码器的移植与优化显得格外实用和必要。基于对DSP平台的结构特性和H.264的计算复杂度分析,主要从核心算法、数据传输和存储器/Cache使用几方面对H.264编码器进行了优化。实验结果表明,对于CIF格式的视频序列,优化后的H.264编码器能够达到每秒高于24帧的编码速度,满足了视频处理对于实时性的要求。

关键词:H.264编码;TMS320DM643;算法优化

0 引言

针对视频通信中传输带宽或存储容量与视频质量的矛盾,ITU-T的VCEG和ISO/IEC的MPEG联合制定了低码率视频压缩标准H.264。相对于以往的标准,H.264除了增强了网络适应能力外,大幅度提高了压缩编码效率,在相同的码率下能够获得更高的主客观质量。2003年5月,H.264/AVC标准正式推出,正式名称为H.264 MPEG-4 part 10 AVC(Advanced Video Coding),以下简称为H.264标准。

1 编码器

H.264仍采用图像预测和变换编码相结合的编码结构,编码器采用的仍是变换和预测的混合编码法。输入的帧或场以宏块为单位被编码器处理。首先,按帧内或帧间预测编码的方法进行处理。如果采用帧内预测编码,其预测值PRED是由当前片中前面己编码的参考图像经运动补偿(MC)后得出,与解码所需的一些边信息(如预测模式量化参数、运动矢量等)一起组成一个压缩后的码流,经NAL(网络自适应层)供传输和存储用。为了提供进一步预测用的参考图像,编码器必须有重建图像的功能。因此必须使残差图像经反量化、反变换后得到。为了去除编码解码环路中产生的噪声,为了提高参考帧的图像质量,从而提高压缩图像性能,设置了一个环路滤波器。即重建图像可用作参考图像。

1.1 视频编码的硬件结构

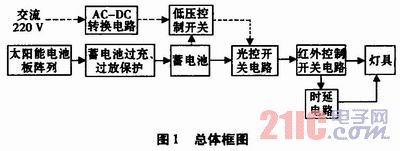

H.264视频编码器硬件结构如图1所示。FLASH模块用于存放程序,EEPROM用于存放编码系统的初始化配置信息和系统MAC层地址。片内SRAM用于缓存当前正在处理的宏块数据,以及一些频繁调用的数据段和程序段。外接存储器SDRAM主要用于存储原始帧、参考帧和重建帧的源数据。片内、片外存储器之间的数据传输借助EDMA在后台操作,这样可并行处理数据传输和运算操作,提高效率。

1.2 DSP芯片简介

DM643的EDMA可在64个独立的通路上,提供超过2GB/s的I/O带宽。此外,运用两级片内高速缓存Cache和64位外部存储器接口(EMIF),可方便地实现与同步/异步存储器的无缝连接。DM643还集成了多种新型的片内外设,以适应于媒体数字化处理和网络通信的应用:(1)三个可配置的视频端口,提供和通用视频A/D和D/A芯片的无缝接口;(2)压控晶体振荡器插值控制端口,用于与MPEG-2传输流接口时的系统时钟恢复;(3)管理数据输入输出模块,用于列举系统中的物理层设备并监视它们的连接状态。 [p]

1.3 H.264编码算法的主要特征

H.264编码算法进行了一系列的改进和扩展,明显改善编码效率的特征如下:

(1)网络适配层NAL:传统的视频编码编完的视频码流在任何应用领域下都是统一的码流模式,视频码流仅有视频编码层。(2)自适应块大小编码模式:H.264允许使用16×16、16×8、8×16、8×8、8×4、4×8、4×4等子块预测和编码模式,采用更小块和自适应编码的方式,使预测残差的数据量减少,进一步降低了码率。(3)多帧运动补偿技术:传统的视频压缩编码采用一个或两个解码帧作为当前预测的参考帧。

2 算法优化

如上所述,运动估计,整数余弦变换/反整数余弦变换,量化是H.264编码器中最耗时的部分。因此,这3项是优化的主要对象。

2.1 运动估计

视频序列图像在时间上存在很强的相关性,采用运动估计和运动补偿技术可以消除时间冗余以提高编码效率。运动估计粗略分为全局运动估计、基于像素点运动估计、基于块运动估计和基于区域地运动估计。

H.264标准采用块运动估计匹配算法,它包含匹配原则(主要有MAD、MSE和NCCF三类),搜索范围,搜索方案等。但是搜索算法是影响块匹配算法性能的主要因素。在整像素的运动估计中,采用了基于菱形搜索算法。

2.2 CPU与缓存之间的数据传输

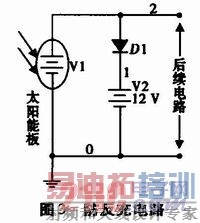

DM643有一个两级(Level2)高性能Cache结构,它们都有16 kB的独立存储器,并且均可以被存入两级Cache中。两级Cache可以被设置为Cache,SRAM或者Cache,SRAM的一部分。CPU与Cache之间的数据读取过程如图3所示。

[p]

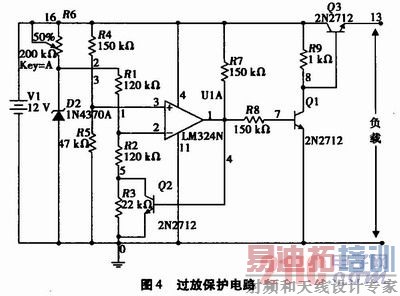

2.3 ICT/反ICT和量化

原始的ICT/IICT和量化算法不能够充分发挥DSP的并行优势,以至于8个功能单元在编码的过程中都处于闲置状态,存储器中的数据被频繁重复的访问也导致了DSP运行效率的降低。在图4所示中,提出对于ICT/IICT和量化部分的算法图例,一个宏块中所有基于4×4块的IC-T/IICT变换都能够同时执行,这充分利用了DSP的8个功能单元。实验结果表明,经量化后,计算一个ICT/HCT的4×4块仅仅需要12个平均周期。这一优化不但提高了算法的速度又显著地降低了码流大小,使视频信号的实时处理成为可能。

3 实验结果分析

在600 MHz的TMS320DM643平台上,通过开发软件CCS载入开源代码X264构架对CIF格式的5个视频序列(Akiyo,News,Foreman,Footba-ll,Mobile)进行了相关实验。在这5个视频序列中,Akiyo和News序列有较低的运动级别,背景变化画面人物运动幅度不大,而Foreman和Fo-otball有高的运动级别,运动剧烈有场景切换,最后一种Mobile序列则有复杂的背景。表1列出了在量化步长(QP)为25的情况下,原始H.264编码器和优化后的H.264编码器之间的对比结果。从中可以看出,原始的编码器的编码速度是2~3 f/s,而优化后的编码速度是前者的10倍多。

4 总结

本系统采用TMS320DM643作为的核心处理器,这款DSP芯片主要是为实现低功耗、高性能而专门设计的定点DSP芯片。它具有高度灵活的可操作性和高速的处理能力,先进的多总线结构,主要应用在通信、数据采集等系统中,特别在实时性方面效果最佳。

本设计借助开源代码X264在CCS开发平台进行试验,测试了编码优化前后的帧率等各种性能,旨在寻求更高效的视屏编码算法。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...