- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

掌握音频协议和标准

过去几年里,音频技术取得了巨大进步,特别是在家庭影院和汽车音响市场。汽车中的传统四扬声器立体声系统正逐渐被多声道多扬声器音频系统所取代。在印度,带双扬声器立体声系统的电视机现已被带5.1多声道的家庭影院系统所取代。

当今的音频设计挑战在于如何模拟实际的声音并通过各种音频设备进行传送。声音可以来自任何方向,实际上,我们的大脑能够计算并感知声音的来源。例如,当战斗机从一点飞到另一点时,它所产生的声音实际上来自无数个位置点。但是,我们不可能用无数个扬声器来再现这种音频体验。

利用多声道、多扬声器系统和先进的音频算法,音频系统能够惟妙惟肖地模拟真实声音。这些复杂的音频系统使用ASIC或DSP来解码多声道编码音频,并且运行各种后处理算法。声道数量越多,意味着存储器和带宽要求越高,这就需要使用音频数据压缩技术来编码并减少所要存储的数据。这些技术还能用来保持声音质量。

与数字音频一同发展的还有音频标准和协议,其目的是简化不同设备之间的音频数据传输,例如,音频播放器与扬声器之间、DVD播放器与AVR之间,而不必将数据转换为模拟信号。

本文将讨论与音频行业相关的各种标准和协议,同时也会探究不同平台的音频系统结构以及各种音频算法和放大器。

标准和协议

S/PDIF标准——该标准定义了一种串行接口,用于在DVD/HD-DVD播放器、AVR和功率放大器等各种音频设备之间传输数字音频数据。当通过模拟链路将音频从DVD播放器传输到音频放大器时,会引入噪声,该噪声很难滤除。不过,如果用数字链路代替模拟链路来传输音频数据,问题就会迎刃而解。数据不必转换为模拟信号就能在不同设备之间传输,这是S/PDIF的最大优势。

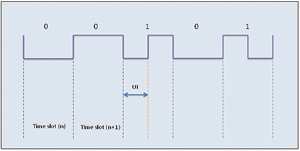

该标准描述了一种串行、单向、自备时钟的接口,可互连那些采用线性PCM编码音频采样的消费和专业应用数字音频设备。它是一种单线、单信号接口,利用双相标记编码进行数据传输,时钟则嵌入数据中,在接收端予以恢复(见图1)。此外,数据与极性无关,因此更易于处理。S/PDIF是从专业音频所用的AES/EBU标准发展而来。二者在协议层上一致,但从XLR到电气RCA插孔或光学TOSLINK的物理连接器发生了改变。本质上,S/PDIF是AES/EBU格式的消费型版本。S/PDIF接口规范主要由硬件和软件组成。软件通常涉及S/PDIF帧格式,硬件则涉及设备间数据传输所使用的物理连接媒介。用于物理媒介的各种接口包括:晶体管与晶体管逻辑、同轴电缆(以RCA插头连接的75Ω电缆)和TOSLINK(一种光纤连接)。

图1 S/PDIF双相标记编码流

S/PDIF协议——如上文所述,它是一种单线串行接口,时钟嵌入数据之中。传输的数据采用双相标记编码。时钟和帧同步信号在接收器端与双相解码数据流一同恢复。数据流中的每个数据位都有一个时隙。时隙以一个跃迁开始,并以一个跃迁结束。如果传输的数据位是“1”,则时隙中间还会增加一个跃迁。数据位“0”则不需要额外跃迁,跃迁之间的最短间隔称为单位间隔(UI)。

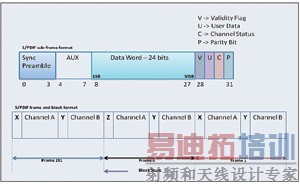

S/PDIF帧格式——首先驱动数据的最低有效位。每个帧有两个子帧,分别是32个时隙,共64个时隙(见图2)。子帧以一个前导码开始,后面跟随24位数据,最后以携带用户数据和通道状态等信息的4位结束。子帧的前4个时隙称为前导码,用于指示子帧和块的开始。前导码有三个,每一前导码均包含一个或两个持续时间为3UI的脉冲,从而打破双相编码规则。这意味着,该模式不可能存在于数据流中的其他地方。每个子帧都以4位前导码开始。块的开始用前导码“Z”和子帧通道的开始“A”表示。前导码“X”表示通道“A”子帧的开始(不同于块的开始),前导码“Y”表示通道“B”子帧的开始。

图2 S/PDIF子帧、帧和块格式

I2S总线——在当今的音频系统中,数字音频数据在系统内部的各种器件之间传输,例如编解码器、DSP、数字IO接口、ADC、DAC和数字滤波器之间。因此,为了增强灵活性,必须有一个标准的协议和通信结构。专为数字音频而开发的I2S总线规范现已被许多IC厂商采用,它是一种简单的三线同步协议,包括如下信号:串行位时钟(SCK)、左右时钟或字选择(WS)以及串行数据。WS线表示正在进行传输的声道。当WS为逻辑高(HI)电平时,右声道进行传输;当WS为逻辑低(LO)电平时,左声道进行传输。发送器以二进制发送数据,首先补足MSB。几乎所有DSP的串行端口都将I2S作为串行端口模式之一。音频编解码器也支持这种模式。

[p]

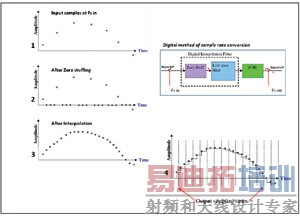

采样速率转换器(SRC)——这是音频系统的一个重要组成部分。采样速率转换既可以通过软件实现,也可以通过一些处理器的片内硬件来支持(见图3)。它主要用于将数据从一个采用特定采样速率的时钟域转换到另一个采用相同或不同采样速率的时钟域。

图3 采样速率转换过程的四个不同阶段

音频可以采用不同采样速率进行编码,其他任务由编解码器完成。某些情况下需要改变编解码器的主时钟,以支持特定采样速率。从采用某一采样速率的音频转换为采用不同采样速率的音频时,即时改变主时钟并不是一件容易的事,有时甚至不可能完成,因为需要更改电路板上的硬件。因此,采样速率转换一般在将数据驱动到编解码器之前执行。这样,编解码器的采样速率不需要改变,可以保持恒定。串行端口以采样频率1发送音频数据到另一端的SRC和编解码器,然后以采样频率2从SRC读取音频数据。

SRC分为两种类型:同步SRC和异步SRC。与同步SRC连接的输出器件为“从机”,与异步SRC连接的器件为“主机”。“主机”是指驱动SCK和帧同步信号的器件。

SRC利用输出采样速率极高的插值滤波器和零阶保持器(ZOH)将离散时间信号转换为连续时间信号。插值值被馈送至ZOH,并以Fs out的输出采样频率进行异步采样。

音频系统

大多数手持式音频设备支持双声道,并能解码MP3、Ogg、WMA媒体格式。这些设备大多依赖电池供电。还有许多手机,其中一些称为“音乐手机”,也属于此类设备。另一方面,家庭影院系统支持多扬声器、多声道音频,例如,Dolby、DTS和各种其他音频后处理算法(THX、ART、Neo6等)。

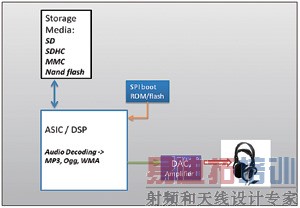

便携式音频系统——有些手持式音频系统采用ASIC,有些则采用DSP。MP3、Ogg和其他媒体文件等音频内容通常存储在高密度存储设备中,如NAND闪存、安全数字(SD)卡、多媒体卡(MMC)和安全数字高容量卡(SDHC)等。

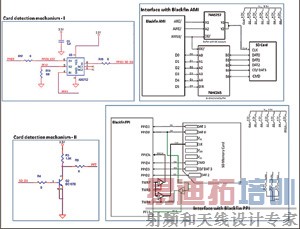

图4显示了与ASIC/DSP的主要系统接口。SD和MMC还支持串行SPI模式,DSP和各种微控制器/微处理器通常提供此种模式。某些处理器片内支持这些标准。利用处理器的其他资源/接口,如并行端口或异步存储器接口等,也可以通过软件实现这些协议。当然,软件实现方法会增加开销。对于运行操作系统(OS)或内核的系统,必须使这些接口和驱动程序与OS兼容,而不应依赖中断服务等。OS环境下可能会引起不可预测的延迟,影响接口时序规格,使得接口不可靠,有时甚至无法工作。为了确保OS兼容,可能需要使用额外的硬件胶合逻辑。

图4 手持式音频系统框图

例如,一个设计示例(见图5)在处理器的外部存储器接口上实现了SD 2.0规范。数据总线不仅用于数据传输,而且用于与SD卡交换命令和响应。在SD卡的4位模式下,数据总线的D0至D3信号连接到SD卡的数据线(DAT0至DAT3)。处理器数据总线的D4用于与SD卡进行命令和响应通信。由于命令字必须通过CMD信号串行发送,因此一系列8位字形成内部存储器中的帧,使得各个字的D4依次具有命令字的一位。这种数据重排是通过函数调用在软件中完成。类似地,软件对接收的状态信息和来往SD卡的实际数据执行数据重排。SD卡时钟信号自ARE/(读取选通)和AWE/(写入选通)信号获得。ARE/和AWE/连接到一个具有开集输出的缓冲器的输入端。AMS3/(异步存储器片选选通)连接到此缓冲器的输出使能引脚。此缓冲器的输出执行“线与”处理,所产生的信号作为时钟提供给SD卡。数据线也通过一个双向缓冲器进行缓冲。

AMS3/驱动缓冲器的输出使能引脚。要求对缓冲器进行隔离,以便其他异步存储设备也能共享数据总线。D5驱动双向缓冲器的DIR(方向控制)引脚。缓冲器两端均需要上拉电阻。BF-54x等其他一些Blackfin产品提供片内SD支持。

图5 Blackfin BF-527处理器异步存储器接口和并行外设接口上的SD设计

文件系统——需要实现FAT16/32来管理存储卡上的音频文件和文件夹。这些代码与音频解码器代码集成。解码后的音频数据接着被送至数模转换器(DAC),经过放大后再被送至音频立体声连接器。与DAC相连的接口通常是串行I2S接口。DAC配置通过串行外设接口(SPI)或I2C兼容外设来完成。运行时,可以通过此控制接口改变各种DAC参数,如采样率、增益/音量控制等。

[p]

处理器或FPGA从SPI引导ROM/闪存器件进行引导加载。应用程序下载至其内部存储器后执行。处理器利用其内部SRAM为IO数据缓冲器存储编码音频帧(从存储介质读取)和解码音频数据(驱动至DAC)。

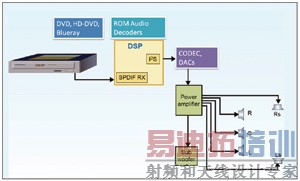

AVR/家庭影院系统——家庭影院音乐系统通常是多声道音频系统(见图6)。Dolby 5.1和DTS 5.1是主流多声道音频系统。DVD播放器通过光纤或同轴电缆S/PDIF接口发送编码音频数据流。系统利用S/PDIF接收器芯片解码双相标记编码数据,并提供与处理器相连的串行帧接口。S/PDIF接收芯片通常向处理器提供I2S格式的数据流。某些处理器片内集成S/PDIF接收器,无须使用外部接收器芯片。处理器运行自动检测算法来确定数据流类型,如Dolby、DTS或非编码PCM音频流等。

图6 多声道音频系统框图

此算法在后台持续运行。自动检测流程基于IEC61937非线性PCM编码比特流国际标准。调用主算法,并将主音频解码器算法所需的各种参数正确传递给函数。解码后的音频数据被复制到已分配的输出缓冲器中。串行端口用于将此解码音频数据以I2S格式驱动至DAC,然后将模拟信号馈送至功率放大器,最后再馈送至扬声器。

音频算法

音频算法可以分为两类:主解码器算法和后处理算法。主解码器算法包括Dolby、DTS 5.1、DTS 6.1、DTS96/24、AAC等。后解码或后处理算法包括Dolby ProLogic、Dolby ProLogic II、DTS Neo6、Surround EX、Dolby耳机、Dolby虚拟扬声器、THX、原始环绕声、Dynamic EQ、Delay等。必须使用高性能信号处理器,而且能执行房间均衡等额外功能。

音频放大器

放大器可以分为如下几类:A类、B类、AB类和C类。放大器的类别基本上由晶体管放大器的工作点或静态点决定。此点位于共发射极配置中晶体管输出特性的直流负载线上。静态点表示相对于特定基极电流“IB”的特定集电极电流“IC”。基极电流“IB”取决于晶体管的偏置,集电极电流“IC”是直流电流增益“hfe”与基极电流“IB”的乘积。A类放大器的静态点几乎位于负载线有效区间的中点,对于任何给定的输入信号变化,晶体管总是在有效区间工作,忠实放大输入信号,而不会引起任何中断或失真。此类放大器用于小信号放大,然后该信号即可驱动功率放大器。由于晶体管始终导通,因此会消耗大量功率,功率效率较低。这使得A类放大器不适合用作功率放大器。为了提高效率,晶体管必须关闭一定的时间,为此需要降低直流负载线上的静态点,使它偏向截止区间。这样就得到其他类型的放大器,如B类、AB类和C类。采用推挽配置的B类放大器是首选功率放大器。它以推挽方式使用两个晶体管,各晶体管导通180°。

但在交越时,存在一个二者均不导通的区间,这会导致交越失真。C类放大器的功率效率可以达到80%,但由于晶体管的导通比例不足输入信号的50%,因此输出失真较高。在有效区间使用晶体管还要求利用散热器来保护晶体管,而这正是D类放大器技术优于其他类型的地方。

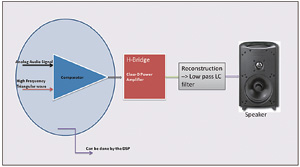

图7为一个D类放大器系统。有时将这种放大器称为数字放大器,但事实并非如此。其工作原理仍然与其他类型放大器相同,但D类放大器的输入信号为PWM(脉冲宽度调制)信号。由于数字输入在逻辑高电平和逻辑低电平之间来回切换,因此晶体管工作在饱和区间或截止区间,但决不会工作在有效区间,因此功耗始终最低。这使得功率效率大幅提高,但同时也会引起较高的总谐波失真(THD)。

图7 模拟域中的D类放大器系统框图

为了解调PWM并重建原始模拟波形,需要使用由LC(电感+电容)构成的高质量低通滤波器。由于大多数音频系统使用DSP,因此D类放大器对音频系统设计很有利。音频信号可以由DSP本身调制为PWM,然后直接馈送至D类放大器的输入端,而无须使用音频DAC或编解码器。因此,除了提高放大器功率效率以外,它还能通过消除编解码器/DAC来降低系统成本。对于D类放大器设计而言,低通重建滤波器是确保良好THD指标的最重要因素。

结语

音频系统设计近年来发展迅猛,特别是在家庭娱乐和汽车音响领域。各种标准、编码技术和强大的处理器已使得多声道高清音频成为现实。音频系统设计人员仍在攻克各种难题,例如,保持高功率效率、实现更低的THD和再现高质量声音等。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...