- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA+ DSP的实时 像处理系统设计与实现

摘 要: 针对图像处理系统计算量大、实时性高和体积小的要求, 研制了一种以DSP为主处理器FPGA 为辅处理器的高性能实时图像处理系统。利用这两种芯片的各自特点, 将算法分成两部分分别交由FPGA 和DSP处理, 大大提高了算法的效率。系统具有结构简单易于实现和运用方便灵活的特点, 加载上相应的程序之后能实现对所获取的图像跟踪、识别和匹配等处理方法。详细说明了系统的设计思路和硬件结构, 并在硬件系统上进行了算法仿真及实验验证。实验结果表明: 该系统实时性高, 适应性好, 能够满足设计要求。

1 引 言

图像处理系统的处理算法复杂, 计算量大, 处理实时性要求高, 同时系统的体积也有严格的限制。

因此在设计系统时必须综合考虑这些特点, 合理选用芯片并保留一定的余度。通常的方法是以FPGA和DSP作为系统的处理器, 即由FPGA 承担图像预处理功能, DSP实现更复杂的图像处理算法。在这样一种结构之上如何扩展系统的应用, 增加其灵活性并减少因前期设计不当造成的风险是设计前需要重点考虑的问题。

2 系统结构设计

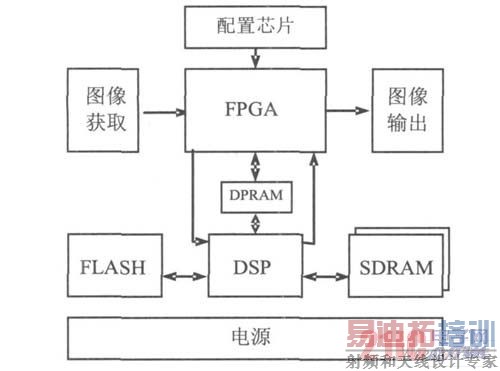

实时图像处理系统除了FPGA和DSP这两个核心部分之外, 还应该有图像获取模块、图像输出模块以及相应的存储部分及通信控制电路等组成。各个主要模块的功能如下:

图像获取模块: 将成像仪输入的图像进行分离、放大, 并在FPGA 的控制下完成A /D 采样, 将模拟信号转换为数字信号, 并将数字信号输入FPGA 模块。

FPGA 模块: 该模块的主要功能是: 1产生系统所需要的逻辑控制信号,2为各芯片提供时钟信号,3对输入图像进行预处理。

DSP模块: 对预处理后的图像进行目标检测、识别与跟踪等复杂的图像处理运算。DSP模块是整个系统的核心模块。

图像输出模块: 对处理后的数字图像进行D /A转换, 并叠加同步信号后形成标准的视频, 实现对处理结果的显示。

实时图像处理系统结构如图1所示。

图1 实时图像处理系统结构框图

3 系统的具体实现方案

明确了系统的基本组成模块之后需要做的工作是: 在满足实时图像处理算法各种要求的条件下如何将这几个部分组合起来, 使得系统易于实现, 并具有较高的可靠性。同时还要对各模块仔细分析加以改进以扩展系统的应用范围。以下是各模块的具体组成。

3. 1 图像获取模块

为扩展系统应用, 该模块有两路视频输入通道,可以根据实际的需要决定是一路还是两路视频输入。当将系统用于双目成像系统时由于双目视觉要求两个成像仪同步, 所以在第一路视频通道中经EL4501分离出的复合同步信号接到第二路成像仪的同步输入口, 以实现两个成像仪的同步。因为成像仪输出为模拟视频信号, 所以分离之后的视频信号须经A /D转换才能进入到FPGA中。A /D采样过程由FPGA 控制, 由第二路视频通道分离出来的场同步、行同步和奇偶帧指示信号直接进入到FPGA,FPGA 将同步信号和奇偶帧指示信号作为中断来控制采样的开始和停止。同时为防止系统其它电路对图像获取模块的干扰, 在信号进入到FPGA 之前应该加上隔离芯片对信号进行隔离。

[p]

3. 2 FPGA 模块

FPGA 是系统中实现图像采集、图像预处理、产生各种控制逻辑和时钟信号的芯片, 系统选用的XC4VSX35芯片是V4 系列中专为数字信号处理进行了优化的一款FPGA。该芯片支持主串、从串、主SelecMt AP、从SelecMt AP和JTAG 边界扫描四种加载模式。本系统选用主串模式和JTAG 边界扫描模式。FPGA使用一块50MHz的晶振作为其全局时钟输入, 依靠V4的片内数字时钟管理器( DCM )可产生24MHz~ 500MH z的时钟频率。

在视频信号输入端, 由于PAL制式视频采用了隔行扫描方式, 每帧图像由奇、偶两帧合成, 所以在FPGA 内部需配置一个双口RAM 以存储奇帧的图像, 等待偶数帧进来之后再将两场合成为一帧完整的图像。双口RAM 的大小及纵深比应根据算法的实际需要来调整。作为系统的协处理器, 图像的预处理也是由FPGA 来完成。FPGA 与DSP 的数据交换有多种方式。对于图像处理系统来说, 其交换的数据量大, 视频的像素速率高。所以使用一块双口RAM作为FPGA 与DSP数据交换的桥梁, 两块芯片各控制一端的读写来完成数据的交换, 这样既满*换数据量大的要求, 又方便实现。双口RAM 选用的是IDT70V631S, 存取周期12ns, 两个端口有各自的地址总线、数据总线和读写控制。DSP和FPGA可以在各自连接的端口对其进行访问和控制。

图像实时处理系统一般是一个控制平台中的一部分, 图像处理系统的最终处理结果通过多通道缓冲串口由FPGA 转接后传至上位机, 而上位机控制命令也由串口传至DSP。串口通信控制可以由FPGA编程实现, 也可以选用专门的芯片来实现, 为节省FPGA 片内资源, 串口通信控制使用串口通信控制芯片TL16CTL16C554实现。

3. 3 DSP模块

DSP由于其计算精度高, 可完成结构复杂的图像处理算法, 所以在系统中是核心处理器。本系统选用的DSP 芯片是TI生产的TMS320C6416 (简称C6416), 其工作频率最高达850MH z, 峰值处理速度达到了6800MSPS, 处理能力强大。DSP核心时钟可通过设置CLKMODE0、1两个引脚( pin)电位的高低来改变, 总共有BYPASS( x1)、x6、x12和x20四种模式。DSP 与FPGA 的数据交换通过双口RAM( DPRAM)。虽然C6416片内集成了高达8M 位的片内高速缓存, 但考虑到图像处理算法必涉及到对前后几帧图像进行处理, 为保证系统运行时存储容量不会成为整个系统的性能瓶颈( choke point), 在DSP模块中额外扩展存储空间。由于EM IFA 口的数据宽度更大, 因此系统在EM IFA 的CE1 空间内扩展了两片总共128M 位的同步存储器。 C6416的引导方式有三种, 分别是: 不加载, CPU 直接开始执行地址0 处的存储器中的指令; ROM 加载, 位于EM IFB CE1空间的ROM 中的程序首选通过EDMA被搬入地址0处, ROM 加载只支持8 位的ROM 加载; 主机加载, 外部主机通过主机接口初始化CPU的存储空间, 包括片内配置寄存器。本系统采用的是ROM 加载方式。C6416 片内有三个多通道缓冲串口, 经DSP处理的最终结果将通过DSP的多通道缓冲串口传送至FPGA。

3. 4 图像输出模块

该模块的功能是将DSP 处理后的图像数据进行数模转换, 并与字符信号合成后形成VGA 格式的视频信号。这里选用的数模转换芯片为ADV7125。

这是AD I公司生产的一款三通道(每通道8 位)视频数模转换器, 其最大数据吞吐率330MSPS, 输出信号兼容RS- 343A /RS - 170。由FPGA 产生的数字视频信号分别进入到ADV7125的三个数据通道, 经数模转换后输出模拟视频信号并与原来的同步信号、消隐信号叠加后便可以在显示器上显示处理的结果了。和图像获取部分一样, 为避免其它电路的干扰, 图像输出部分也需要加上数据隔离芯片。

4 系统仿真验证

图像处理算法可分为预处理算法和后期的复杂算法。预处理算法主要包括图像的校正、增强和简单的分割等, 主要作用就是加强图像的特征, 消除干扰和提取有用信息。这一类算法的特点是算法简单但运算量大, 适合于FPGA 来完成。预处理后的图像一般为二值图像, 这样一来图像的冗余量就大大减少, 这样后期的复杂算法在对图像进行匹配、识别、跟踪等操作时数据量就大大减少, 增加了算法的可行性。为验证本硬件系统的有效性, 进行了大量仿真测试试验, 图2~ 图5为桥梁识别的试验结果。

其中, 图3、图4是FPGA 模块上进行图像增强与分割等预处理的测试结果。图5 是基于DSP 的目标识别结果。

图2 原始图像 图3 FPGA 图像增强结果 图4 FPGA图像分割结果 图5 基于DSP的目标识别结果

5 结 论

实时图像处理系统以DSP和FPGA 为基本结构, 并在此结构的基础上进行了优化, 增加了视频输入通路。同时所有的数据交换都通过了FPGA, 后期的调试过程证明这样做使得调试非常方便, 既可以监视数据的交换又方便修正前期设计的错误。整个系统结构简单, 各个模块功能清晰明了。经后期大量的系统仿真验证: 系统稳定性高, 处理速度快,能满足设计要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:MC68HC908LJ12芯片的导轨式安装三相电能表的工作原理及应用

下一篇:基于DSP的无位置传感器永磁同步电机磁场定向控制系统