- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP 的高速信号采集系统设计

1 引言

数据采集技术是一项基本的实用性技术,已被广泛地应用于测量、检测、控制、诊断等各个领域。随着电子技术, 计算机技术和通信技术的迅猛发展, 国内外用数字信号处理的办法检测, 采集, 分析, 处理各种数据已经成为一种趋势,而运用数字信号处理的方法对现场采集的音频信号进行实时分析,为现场状况的预测提供精确的数据分析依据,现己经在故障检测、灾害预防、军事等方面得到了广泛的应用。在铝电解工业中,确认电解槽的破损形式和部位时可利用其发出的信号进行检测。在铝电解的生产过程中会产生一些特征频率,如熔体循环流动、界面波动、阳极气体排出等等,也可以利用这些信号所传达的信息实时检测进行故障预防。本设计的功能是采集铝电解槽的20kHz 以下频率信号即音频信号缓冲存储并实时上传到PC 机并且接收PC 机传来的指挥信号。

2 系统总体结构设计

单片机工作频率较低, 其信号处理能力远远不及DS P , 但是它拥有丰富的接口, 本设计中用到了较多芯片, 其初始化控制协调运行等需要较多的接口, 所以选择单片机作为主机控制所有芯片。DSP 主频为100MHz肯定达到处理要求,外扩的64k SRAM 为语音滤波等算法提供了空间。在与PC 机的通讯中,DSP 没有内置任何通讯模块, 单片机内置了串口通讯, 但对于高速信号采集和远程采集控制来讲串口显然不符合要求,所以本设计采用了瑞立公司的网络通讯芯片8019 通过网线与PC 机进行通信,它遵守TCP/IP 和UDP 协议,从而使该系统可以通过网络进行远程控制,理论上要求传输速度为96k*32 位*2 加开销大约为8M/s,五类双绞网线带宽为10M,传输距离200 米,可以达到电解槽现场要求。

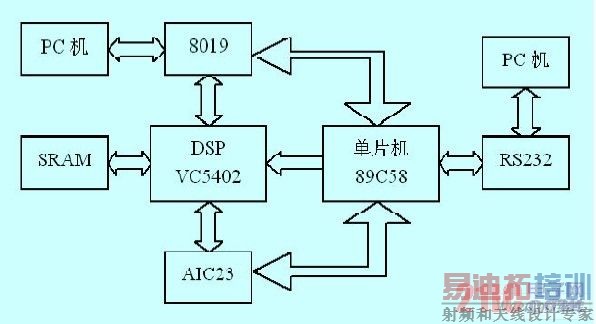

系统总体架构如图1 所示,由单片机通过DSP 的主机接口HPI 控制DSP 的加载启动和复位, 单片机控制AD 模块AIC23 的初始化和复位,同时也控制网络通讯模块8019 的上电复位,通过串口RS232 可以将程序下载到单片机中。DSP 则通过多通道缓冲串口McBSP 与AIC23 进行数据交换,同时通过网络模块8019 与上位机进行数据通信,SRAM 则为DSP 的数据存储和处理提供了更广阔的空间。另外CPLD 模块并未在图中表示出,所有需要逻辑的信号都要通过CPLD 模块进行逻辑,如片选信号, 地址译码信号, 一部分复位信号等等。

系统总体架构图

图1 系统总体架构图

2.1 主从结构设计

系统由单片机和DS P 组成主从结构, 单片机为主机,主要通过DSP 的HPI 外设对DSP 进行控制,该外设包括HD[0-7] 八个数据线和十个控制引脚,用单片机的P0 口连接DSP 的HD 口,P2 口连接需要控制的几个控制引脚,这样通过P0 口和P2 口,单片机就可以通过HPI实现对DSP 的控制,事实上主要是上电复位的bootloader引导过程。单片机对DSP 的启动控制过程是首先上电发复位信号,DSP 上电复位后30 个CPU 周期内会首先检查INT2 中断标志是否有效,将HPI 的HINT 引脚连接到INT2 上,这样DSP 复位后HINT 的低电平使INT2有效,正好选择了HPI 模式,待DSP 完成了对HPI 实现方式的确认后向DSP 装载程序,程序搬移完成后设置程序入口点,这样就实现了DSP 的启动。

2.2 DSP 与AIC23 的通信

DSP 与AIC23 间的通信是通过McBSP[6]口实现的,它是一个多通道多缓冲全双工的串行通信接口,AIC23通过单片机配置可以实现8kHz-96kHz 的采样率[4],根据采样定理采样率需要达到40kHz 以上,将AIC23 配置为96kHz 的采样率。硬件连接方案如下:将DSP 的BDX0(发送串行数据)BDR0(接收串行数据)BFSX0(发送帧同步引脚)BFSR0(接收帧同步引脚)与AIC23 的DIN(接收串行数据)DOUT(发送串行数据)LRCIN(接收帧同步信号)LRCOUT(发送帧同步信号)相连接。因为整个通信过程是由DSP 主导的,所以时钟信号统一用BCLKX0(发送时钟引脚),故而将BCLKX0 BCLKR0(接收时钟引脚)以及AIC23 上的BCLK 相连。

2.3 DSP 与8019 的通信

对于DS P 来讲, 8 0 1 9 好比一个片外存储器, 所以DSP 对8019 的操作与对片外存储器的操作相同,连接方法也与存储器连接方法相同, 这里不再螯述, 事实上,8019 内部存储器分为三部分即控制寄存器和数据发送接收存储器。

[p]

3 系统软件设计

3.1 单片机程序设计

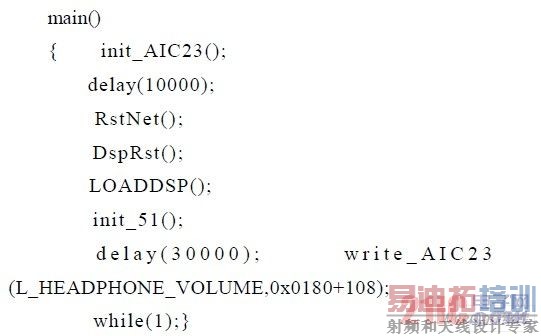

单片机控制着整个系统,主要工作是各个芯片的上电复位初始化, 对于不同的芯片操作方式也不尽相同,程序设计中将每个芯片初始化定义为一个函数,其主函数如下:

对DSP 的初始化过程分为复位和加载程序两步,完成初始化后通过AIC23 放音。

3.2 DSP 程序设计

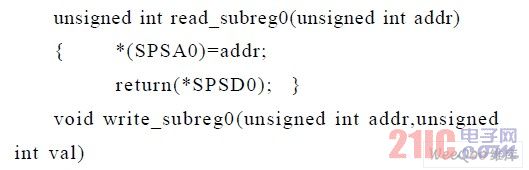

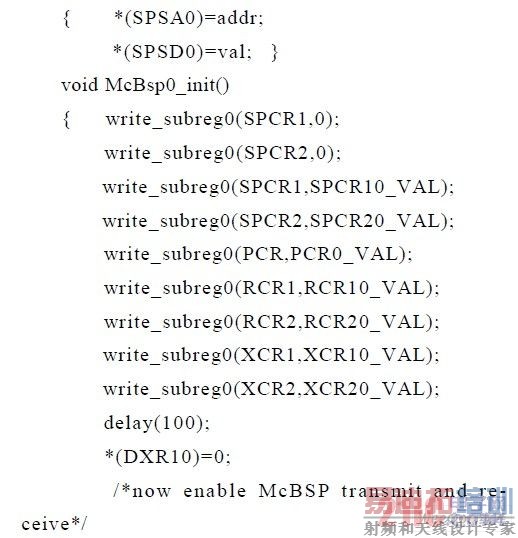

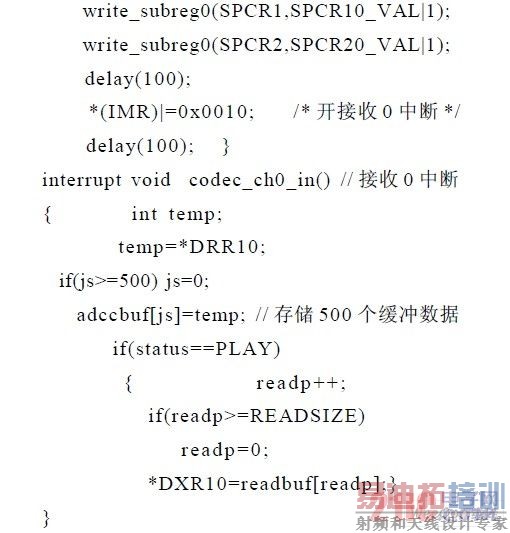

DSP 程序包括主程序,AD 控制程序,8019 控制程序,中断向量表和命令文件。主程序中完成对自身各寄存器的配置和外围芯片的二次初始化以及死循环,需要配置的自身寄存器包括几个基本状态寄存器,定时器有关寄存器和多通道缓冲串口寄存器。AD 控制程序包含于McBSP 接收中断服务程序中,该程序将接收到的信号存储到一个定义好的缓存中,同时将发送缓存中的一个信号送给AD。程序如下:

[p]

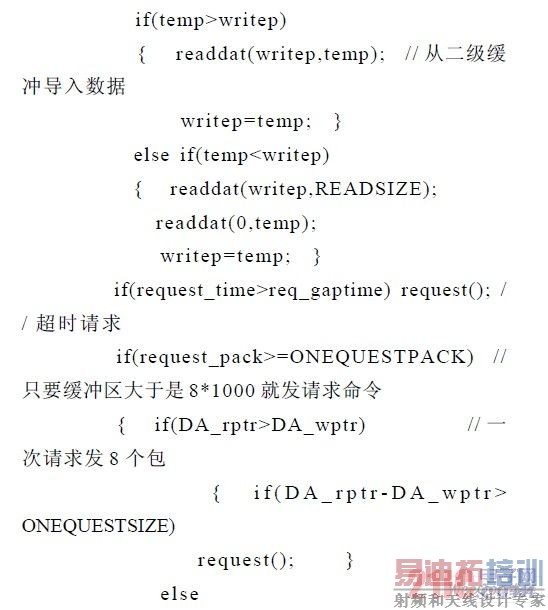

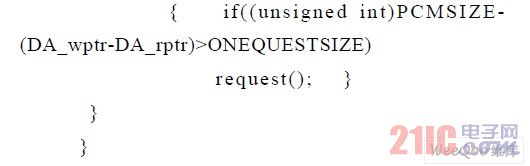

8019 控制程序是最繁琐的一部分,因为编程过程要遵循TCP/IP 和UDP 协议,8019 具有独特的分页控制寄存器的功能。可以将复杂的控制程序分为几个控制函数, 好在制造商已经为用户提供了这几个函数的库文件,用户只需要调用就可以了,以下给出8019 通信程序:

[p]

3.3 CPLD 程序设计

CPLD 程序中要完成的有片选信号(包括一部分地址信号)和中断信号的逻辑处理,选用ALTRA 的EPM7032AE[5]。

DSP 的外部中断INT1 反映的是USB 中断请求,INT1 为低有效而USBINT 为高有效,INT1<=NOT(USBINT);DSP 的RW 信号在读操作时为高电平在写操作时为低电平,MEMSTRB 存储器选通信号为低有效,SRAM 的写信号MEMWR 和读信号MEMRD 均为低有效, 故MEMWR<=RW OR MEMSTRB,MEMRD<=NOT (RW)OR MEMSTRB;DSP 的I/O 选通信号IOSTRB 为低有效, 而对于接受I /O 控制的USB 芯片来讲其读写信号RD 和WR 均为低有效,故IOWR<=RW OR IOSTRB,IORD<=NOT(RW) OR IOSTRB;DSP 的数据选通信号DS 为低有效,存储器选通信号MEMSTRB 也为低有效,而SRAM的片选信号RAMCS 同样为低有效,并且RAMCS在DS 或MEMSTRB 有效时均应被激活,RAMCS<=MEMSTRB OR DS;3.4 上位机程序设计:

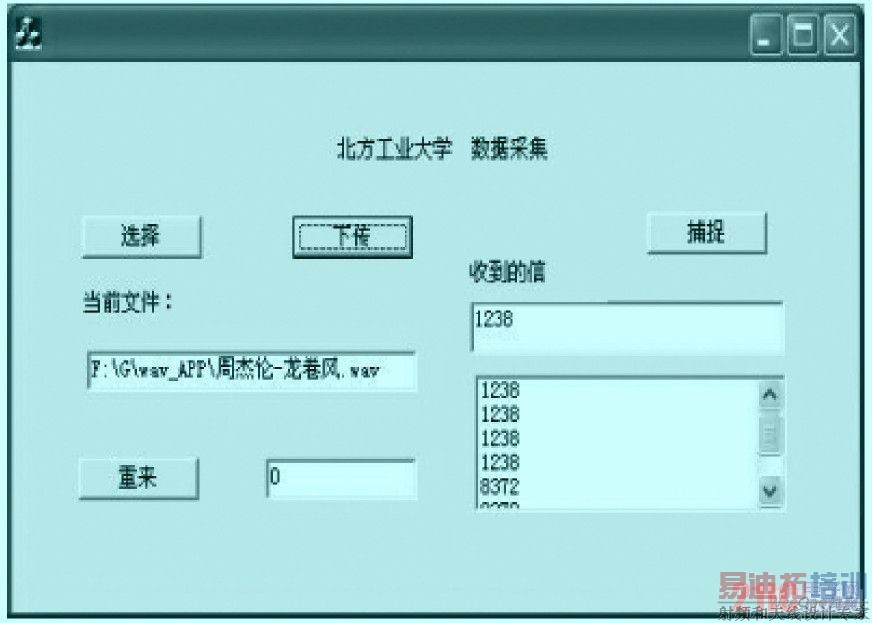

上位机程序的功能是接收来自下位机的传送数据和向下位机发送数据和命令,对于接受到的数据可以利用数据分析系统进行分析得出结果,而对于向下位机发送的数据工业中以控制参数和音频命令居多,故本设计中上位机界面提供了这些内容, 界面如图2 所示。

上位机界面

图2 上位机界面。

3.5 调试

抓包测试图

图3 抓包测试图。

电路板制作完成后, 用联机网线将电路板和PC 机连接,将电路板IP 和PC 机IP 设置在同一组中,从PC 机发送包含0-20kHz 各个频率的音频信号给DSP,DSP 将该音频通过AIC23 后播放,与PC 机同步播放的音频信号相对比检查传输实时性, 对比其各部分频率或对比PC 机内和DSP 内数据数值可知数据传输质量如何。同时DSP 将采集到的信号发送给PC 机,由于数量很大全部显示反应迟缓所以捕捉显示,对比CCS 查看到的DSP内存储数据可知传输是否正确,用网络抓包软件抓包可以清楚的看到通信的内容, 如图3 所示。

4 结束语

系统设计完成后通过测试能够完成高速信号的采集和传输, 数据传输正确, 质量良好。数据传输的实时性和可靠性达到用户的设计要求。在该系统的设计中,DSP 的强大运算能力和扩展的数据存储空间为复杂算法的实现提供了条件。在铝电解工业应用中,后续课题中将把电解铝控制的复杂神经网络算法写入到本设计的DSP 中,届时该设计的功能可将现场信号采集实时运算及控制以及上传下载高速信号集于一身。此外,在其它工控场合本设计也可扮演重要角色。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...