- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

各位CLASS设置间距问题

录入:edatop.com 点击:

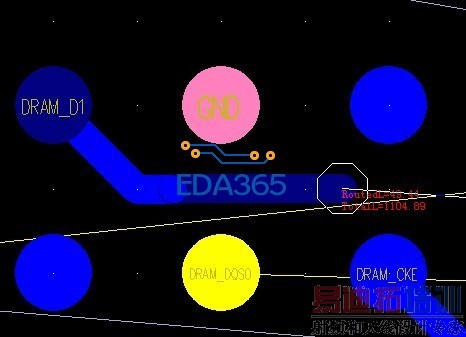

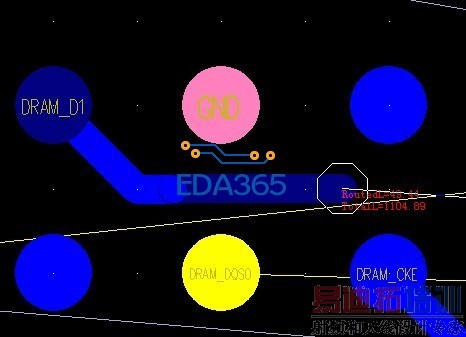

请教各位老师,比如在走DDR中设置ADD 和DAT两个CLASS的走线间距为5,原本意思是在DDR外走线的两个CLASS间距为0.5,但在BGA元件中,会有不同CLASS两个悍盘挨着的情况,如图

线与BGA悍盘间距没这么大,所以就走不出来线,这种情况该怎样处理呀? 谢谢呀

线与BGA悍盘间距没这么大,所以就走不出来线,这种情况该怎样处理呀? 谢谢呀

要么改BGA 的焊盘 要么改线宽4.5MIL

谢谢呀,这个方法不是理想的 ,有没有其它方法呀,比如说BGA里设置个区域,在这个区域不做CLASS与CALSS之间的间距DRC,BGA出线之后才做DRC

可以,设置你这个BGA器件的间距规则就行了。

原来你是想问区域能不能设计规则啊,我以为你5MIL 走不出来。

嘿嘿,那有没有设置方法呀,教下我们,谢谢

已经说了啊,区域设计规则,你设置BGA的规则,BGA区域都是。

pads 不支持区域规则。用4楼方法,设置器件规则。这样,从BGA 拉线就适用器件规则,从CPU 往BGA 拉线就适用class to class 规则。

没用呀,从BGA脚出来走线就已经检测出CLASS间距了,两个CLASS在BGA里面相邻处已经是CLASS间距规则,根本拉不出来线

你有设置器件规则吗? 器件规则优先级最高。你有设置的话肯定拉的出来。要么把你的设置图贴出来。

wpc4208211 发表于 2013-3-18 17:25 你没设置元件的间距 注意和默认的一样的话等于没设置 操作如下 谢谢,我的意思是间距一样是4.5,因为间距4.5在没设CLASS间距时是可以出线的,现在我们要的是在BGA内出线不考虑CLASS间距,在BGA出线后再用上CLASS间距,按你说的修改过,还是达不到所要的,可能PADS跟本就实现不了此功能吧,不知高手有没试过 你在死钻牛角尖啊。非要走4.5过4.5。难道走5过4不行吗?外部走5过5.

操作文件

20120320.rar

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>