- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种基于FPGA的正弦波信号发生器的设计

摘要:现代测试领城中,经常需要信号发生器提供多种多样的的测试信号去检验实际电路中存在的设计问题。传统的信号发生器多采用模拟电路搭建。以正弦波信号发生器为例,结合DDS直接数字合成技术,基于FPGA设计其他外围电路构成正弦波信号发生器。相比传统的模拟信号发生器,该电路具有设计简单,升级容易,波形稳定等特点。

关键词:FPGA;DDS;正弦波信号发生器

O 引言

信号发生器是用来为各种电路提供测试信号的仪器,在工程应用和测试领域有着非常广泛的应用。目前传统的信号发生器是使用模拟电路或者专用芯片搭建而成,但是存在频率不商,稳定性较差,且不易扩展和调试的缺陷;而采用DDS直接数字频率合成技术设计的信号发生器,改变了以往的设计思路,在精度、灵活性上大大超越了模拟信号发生器。随着可编程逻辑器件FPGA的迅速发展,基于FPGA控制的DDS信号发生器使得电路设计更加简单,而且通过预留的端口可轻松进行二次开发。本文通过Altera公司的EPFl0K10LC84-4芯片,成功实现了正弦波信号发生器。

1 系统硬件结构

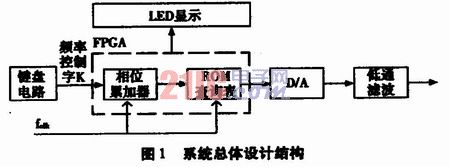

本系统由健盘电路、LED显示、FPGA单元、D/A转化和低通滤波器构成。以FPGA为主控制芯片,结合DDS直接数字频率合成技术产生正弦波信号。系统总体设计结构见图1。

1.1 键盘电路

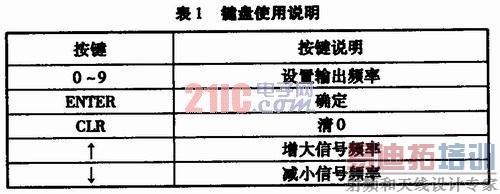

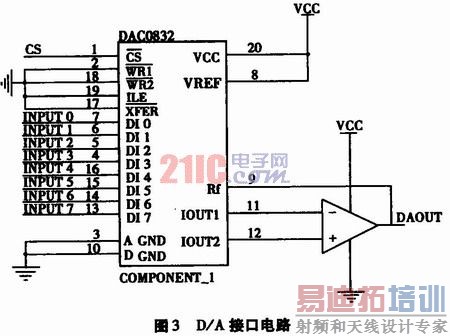

在本系统中,通过键盘电路改变频率控制字K,从而实现对正弦信号的频率、相位的初始化设置。为了节省FPGA的I/O端口,简化硬件线路,键盘电路采用4×4矩阵式健盘。键盘共设有14个键,其中包括4个功能健。具体键盘按键设置如表1。

使用时先通过“0~9”、“↑”、“↑”12个设置按键输入所需信号频率,再按下ENTER执行健,频率控制字K将刷新,使得输出信号频率发生变化。CLR键用于将原有的设定值清零。 [p]

1.2 LED显示

在本系统中,通过4个LED数码管进行动态显示。电路设计如图2所示。LED数码管动态显示的实现方法为依次点亮各个数码管,循环进行显示,利用人眼的视觉暂留特性,数码管每秒导通16次以上,可以达到4个数码管同时显示的效果。但是,延时也不是越小越好,因为数码管达到一定亮度需要一定时间。如果延时控制不好则会出现闪动,或者亮度不够。根据经验,延时0.005秒可以达到满意效果。

1.3 FPGA单元

FPGA单元包括键盘转换频率控制字、LED显示控制、相位累加器、ROM查询表的实现。键盘电路是一组按键开关的集合,FPGA扫描键盘电路的电平信号,通过FPGA中指定程序转化为频率控制字K输入到相位累加器,同时,将设置输出的频率通过4个LED数码管实时显示。

相位累加器是DDS技术的核心,它类似一个计数器,由时钟信号fclk上升沿触发。频率控制字K控制相位累加器的步长,每来一个上升沿,相位累加器上次的基数与频率控制字K相加,得到新相位。新相位作为ROM查询表的地址,相应的波形数据被读取,经过D/A转换输出阶梯波形。本文只将相位累加和ROM查询表作为主要内容在软件设计部分说明,具体内容见第3部分软件设计。

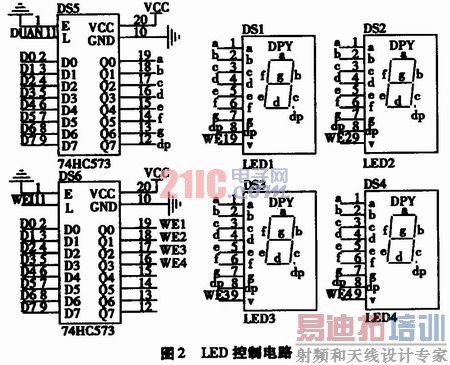

1.4 D/A转化

从FPGA输出的正弦波信号还只是阶梯信号,需要经过D/A转化器进行数字/模拟信号的转化。本设计使用的是8位D/A转化芯片DAC083 2,该芯片采用CMOS/Si-Cr工艺实现。用倒T形电阻网络转换,为电流输出型。DAC0832中有两级锁存器,第一级即输入寄存器,第二级即DAC寄存器,数据输入有直通数字输入、双缓冲输入或单缓冲输入三种工作方式。

D/A接口电路如图3所示。

[p]

1.5 低通滤波电路

低通滤波器用于滤除阶梯信号中的谐波分量。本文采用2阶低通滤波电路,阶梯信号通过低通滤波,使得输出信号频谱纯度较好,失真较小。

2 系统关键技术

DDS(Direct Digital Synthesis)是一种应用直接数字合成技术来产生信号波形的方法。DDS技术建立在采样定理的基础上,它首先对需要的信号波形进行采样、量化,然后存入存储器作为待产生信号的数据查询表。在输出信号波形时,从数据表依次读出数据,产生数字信号。

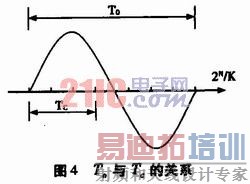

输入时钟频率和输出波形信号的频率关系如图4所示。在图4中To表示输出波形的周期,Tc为采样周期,2N为ROM查询表寻址范围,K为频率控制字。由图可知To=Tc*2N/K,转换为频率可表示为fo=fc*K/2N,fc为时钟信号clk的频率。

在本设计中N=8,因此信号的输出频率fo=fc*K/256。

3 软件设计

软件设计主要是在FPGA中通过Verilog硬件语言进行相位累加器和ROM查询表的编程实现,这两部分采用Quartus软件和Matlab软件并行开发。

3.1 相位累加器的实现

相位累加器主要用于产生ROM查询表所需的地址信息。图5为在Quartus软件中编程生成的相位累加器符号,相位累加器的输入信号包括时钟信号clk、复位信号clr和频率控制字K。输出信号addr[7…0]为ROM查询表的输入地址信号。

相位累加器类似一个计数器。首先,软件设置相位累加器的基数为0,并通过时钟信号clk上升沿触发,基数与频率控制字K相加,相加后的值反馈到相位累加器的输入端作为下一次的基数。当相位累加器的溢出时,—个完整的阶梯正弦信号就从ROM查询表的输出端输出。因此,相位累加器的溢出率就是正弦波信号的输出频率。相位累加器的仿真波形如图6所示。

[p]

3.2 ROM查询表的实现

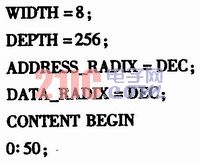

本文设计的ROM查询表寻址范围为256,数据为8bit。ROM查询表如图7所示,输出q[7…O]需与D/A转换器的输入相连。ROM查询表的输出为8位,因此与D/A转换芯片的分辨率相匹配。

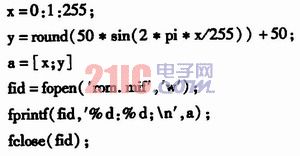

ROM查询表的设计有很多种方法。定制ROM查询表需要在软件Quartus中载入.mif或.hex文件,这两种文件可由多种工具获得,如Quart-us的Text File编辑器、Matlab、DSP Builder、vc++编译器、Keil编译器等工具。本文选用Matab得到正弦波数字幅度值的.mif文件。Matl-ab程序如下:

由于此时生成的.mif文件不符合Quartus中所需载入的.mif格式,还需要对其进行修改。修改格式如下:

最后通过载入此.mif文件,就可获得如图7所示的ROM查询表。

4 系统测试

硬件调试完成后,我们对系统的整体功能进行了测试,并且与Matlab的仿真结果进行了比较。用示波器观测试验波形如图8所示。系统的测试结果表明,输出波形状态良好,未出现明显失真。

5 结束语

本文介绍的这种基于FPGA的DDS正弦波信号发生器,具有电路结构简单、工作频率稳定度高、频率调整精度高等特点。并且,此方法同样适用于三角波、方波等其他任意波形的实现。若要产生某特定波形,只需先用地Matlab对波形曲线采样生成相应的.mif文件,然后载入ROM查询表中,其他硬件不变即可产生所需信号。因此,该设计也可以直接拓展到其他测试领域的电路中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LED光源工作原理及亮度稳定性

下一篇:DSP+FPGA实时信号处理系统