- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA架构的功耗及影响功耗的用户选择方案

本文将介绍FPGA的功耗、流行的低功耗功能件以及影响功耗的用户选择方案,并探讨近期的低功耗研究,以洞察高功率效率FPGA的未来趋势。

功耗的组成部分

FPGA的功耗由两部分组成:动态功耗和静态功耗。信号给电容性节点充电时产生动态功耗。这些电容性节点可以是内部逻辑块、互连架构中的布线导线、外部封装引脚或由芯片输出端驱动的板级迹线。FPGA的总动态功耗是所有电容性节点充电产生的组合功耗。

静态功耗与电路活动无关,可以产生于晶体管漏电流,也可以产生于偏置电流。总静态功耗是各晶体管漏电功耗及FPGA中所有偏置电流之和。动态功耗取决于有源电容一侧,因而可随着晶体管尺寸的缩小而改善。然而,这却使静态功耗增加,因为较小的晶体管漏电流反而较大。因此静态功耗占集成电路总功耗的比例日益增大。

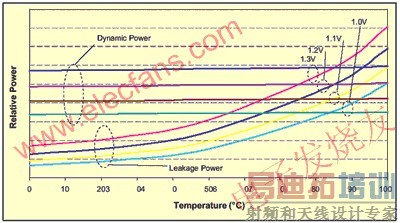

如图1所示,功耗很大程度上取决于电源电压和温度。降低FPGA电源电压可使动态功耗呈二次函数下降,漏电功耗呈指数下降。升高温度可导致漏电功耗呈指数上升。例如,把温度从85℃升高至100℃可使漏电功耗增加25%。

图1 电压和温度对功耗的影响

功耗分解

下面分析一下FPGA总功耗的分解情况,以便了解功耗的主要所在。FPGA功耗与设计有关,也就是说取决于器件系列、时钟频率、翻转率和资源利用率。

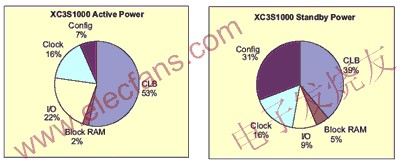

以Xilinx Spartan-3 XC3S1000 FPGA为例,假定时钟频率为100MHz,翻转率为12.5%,而资源利用率则取多种实际设计基准测试的典型值。

图2所示为XC3S1000的活动功耗和待机功耗分解图。据报告显示,活动功耗是设计在高温下活动时的功耗,包括动态和静态功耗两部分。待机功耗是设计空闲时的功耗,由额定温度下的静态功耗组成。CLB在活动功耗和待机功耗中占最主要部分,这不足为奇,但其他模块也产生可观的功耗。I/O和时钟电路占全部活动功耗的1/3,如果使用高功耗的I/O标准,其功耗还会更高。

图2 Spartan-3 XC3S1000 FPGA典型功耗分解图

配置电路和时钟电路占待机功耗近1/2,这在很大程度上是偏置电流所致。因此,要降低芯片的总功耗,就必须采取针对所有主要功耗器件的多种解决方案。 [p]

低功耗设计

FPGA的设计中使用了多种功耗驱动的设计技术。以Xilinx Virtex系列为例,因为配置存储单元可占到FPGA中晶体管数的1/3,所以在该系列中使用了一种低漏电流的“midox”晶体管来减少存储单元的漏电流。为了减少静态功耗,还全面采用了较长沟道和较高阈值的晶体管。动态功耗问题则用低电容电路和定制模块来解决。DSP模块中乘法器的功耗不到FPGA架构所构建乘法器的20%。鉴于制造偏差可导致漏电流分布范围很大,可筛选出低漏电流器件,以有效提供核心漏电功耗低于60%的器件。

除了融入FPGA设计之外,还有许多设计选择方案影响到FPGA的功耗。下面分析部分这类选择方案。

1 功耗估计

功耗估计是低功耗设计中的一个关键步骤。虽然确定FPGA功耗的最准确方法是硬件测量,但功耗估计有助于确认高功耗模块,可用于在设计阶段早期制定功耗预算。

如图1所示,某些外部因素对功耗具有呈指数的影响;环境的微小变化即可造成预估功耗的重大变化。使用功耗估计工具虽难以达到精准,但仍然可以通过确认高功耗模块来为功耗优化提供极好的指导。

2 电压和温度控制

如图1所示,降低电压和温度均可显着减少漏电流。电源电压降低5% 就可降低功耗10%。通过改变电源配置,很容易调整电源电压。目前的FPGA不支持大范围电压调整,推荐的电压范围通常是±5%。结温可以用散热器和气流等冷却方案来降低。温度降低20℃可减少漏电功耗25%以上。降低温度还可呈指数提高芯片的可靠性。研究表明,温度降低20℃可使芯片总体寿命延长10倍。

3 悬挂和休眠模式

悬挂和休眠等模式可有效降低功耗。以Xilinx Spartan-3A FPGA为例,该器件提供两种低功耗空闲状态。在悬挂模式下,VCCAUX电源上的电路被禁用,以减少漏电功耗和消除偏置电流,这样可降低静态功耗40%以上。悬挂时仍保持芯片配置和电路状态。将唤醒引脚置位即可退出悬挂模式。此过程用时不到1ms。

休眠模式允许关闭所有功率调节器,从而实现零功耗。若要重启,必须重开电源并配置器件,此过程需要数十毫秒。切断电源后,所有I/O均处于高阻抗状态。如有I/O需要在休眠模式下主动激活,则必须保持对相应I/O组供电,这会消耗少量待机功率。

4 I/O标准方案

不同I/O标准的功耗水平相差悬殊。在牺牲速度或逻辑利用率的情况下,选择低功耗I/O标准可显著降低功耗。例如,LVDS是功耗大户,其每对输入的电流为3mA,每对输出的电流为9mA。因此,从功耗角度来看,应该仅在系统技术规范要求或需要最高性能时才使用LVDS。

替代LVDS的一种功耗较低而性能较高的方案是HSTL或SSTL,但这二者仍要每输入消耗3mA。如果可能,推荐换用LVCMOS输入。此外,DCI标准是功耗大户。当连接到RLDRAM等存储器件时,请考虑在存储器上使用ODT,而在FPGA上使用LVDCI,以减少功耗。

5 嵌入式模块

用嵌入式模块替代可编程架构可显著降低功耗。嵌入式模块是定制设计的,因此其体积和开关电容都比可编程逻辑的小。这些模块的功耗是等效可编程逻辑的1/5~1/12。如果设计缩小并可装入较小的器件,则使用嵌入式模块可以降低静态功耗。一个潜在的缺点是,使用大型嵌入式模块可能无法更有效地实现非常简单的功能。

6 时钟生成器

在时钟生成中考虑功耗因素可以减少功耗。数字时钟管理器广泛用于生成不同频率或相位的时钟。然而,DCM消耗的功率占VCCAUX不可小觑的一部分;因此,应尽可能限制使用DCM。通过使用多种输出(如CLK2X、CLKDV 和CLKFX),一个DCM常常可生成多种时钟。与为同一功能使用多个DCM相比,这是一种功耗较低的解决方案。 [p]

7 Block RAM的构建

多个Block RAM常常可以组合起来构成一个大型RAM。组合的方式可以对功耗意义重大。时序驱动的方法是并行访问所有RAM。例如,可以用4个2k×9 RAM构成一个2k×36 RAM。这个较大RAM的访问时间与单个Block RAM相同;然而,其每次访问的功耗却相当于4个Block RAM的功耗之和。

一种低功耗的解决方案是用4个512×36b RAM 构成同样的2k×36b RAM。每次访问都会预先解码,以选择访问4个Block RAM之一。尽管预解码延长了访问时间,但较大RAM每次访问的功耗却与单个Block RAM大致相同。

低功耗研究

1 降低电压

降低电压是减少功耗的最有效方式之一,而且随之而来的性能下降对许多并不要求最高性能的设计来说是可以接受的。不过,目前FPGA的工作电压范围很小,在某些电压敏感型电路上还不能使用。

在Xilinx研究实验室,CLB电路被重新设计成能在降低许多的电压下工作,以便在较低功耗情况下提供宽裕的性能权衡余地。例如,对于90nm工艺,电压下降200mV可降低功耗40%,最高性能损失25%;电压下降400mV可降低功耗70%,最高性能损失55%。

2 细粒度电源开关

可编程逻辑设计特有的开销之一是并非所有片上资源都用于给定的设计。可是,未使用的资源保持供电状态,并以漏电功耗的形式增加了总功耗。模块级电源开关可分别关掉未使用模块的供电。每个模块通过一个电源开关耦接到电源。开关闭合时,该模块工作。开关断开时,该模块从电源有效断开,从而使漏电功耗降到1/50~1/100。电源开关的粒度可以小到单个CLB和Block RAM。在设计中,这些电源开关可以通过配置比特流进行编程,也可由用户直接控制或通过访问端口控制。实际设计的基准测试结果表明,细粒度电源开关可减少漏电功耗30%。

3 深睡眠模式

便携电子产品的主要要求之一是器件空闲时功耗极低或无功耗。以Xilinx Spartan-3A FPGA为例,该芯片可通过进入休眠模式来达到此目的,这需要外部控制,苏醒缓慢,且不能恢复FPGA状态。设计动态控制上述细粒度电源开关,令其关闭所有内部模块供电,仅保留配置和电路状态存储组件为供电状态。这样形成的状态是一种深睡眠模式,其漏电功耗为额定功耗的1%~2%,保存FPGA状态,退出此模式仅需数微秒。

4 异构架构

电路的最高时钟频率取决于其时序关键型路径的延迟。非关键型路径的速度可以较慢而不影响整体芯片性能。在大型系统中,可以有几个速度关键型模块(如处理器中的数据通路),其他模块可以是非关键型(如缓存)。

当今的FPGA就功耗和速度而言是相同的;每个CLB 均有同样的功耗和速度特性。异构架构可降低功耗,这种架构包含一些低功耗(同时也较慢)的模块,方法是在低功耗模块中实现非关键型模块。这样做不影响整体芯片性能,因为时序关键型模块并未损失性能。

创建异构架构的一种方法是,分配两条核心供电轨,即一条高电压轨(VDDH)和一条低电压轨(VDDL)。FPGA的每个器件用嵌入式电源开关选择这二者之一,并相应采用高速度或低功耗特性。设计的详细时序确定之后,电压选择便告完成,所以只有非关键型模块才应以VDDL供电。

创建异构架构的另一种方法是,将FPGA分成不同的区,并将这些区分别预制为具有高速度和低功耗特性。可以用不同电源电压、不同阈值或通过若干其他设计权衡条件来实现这些区。要避免性能下降,设计工具必须将设计的时序关键型器件映像成高速度区,而将非关键型器件映射成低功耗区。

5 低摆幅信令

随着FPGA容量增加,片上可编程互连的功耗越来越大。减少这种通信功耗的一种有效方法是使用低摆幅信令,其中导线上的电压摆幅比电源电压摆幅低得多。现今,低摆幅信令常见于在高电容性导线(如总线或片外链接)上进行通信的情况。低摆幅驱动器和接收器比CMOS 缓冲器更复杂,所以占用更多芯片面积。但是,随着片上互连逐渐成为总体功耗的较大组成部分,低摆幅信令的功耗优势将证明增加设计复杂性是值得的。当然,FPGA用户不会看到内部信号电压的差异。

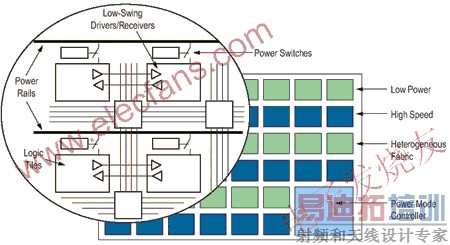

图3所示为具有上述某些概念的FPGA架构,其可编程异构架构由高速度和低功耗两个区组成。一个片上功耗模式控制器可管理各种降功耗模式,即深睡眠模式、悬挂模式和休眠模式。在架构内部,可以用专用的供电开关关掉每个逻辑块的电源。通过布线架构的通信信号流经低摆幅驱动器和接收器,以降低互连功耗。

图3 具有多种降低功耗解决方案的概念架构

结论

除了目前用于现代FPGA设计的能源优化方案,一些用户设计决策也可以产生显著的功耗效益。可以预见,未来的新技术中会有更大胆地遏制功耗的架构解决方案,从而使新的FPGA应用成为可能。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...