- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP Builder的回波抵消器设计与实现

摘要:针对通信中的回波问题,基于自适应滤波的LMS算法,设计了自适应回波抵消器。并基于利用FPGA芯片,在DSP Builder平台上,有效结合MatLab/Simulink和Quanus II设计工具,根据模块化设计思想实现了LMS算法自适应回波抵消器硬件电路设计。软件仿真和系统FPGA硬件实测结果表明,该设计方法使回波抵消器的FPGA硬件实现更加简便快捷。

关键词:DSP Builder;回波抵消器;FPGA

在数字通信、卫星通信等系统中,不同程度的存在回波现象,影响了通信质量。为了消除回波可以采用回波抵消器,它能估计回波路径的特征参数,以产生一个估计的回波信号,然后从接收信号中减去该信号,以实现回波抵消。而一般采用自适应滤波器模拟回波路径,可以跟踪回波路径的变化。

DSP Builder是Ahera公司推出的面向DSP开发的系统级工具,它作为Matlab的一个Simulink工具箱出现,使得用FPGA设计的DSP系统完全可以通过图形化界面进行设计和仿真。

文中介绍以DSP Builder为平台完成自适应回波抵消器的FPGA电路设计,用FPGA验证设计电路的正确性和可靠性。

1 自适应回波抵消器原理

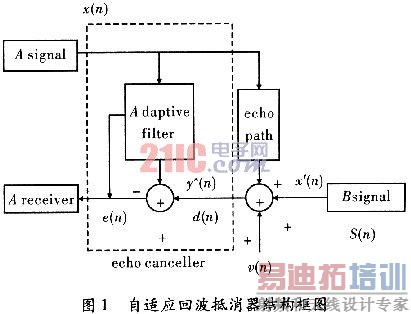

自适应回波抵消结构框图,如图1所示。

图1中s(n)表示B信号;x’(n)表示A信号产生的回波;v(n)为近端环境噪声;y’(n)是滤波器模拟的回波信号;e(n)是残留回波信号或误差信号。信号d(n)由B信号s(n)和回波x’(n)及噪声组成,即d(n)=x’(n)+s(n)+v(n)。假定模拟回波信号估计为

![]()

式中,ωk(n)为自适应滤波器的时变系数,从信号d(n)中减去模拟回波y’(n)信号后的残留回波信号或误差信号为

![]()

当自适应滤波器的单位脉冲响应能很好地模拟回波通道的传递函数时,可以认为时,从而有e(n)=s(n)+v(n),这样传向远端的信号中不包括回波信号x’(n),即回波被抵消。

其中,回波抵消器的主要部分自适应滤波器所用算法选择LMS算法,其迭代公式为

![]()

式中,X(n) =[X(n),X(n-1),X(n-2),…,X(n-M+1)]T表示时刻n时的输入信号矢量,由最近M个信号采样值构成,W(n)=[W0(n),Wl(n),…,WM-1(n)]T表示n时刻自适应滤波器的系数矢量估值,μ是控制稳定性和收敛速度的步长参量。 [p]

2 FPGA硬件设计

设计选用FPGA是Altera公司Cyclone系列的EPlCl2Q240C8。FPGA中I/O端口可自由定义,电路设计方便、编程灵活、不易受外部干扰。系统编译环境采用QuartusⅡ,顶层设计为图形化方式。芯片模块划分为分频模块、D/A转换模块和回波抵消器模块。分频模块采用VHDL语言编程实现,D/A转换模块采用硬件电路实现,同波抵消器模块用DSPBuilder软件进行设计。

2.1 分频模块设计

分频模块是将外部时钟进行分频设定,得到系统内部DA模块和回波抵消器模块所需要的时钟。分频模块的外部时钟输入频率为50 MHz,8分频后产生的时钟频率约为6 MHz。

2.2 回波抵消器模块设计

该部分采用层次化的设计方法。利用DSP Builder模块构建自适应算法部分,根据LMS算法迭代公式(4)和滤波器的估计输出式(2),建立加权分量模型。如图2(a)所示。

在图2(a)中,第i个延时单元的输入信号为x(n),延时后的输出信号为x(n-1),同时输入信号x(n)产生一个乘积y’(n)=ω(n)x(n),由于是滤波器的估计输出是一系列权值分量与输入矢量的各分量乘积之和。因此,除第一级外,后续单元必须加上前一级的加权单元的输出。封装后,则可以根据滤波器阶数的不同而相应调整,以实现多级级联。尤其是在构造阶数可变和阶数较大的滤波器时更能显出其灵活性。然后将封装后的加权分量单元依照阶数级联,并再次封装即构成抵消器模块。可运用于顶层模型中。

在顶层系统模型中连接各子模块,如图2(b)所示,图中两个信号源sin2,sin1采用正弦信号发生器实现,利用正弦查找表产生正弦波数据,函数调用格式为lOsin([0:2π/2∧4:2π])和5sin[0:2π/2∧6:2π],其输入地址分别为4位和6位,输出为16位。Dixiaoqi模块由图2(a)级联封装得到,模块Parallel to serial为并行/串行转换器。

设计中,因语音信号频率可以看作约为3.4 kHz,所以信号采样频率设为8 kHz,假设回波延迟2.5 ms(小于回波对听觉产生干扰的范围20 ms),考虑收敛速度和实现情况,步长采用0.1,计算得出滤波器阶数20。

2.3 D/A转换模块设计

利用Texas Instruments公司的D/A芯片TLC5620,并辅助使用4输入与门SN74HC08M和运算放大器LM358AM,构建数模转换器。TLC5620是8位电压输出的数模转换器,需5V外接电压,有4个输出端口可以选择。利用扩展插槽与FPGA连接,信号接119脚,时钟由所编程序在FPGA内实现,通过73脚与TLC5620连接,控制信号通过63脚连接TLC5620。

3 DSP Builder仿真和FPGA验证

通过Simulink仿真得到波形,如图3(a)所示,图中第一行为返回A听筒的误差e信号波形,第二行为输入话筒的所有信号,即B信号与回波信号之和。由变化的波形可以看出,随着自适应滤波器的“学习”过程,回波逐渐被抵消。

利用ModelSim针对生成的RTL级VHDL代码进行功能仿真,设置信号为模拟形式,如图3(b)所示,图中为减去回波后的误差信号,与Simu-link仿真结果一致。

使用ModelSim完成RTL级功能仿真,其仿真结果并不能精确反映电路的全部硬件特性,进行门级的时序仿真仍然十分重要。在Quartus Ⅱ下编译后进行时序仿真,其仿真波形,如图3(c)所示。 [p]

把回波抵消器模型转化生成图元文件,作为一个子模块在顶层系统中调用。在QuartusⅡ环境下,调用各个子模块,构成完整的系统原理图设计,然后进行编译、仿真和引脚分配等工作。最后下载到FPGA芯片中,对硬件进行测试,采用SignalTapⅡ实际测得的值如图4所示,验证本设计的正确性。

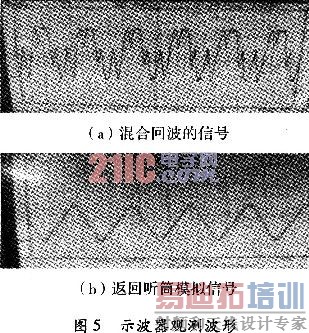

最后通过D/A转换电路接入示波器。观测结果,如图5(a),图5(b)所示,通过比较混合回波的信号和经过抵消后得到的返回听筒的消除回波以后的信号,可以看出回波已基本消除,设计达到目的。通过测试,回波衰减率约为25 dB,基本达到ITUTG.167标准中回波衰减率至少20 dB的要求。

4 结束语

采用DSP Builder进行设计,使用图形界面,用模块化设计代替以往的VHDL语言编程,并综合多种设计工具,便于研究者迅速地将算法级的构思应用于系统设计中,从而可以专注于系统算法的设计,避免了繁琐的语言编程和电路设计,提高了设计速度,缩短设计周期,为产品开发节约了研发时间。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LED点阵显示器原理及程序

下一篇:LED封装的取光效率