- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

在全集成设计环境中开发视频IP

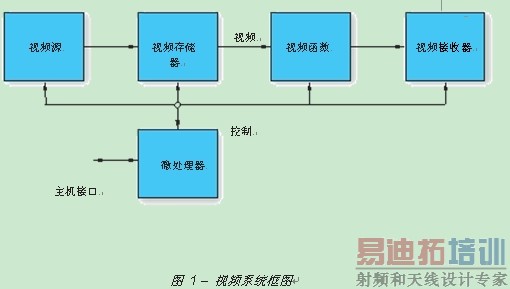

典型的视频处理系统使用一个微处理器来控制一个视频流水线,该视频流水线包括一个视频源和宿,一个用于存储视频数据的大型存储器,和一个视频处理系统(图 1)。

在实现和调试各种视频算法时,您需要通过软件和硬件仿真来验证其功能性。视频流的实时特性和每帧所需的大量视频数据,令视频处理应用的仿真产生了特别的挑战。

设计环境

视频基本套件(VSK) 支持广泛视频应用领域的高性能视频处理系统的快速开发与调试。VSK 采用赛灵思 Virtex-4 XC4VSX35 器件,该器件通过结构中高比例的乘法累加块(也称为 DSP48)而针对 DSP 处理进行了优化,并具有丰富的视频接口特性集支持,如 DVI、VGA、分量(HD)、复合、S视频和 SDI等。

通常,开发视频算法需要使用硬件对实时数据流进行视频操作验证,需要仿真环境来开发和测试视频处理组件。VSK 为视频系统的每个组件同时提供了软件仿真和实时操作,可让您开发视频 IP(包括滤波器、视频块集、加速器和视频接口转换)或最终应用程序,如编解码器、图像增强、动态伽马校正和运动估计等。与工具套件的集成和 I/O 多样性使能快捷而容易地把视频引入板上和优化其运行算法。

与 VSK 一起提供的还有参考设计,其中一些使用 HDL 编写,其他的则用Xilinx System Generator for DSP 设计环境构建。为了去除通过各种视频接口引入数据并把它们发送到 Virtex-4 器件的复杂性,所以我们附带了一个视频接口块集库,使所有接口块集均可通过一个 MicroBlaze控制器来进行控制。

为了突出显示 VSK 的部分能力,我将对 MPEG-4 第 2 部分解码器演示设计进行说明。

MPEG-4 第 2 部分

该 MPEG-4 解码器演示系统由 FPGA 硬件评估平台、赛灵思 IP 核和嵌入式软件组成,并一起对工业标准编码视频位流执行解压操作。

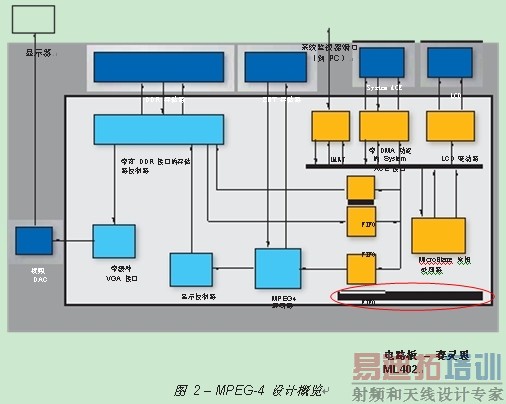

对于此设计,FPGA 被编程为执行解压和驱动视频显示之用。一个 Compact Flash 卡用于保存多个压缩视频流和 FPGA 配置位流。一个位于 FPGA 内的嵌入式处理器从 Compact Flash 卡读取位流,将其写入一个外部 DDR 存储器中,然后将其发送到 MPEG-4 第 2 部分解码器。然后通过视频 I/O 子卡,将解码器的输出重新格式化为要在外部监视器上显示的视频标准。

系统概览如图 2 所示。MPEG-4 解码器核、DDR 存储器控制器、颜色空间转换器、VGA 接口、宏块格式转换器、以及 MicroBlaze 软核处理器及相关外围电路,在 XC4VSX35 FPGA 中实现。而ZBT 存储器、DDR 存储器、System ACE技术、Compact Flash 连接器、两线式 LCD 显示器,和一个数模转换器,都是位于硬件平台上。 [p]

嵌入式处理器

视频系统一般需要有一个控制处理器。该处理器通常用于与主机系统通信,建立视频处理操作,计算系数,且一般作为低速率数据处理器运行。VSK 具有输入与输出源的视频标准,与 System Generator 硬件联合仿真能力相配合,可让您通过实时视频流快速测试和调试系统。

在该 MPEG-4 演示设计中,嵌入式 MicroBlaze 处理器用作总体系统级控制器,处理以下功能,如用户接口,从 Compact Flash 卡中读取压缩位流,将位流发送到 MPEG-4 解码器核,和监视所有系统状态标志等。

通过Xilinx System Generator for DSP,可大大简化 MicroBlaze 处理器整合到框架中的设计流程。您可以结合使用 Xilinx System Generator 与嵌入式开发套件 (EDK) 软件工具,去实现和仿真具有一个处理器和 FPGA 视频处理器功能、对实况视频流进行操作的系统。System Generator 自动生成软件驱动程序来支持用于向 System Generator 设计的数据读写。 两种方法学目前均支持集成一个 MicroBlaze 控制器:

System Generator 设计导出到 EDK 系统。当在 pcore(处理器核)导出模式下使用时,内存映射块和所有其他块被封装到一个 pcore 外设中。内存映射接口的软件驱动程序及文档也被生成并随该外设一起提供。

EDK 项目导入到 System Generator 设计中,以便进行硬件联合仿真。当在 EDK 导入模式下使用时,通过运行 EDK 导入向导将一个 EDK 文件导入到 System Generator 中。当导入向导完成后,该 EDK 系统象一个黑盒子的被拉入 System Generator 设计中。在导入过程中,EDK 系统通过快速单工链路 (FSL) 接口进行扩展,该接口用于与内存映射进行通信。

硬件联合仿真

观看最后输出视频是所有视频系统一项重要的质量测量指标。VSK 具有的输入与输出源视频标准,与 System Generator 硬件联合仿真能力相配合,可让您通过实时视频流快速测试和调试系统。

System Generator 提供了硬件联合仿真接口,可以将 System Generator 图编译为 FPGA 位流,并将该位流与一个新的运行时硬件联合仿真块相关联。当在 Simulink 中仿真该设计时,编译部分的结果将通过硬件而非软件来计算。

System Generator 提供了高速硬件联合仿真接口,允许Simulink 矢量或矩阵信号在单个事务中向 FPGA 硬件读出或写入。通过使用这些接口,您可以极大地减少仿真过程中 PC/硬件交易的数量,进一步加快仿真速度,超出传统硬件联合仿真所能达到的速度。利用以太网技术的普及和先进性,该接口提供给外部 FPGA 器件一种便捷和高带宽的联合仿真方法。

VSK 支持两种以太网联合仿真模式:

基于网络的以太网硬件联合仿真接口提供了通过 IPv4 网络基础设施到 FPGA 平台的联合仿真接入。由于 IPv4 网络分布广泛,因此该接口提供了一种直接与连接到有线或无线网络的远程硬件进行通信的方式。该接口特别适用于在远处的 FPGA 平台(如跨局或跨国),或多个设计者必须共享一个开发板的情况。基于网络的以太网接口支持工作在 10/100 Mbps 半/全双工模式。

点对点以太网硬件联合仿真提供了一种通过原始以太网连接进行的联合仿真接口。原始以太网连接指第 2 层(数据链路层)以太网连接,位于一个支持的 FPGA 开发板和一个 PC 主机之间,沿途没有路由网络设备。点对点以太网接口支持工作在 10/100/1000 Mbps 半/全双工模式。只要底层连接支持,还可支持在千兆位以太网连接的巨大框架。

VSK 包括软件、硬件、相机、电缆和一份详细的用户指南及参考设计。它包括一套限制版的 System Generator for DSP、ISE

软件,和嵌入式设计套件 (EDK) FPGA 设计工具,以及一个赛灵思 ML402-SX35 开发板,视频 I/O 子卡 (VIODC),CMOS 图像传感器相机,电源和电缆。

结论

凭借这一完整且易用的解决方案,视频基本套件是一个理想硬件平台来评估赛灵思 FPGA成为广泛的视频与成像应用领域。通过完全集成 Xilinx System Generator for DSP 软件并拥有其支持,VSK 可以充分利用新的高速以太网硬件联合仿真能力,实现编解码器、IP 和视频算法的实时系统集成、开发和验证。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于ISD4004语音芯片和AT89S52单片机的语音播报记事器设计

下一篇:基于PMAC2

PC

-

104运动控制器的AGV底盘控制系统