- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

在视频监控系统中使用FPGA进行视频处理

视频监控系统是火车站、机场、银行、娱乐场所、购物中心甚至家庭保安的重要组件。随着安全风险的增加,对视觉监视和记录事件的需求以多种使用模式激增。因此,新架构必须为横跨一整套日渐繁杂的视频监控系统要求的成本效益方案提供可扩展性。

上市时间的压力、新CODEC标准、日益广泛的要求(包括先进的目标探测、运动探测、目标跟踪和目标跟踪特性),这些不过是新型视频监控架构所面临挑战中的几项。伴随挑战而来的是对可扩展为不同性能范围的实现的需求。

视频监控和DVR系统

数字监控系统中的数字视频录像机(DVR)正在迅速采用先进的数字视频压缩。大多数DVR制造商从MPEG-4向H.264高清晰度(HD)CODEC转移,对更高分辨率和压缩速度的需求也随之增加。专用芯片(ASSP) 对大批量应用很有用,但缺少灵活性,开发成本高,而且开发时间较长;大多数高级数字媒体处理器则只能执行 H.264 HD 解码(而 H.264 HD 编码比解码还要复杂得多)。满足 H.264 HD 性能要求的最佳解决方案是使用一个 FPGA 加上一个外部 DSP 或数字媒体处理器。

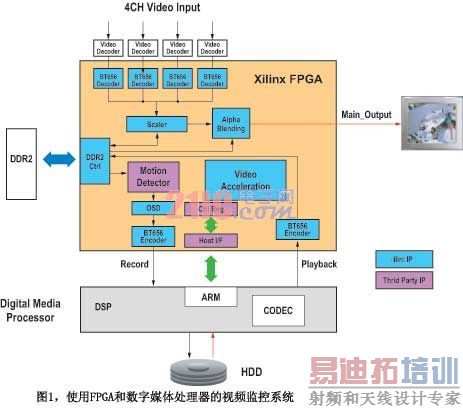

使用低成本的 Xilinx FPGA,可以更进一步提供运动探测、视频缩放、颜色空间转换、硬盘接口和DDR2存储器接口,还可以将两个 27MHz ITU-R BT656 数据流时分多路传输到一个 54MHz 数据流中,同时为 DSP 处理器提供视频加速。要将两个 ITU-R BT656 数据流多路传输到一个 ITU-R BT656 数据流中,仅需要一个通道视频端口来独立地传输完整的二通道视频数据。要为只有一个 ITU-R BT656 视频输入端口的数字媒体处理器提供接口,这种实现方法非常有用。图 1 所示就是这样一种建议架构的框图。 [p]

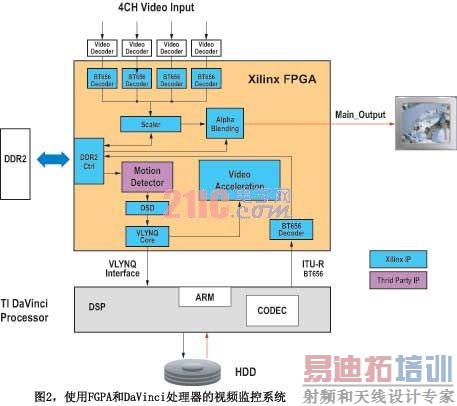

对于使用德州仪器公司 DaVinci 处理器(仅有一个 ITU-R BT656 视频输入端口)的 DVR 设计,需要一种更有效的实现方法将两个或更多 ITU-R BT656 数据流时分多路传输到一个 VLYNQ 数据流中,然后才能将其输送到 DaVinci 处理器。使用上述实现方法,就能用少得多的 I/O 引脚传输视频流,并且可以降低系统成本,因为器件的封装可以变得更小。图 2 所示为此设计的框图。

PC 扩展卡 DVR 系统

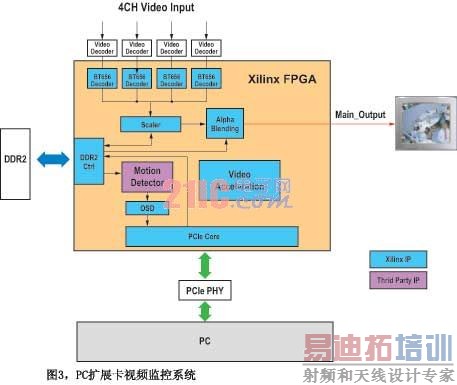

过去十年,PCI 总线为 PC 提供了很好的服务。然而,当今的 PC 扩展卡 DVR 系统所要求的带宽,已经大大超出了 PCI 总线力所能及的程度。未经压缩的视频数据(剥除空白帧之后)约为 165 Mbps。因此,在总体 PCI 带宽为 1 Gbps 的情况下,在一条 PCI 总线上最多只能混用 6 个未经压缩的视频采集或视频重放设备。如在扩展卡上使用 MPEG-4 CODEC 芯片组来缩小总线上的带宽,但这会增加成本,并且会受到现有MPEG-4芯片组的限制。

PCI Express (PCIe) 技术使流量大幅度提升。PCI Express 分解为多个通道。每通道在每个方向上包含一个差分对,每个差分对的数据流量为 2 Gbps。主板上的每个 PCIe 插槽都有自己的通道,这些通道不与其它任何插槽共享。各插槽的配置为 16 通道(亦称 x16)、8 通道 (x8)、4 通道 (x4) 或 1 通道 (x1)。PCIe 允许每卡提供的数据量从 x1 通道的 2 Gbps 到 x16 通道的 32 Gbps 不等。有了 PCIe 数据流量,就可以摆脱每张 PCI 卡 6 个未压缩视频通道的限制。

使用与图 1 所示同样的设计,可通过用 PC 替换数字媒体处理器并且经 PCIe 总线将视频流缓存到 PC 的方法,轻松快捷地实现 PC 扩展卡 DVR 系统。视频模数转换器产生四条独立的数字 ITU-R BT656 流,然后这些流被送入低成本的 Spartan-3 器件进行预处理。在 FPGA 中,视频数据剥除空白帧并同步,为 PCIe 适当打包,馈入 Xilinx PCIe 内核。然后,软件就可以读取并播放输入的视频,对其进行处理,或将其储存到磁盘。图 3 所示为 PC 扩展卡视频监控系统设计。

Xilinx 视频和图像处理算法

从多相视频转换器、二维 FIR 滤波器和屏幕显示到覆盖以及阿尔法混合等简单效果,再到格式和颜色空间转换,Xilinx FPGA 都是实时数字视频、图像处理和滤波的理想平台。表 1 列出了一些常用视频 IP 模块组的应用指南。

Xilinx FPGA的 DSP 处理能力支持非常高的分辨率(画质高达 1080p),并且可以缩小大型 DSP 阵列的尺寸。 [p]

现成的 IP

Xilinx 提供了视频 IP 模块组,以供在视频监控系统中快速设计、仿真、实现和验证视频和图像处理算法。其中包括设计 DVR 用的基本基元和高级算法。

此外,Xilinx 及其合作伙伴提供了一系列压缩编码、解码和编解码解决方案,从为需要快速实现的人提供现成的内核,一直到为希望通过高质量和低比特率使自己的产品与众不同的人提供构造模块参考设计和硬件平台。

将 Xilinx FPGA 用于某些编解码模块中的极其繁重的处理任务,可以支持多通道 HD 编码,节约宝贵的系统处理器周期,通过减少或排除 DSP 处理器阵列大量节约成本,并轻松地将从接口到进一步视频处理的更多功能和能力集成到系统中。最重要的是,FPGA 提供了可扩展的解决方案,从而能在相同的系统中支持不同的配置、额外的通道或新的编解码方案。

Xilinx FPGA 可通过强化系统逻辑和实现新外设进一步降低 DVR 系统成本。Xilinx 及其合作伙伴还为视频监控系统的快速发展提供系统接口:先进的存储器接口、PCI Express、德州仪器的 VLYNQ 和 EMIF 接口、硬盘接口以及 ITU-R BT656 接口。

Xilinx 工具简化设计

Xilinx System Generator for DSP 允许使用 Xilinx 视频 IP 模块组构建和调试 Simulink 中的高性能 DVR 系统。使用 System Generator 开发并实现视频处理算法,可以获得经过彻底验证和可以轻松执行的设计。

Xilinx 已开发出各种经过预测试的新型视频 IP 模块组。通过在 System Generator 内拖放模块轻松构建视频/影像系统,从而省下用 HDL 语言编写这些基本构建模块的宝贵时间。

为了处理从开发板到 PC 的庞大的视频数据流,System Generator for DSP 引入了另一种新颖的高速硬件协同仿真(通过以太网接口)。这种接口允许低延迟的高流量,事实证明它对于在 System Generator 环境中构建视频/影像系统极其有用。

另一种基于 MATLAB 语言的设计工具是 Xilinx 开发的 AccelDSP 综合工具,这是基于高级 MATLAB 语言的工具,用于 Xilinx FPGA 设计 DSP 模块。此工具可实现浮点到定点的自动转换,能生成可综合的 VHDL 或 Verilog 语言,并且可以为验证创建测试平台。还可以用 MATLAB 算法生成定点 C++ 模型或 System Generator 模块。AccelDSP 是 Xilinx XtremeDSP解决方案的一个关键组件,它集最先进的 FPGA、设计工具、知识产权内核、合作伙伴关系以及设计和教育服务于一体。

结论

在视频监控系统中,视频信号由多个摄像机生成。FPGA 从视频解码器接收 ITU-R BT656 格式的数字视频,然后将经过处理的视频输出到监视器进行显示,同时将其输出到数字媒体处理器或 DSP 进行压缩后存入硬盘。

利用 Xilinx FPGA可以使符合标准的系统有别于竞争对手的产品,同时还为应用获得最佳平衡。利用 Xilinx 的视频 IP 模块组可以轻松构建具有高度灵活性和可扩展性的 DVR 系统,从而既满足低端市场又满足高端市场。通过将 PCIe 内核与视频 IP 模块组集成到一起,可以开发出低成本的 PC 扩展卡视频监控系统。使用 Xilinx FPGA 中的 VLYNQ 内核,可以通过 Xilinx FPGA 将来自多部摄像机的众多视频流轻松地连接到 TI 的 DaVinci 处理器。

AccelChip 与 Xilinx System Generator 的集成将算法开发者青睐的基于 MATLAB 的算法综合与系统工程师和硬件设计者使用的图形设计流程结合起来。它使用丰富的 MATLAB 语言及其附带的工具箱创建复杂 DSP 算法的 System Generator IP 模块。通过合并使用这些工具,设计团队可以为实现而利用硬件建模这一最有效的手段,从而让算法开发者完全参与 FPGA 的设计过程,并且更快地完成更优质的设计。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:音频接口芯片TLC320AD50C与TMS320VC5402接口连接及软件实现

下一篇:基于ISD4004语音芯片和AT89S52单片机的语音播报记事器设计