- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于CPLD与μC/OS -Ⅱ的断路器智能控制单元设计

本文介绍的智能控制单元采用数字信号处理器(DSP)及嵌入式实时操作系统完成各种数据的处理、通信和算法的设计,而状态量的采集和执行信号输出将由复杂可编程逻辑器(CPLD)完成,主要是基于CPLD内部硬件电路结构的可靠性和对状态采集的实时性,该系统可以满足系统控制实时性及可靠性的要求。

硬件设计

TMS320F2812DSP介绍

TMS320F2812DSP是德州仪器公司(TI)推出的32位高性能数字信号处理器,它具有峰值运行每秒150万条指令(MIPS)的处理速度和单周期完成32×32位MAC运算功能,同时它还具有128k×16的片上Flash,18k×16的片上RAM以及大量的片上外设,包括A/D转换模块、2个事件管理器(EVA和EVB),CAN总线控制器、2个串行通信接口模块(SCIA和SCIB)、串行外设接口模块(SPI)、多功能串行接口(McBSP)及56个通用I/O口。该DSP以高效的32位定点CPUTMS320C28xTM为核心处理器,其开发既可使用C28x汇编也可使用ANSIC/C++语言。此外TI公司还提供有虚拟浮点数学函数库(IQ数学函数库)、快速傅里叶变换(FFT)算法函数库、滤波器库等,这些函数库可显著简化应用系统开发。

TMS320F2812强大的功能使其能满足嵌入式智能控制单元的设计要求。

系统硬件设计

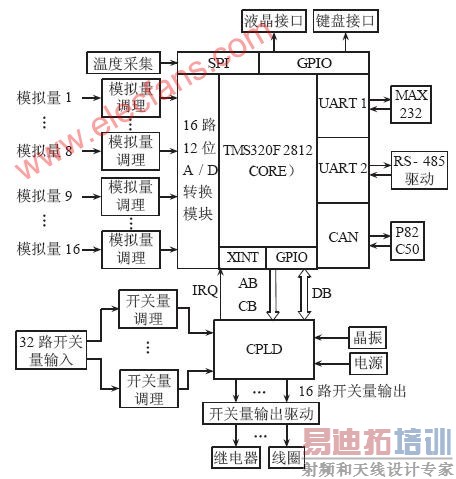

智能控制单元主要完成的任务包括:处理主控模块控制命令、监测母线电力参数、温度采集、保护控制算法的实现、检测开关量的状态、开关量的输出控制及与监控中心的通信等。为了实现上述功能,并充分利用DSP TMS320F2812强大的外设功能及嵌入式操作系统的优点,DSP主要完成模拟量采集、数据处理、算法实现、温度采集、通信及命令处理。同时为了状态的快速检测和输出执行信号的可靠性,将由CPLD完成状态量的监测、与DSP的通信、状态信号的输出及外部高电压电路的控制。系统结构如图1所示。系统硬件的设计包括各调理电路、CAN总线通信驱动、RS-232总线驱动和RS-485总线驱动及CPLD内部电路的设计。

图1 智能控制单元系统结构图

调理电路设计

调理电路包括交流电压采集调理电路、开关量采集调理电路、开关量控制驱动电路。交流电压信号的采集使用F2812 内置12位A/D转换模块,该模块本身具有采样保持电路且要求输入电压的范围为0~3V,因此设计了由电压互感器、电流电压转换电路和RC滤波构成隔离电路和由放大、电压抬升、电压跟随器及限幅组成的调理电路,可将220V/50Hz的电压信号转换成0~3V的电压信号。

开关量的采集采用CPLD实现。由于开关量经常出现抖动问题,因此其调理电路需采取措施去除开关抖动。在其调理电路中,采用电容C滤除输入信号中的尖峰电压(主要针对高频干扰),12V的稳压二极管滤除干扰信号(主要针对低频干扰),光电耦合器是为了防止外部信号影响内部电路的工作;二极管VD用于保护光耦中的发光二级管以免发光二极管被反向击穿开关量控制信号经CPLD的I/O管脚输出。输出信号经过光耦器件TLP127驱动外部的高电压器件动作。

由于该智能控制单元主要是控制断路器的关合,而断路器的关合过程中会产生强的电磁效应,如果直接由DSP的GPIO管脚驱动,外部电磁干扰有可能使DSP的程序跑飞或使DSP复位,严重影响执行后果,所以系统中开关量的输入/输出均由CPLD完成,其可靠程度将加强。

通信模块

F2812具有增强型CAN控制器eCAN模块,其完全支持CAN2.0B协议,性能较之已有的DSP内嵌CAN控制器有较大的提高,在CAN总线通信时,数据传输更加灵活方便,数据量更大、可靠性更高、功能更加完备,因此本设计采用CAN总线实现智能终端的通信。通信模块的硬件设计主要是CAN总线驱动电路的设计,选用飞利浦公司的CAN通信收发器PCA82C250作为F2812的CAN控制器和物理总线间接口,以实现对总线的差动发送和接收功能。为防止干扰信号的引入,设计中采用高速光耦6N137对F2812及物理总线隔离。RS-232的驱动芯片直接选用MAX232驱动芯片,而RS-485的驱动芯片采用SNLBC184,同时为了防止干扰信号进入,设计中采用光耦TLP521对F2812和RS-232及RS-485总线驱动芯片隔离。 [p]

CPLD模块设计

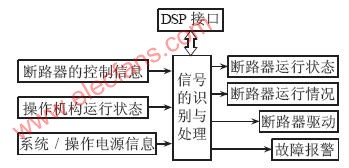

在该智能控制单元中,CPLD是一个重要的组成部分,由CPLD组成的状态采集及输出执行系统可以独立工作,主要是控制断路器的异步关合,接受各种输入的按键操作和状态的输入/输出。同步控制时,CPLD接收DSP传送的动作命令,即可以执行同步关合操作,同时,当状态发生变化时,CPLD将发出中断信号,由DSP读取状态并且作出相应的处理或传送给监控中心。CPLD的输入信号主要有异步的关、合、复位输入,断路器的位置信号、开关小车的位置信号、失压跳闸、过流跳闸、系统电压信号等。其信息输出模块的功能主要是显示断路器是否具备可以操动的条件、断路器的合/分闸状态、断路器的动作执行情况、输出控制断路器动作命令等。CPLD的控制框图如图2所示。CPLD作为一个单独的控制执行机构,通过编写相应的VHDL代码,即可以生成相应的操作电路,包括对各种输入信号的锁存、判断和处理,以及对各种命令信号的执行,对输出信号的控制。

软件设计

软件设计包括系统软件设计和应用软件设计。

图2 CPLD的控制框图

系统软件设计的主要任务是实现μC/OS-Ⅱ在F2812上的移植;应用软件设计的主要任务是系统功能的实现。

系统软件设计

μC/OS -Ⅱ简介

本设计系统软件采用源代码公开实时操作系统μC/OS-Ⅱ,它是一个基于优先级的、可移植、可固化、可裁剪、占先式实时操作系统,其绝大部分源码是用ANSIC写的。

μC/OS-Ⅱ在F2812上的移植要使用μC/OS-Ⅱ,首先要把内核成功移植到所使用的CPU上。μC/OS-Ⅱ在F2812上的移植工作包括4个内容。

a.在OS_CPU.H中定义与处理器相关的常量、宏及数据类型。例如关中断和开中断的定义分别为#defineOS_ENTER_CRITICAL()asm“DINT”及#defineOS_EXIT_CRITICAL()asm“EINT”。

b.调整和修改头文件OS_CFG.H,以裁减或修改μC/OS-Ⅱ的系统服务,减少资源损耗。例如,

#defineOS_MBOX_EN0即禁止使用邮箱相关的代码。

c.编写C语言文件OS_CPU.C。由于本设计中未用到其他几个函数,因此这里主要完成函数OSTaskStkInit()的编写。OSTaskStkInit()用来初始化任务的堆栈结构,使其看起来象刚发生过中断并将所有的寄存器保存到堆栈的情形一样。

d.编写汇编语言文件OS_CPU.ASM。本文件包括4个子函数程序:OSStartHighRdy()(运行最高优先级任务),OSCtxSw()(任务级的任务切换),OSIntCtxSw()(中断级的任务切换)和OSTickISR()(μC/OS-Ⅱ时间节拍中断函数),这是μC/OS-Ⅱ移植中的重点和难点,这几个函数的合理实现,是保证μC/OS-Ⅱ运行的基础。

上述工作完成后,μC/OS-Ⅱ就可以运行了。

应用软件设计

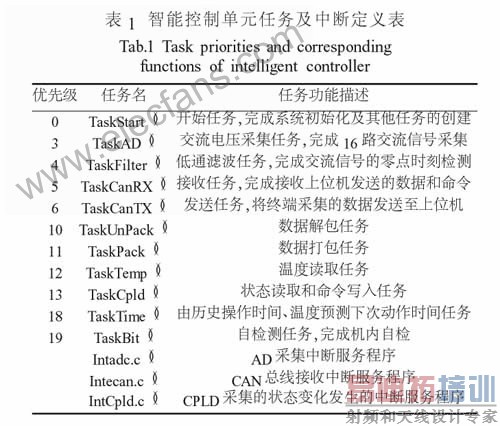

根据智能控制单元的功能要求,将系统分为交流电压采集模块、数据处理模块、断路器动作时间预测模块、通信模块、以及与CPLD的接口模块共11个任务和3个中断来实现,每个任务根据其实时性的要求并参照单调执行率调度法RMS分配一定的优先级、任务及中断的定义,如表1所示。

[p]

优先级最高的是开始任务(TaskStart),这是系统启动后运行的第1个任务。在该任务中要完成系统及相关外设的初始化,并进行必要的自检测,然后创建其余的各个任务。在完成其余各个任务创建之后,该任务要删除自己,把系统资源让给其他任务,整个系统开始正常运行。该任务的示意代码如下:

/*系统及外设初始化*/

/*系统自检测*/

/*创建各个任务*/

StartCpuTimer2();/*启动时间片*/

OSStatInit();/*统计任务初始化*/

创建智能控制单元的各个应用任务;

KickDog();/*WatchDog复位*/

OSTaskdel(OS_PRIO_SELF);/*删除开始任务*/

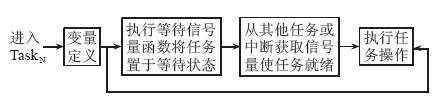

除了TaskStart()之外,其余各任务模块的结构都是无限循环体,图3给出了一般任务流程图。

图3 任务流程图

任务通信与同步

μC/OS-Ⅱ提供了5种用于数据共享和任务通信的方法:信号量、邮箱、消息队列、事件标志及互斥型信号量。信号量可以控制共享资源的使用权,也可以协调外部事件与任务的执行,提供了任务间通信、同步和互斥的最快通信,μC/OS-Ⅱ提供了3种类型的信号量,即二进制型、计数型和互斥型。事件标志可使任务与多个事件同步,若与多个事件的任何一个同步,称为独立型同步;若与多个事件都同步,称之为关联型同步。邮箱是一种通信机制,它可以发送一个指针型的变量,该指针指向一个包含了特定消息的数据结构。消息队列是另一种通信机制,它可以使一个任务或中断服务子程序向另一个任务发送以指针定义的变量,具体应用不同,每个指针指向的数据结构也不同。互斥型信号量是一种特殊的二进制型信号量,主要用于解决内在的互斥问题,减少实际应用中所必需的优先级翻转。在设计智能控制单元软件时,充分利用了μC/OS-Ⅱ提供的这些通信机制,以协调各独立任务的运行。

通信协议的实现

F2812提供了标准的CAN2.0B总线协议,而此协议是一种物理层协议,因为该智能控制单元用于电力系统控制中,电力系统通用的应用层协议主要有CDT,MODBUS,DNP3.0等,在本设计的过程中应用层的协议将采用MODBUS协议,通信协议的实现比较复杂,但是由于采用了实时操作系统,通信协议的实现可以由操作系统统一管理,主要由数据的接收、发送、打包、解包任务完成。

总结

a.设计中使用具有多外设的新型高性能DSPTMS320F2812芯片,大大减少了系统硬件设计的工作量,缩短了开发周期。设计中采用了DSP最小系统与调理电路分开设计的方法,并且在DSP最小系统设计中采用多层板结构,并大量使用了贴片元件,以提高系统的稳定性及电磁兼容性。

b.作为基于优先级调度的嵌入式操作系统, 任务优先级的合理分配对系统的正常运行至关重要。在本设计中,对任务优先级的分配首先考虑是满足系统实时性,其次在同等条件下再考虑任务的执行频度,通过反复调整,最终确定优先级的分配表1。

c.本课题利用了基于CPLD的执行电路设计,由于CPLD的内部硬件结构的可靠性及快速的反应,非常适合电力系统控制,因此采用全CPLD(或ACTELFPGA)应是一个研究方向。

d.F2812作为TI公司推出的2000系列的新成员,目前在国内的开发和设计还处于摸索阶段,本文中所提出的基于TMS320F2812+μC/OS-Ⅱ的系统设计思想会对F2812的学习和使用起到一定的促进作用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于TMS320C5515设计的心电

(

ECG)

MDK开发技术

下一篇:基于FPGA的可重构系统及其结构分析