- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

恐怖:破解版的PADS9.4.1有严重的软件BUG问题

但当我对PCB的几个走线进行调整,增加了几个测试点后,再进行全面铺铜,然后重新进行一次“Verify Design”进行间距、连通性检查,结果死活不通过,总是提示间距有问题。

头大,没动到的地方提示间距错误,奇怪得很!我可以确定的是,整个工程的设置没有任何改动,但修改之前检查可以通过,修改之后检查却有间距错误的问题!

于是,我打开了修改之前和修改之后的两个PCB工程进行对比,尤其是检查提示错误的地方。

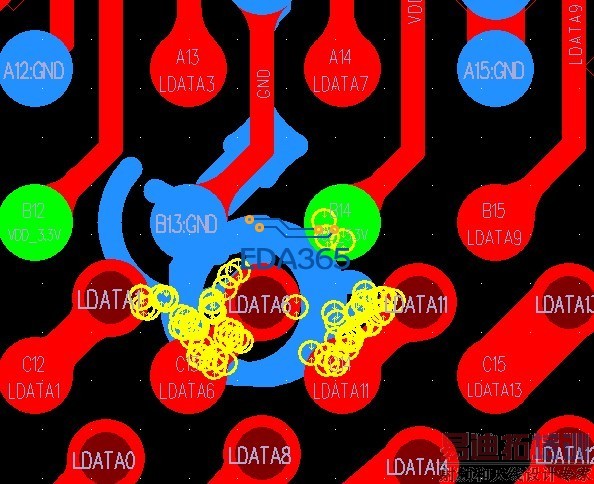

最终发现:铺铜出了问题!铺铜时间距不够的地方,竟然也添加了花盘!(注:我在Termals选项中,把Spoke minimal一项设置为4,即花盘将产生4根连线。)

此外,有些地方,还乱七八糟的铺上了铜。见下图。

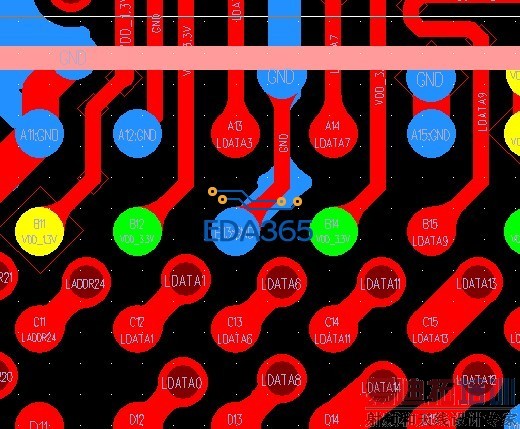

正确的铺铜情况:

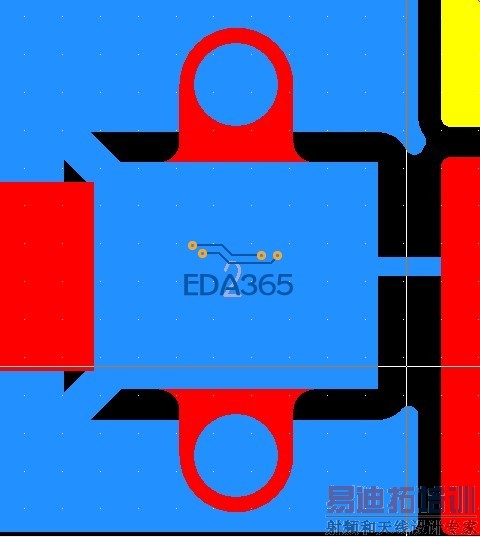

错误的铺铜情况:

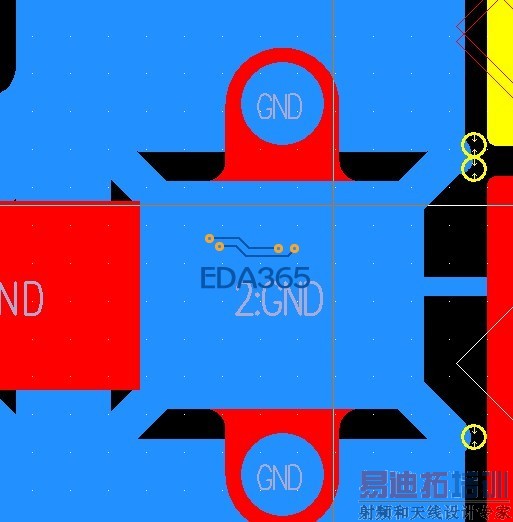

生成的Gerber文件,很明显的可以看到错误的铺铜:

太垃圾了!从PADS2005一路走来,PADS的软件BUG不断!

先是PADS2005在编辑封装库或画图时,容易导致软件崩溃;

再到PADS2007在画图过程中容易出现崩溃死机;

到现在的PADS9.4.1目前发现的调整走线时过孔直接丢失的情况,以及这次发现的铺铜乱七八糟的错误。

我还没用过一个真正稳定可靠的版本。是因为使用破解版没交钱吗?

真后悔当年学PADS啊,要是学allegro+Orcad就好了。

本人是做软件开发的,偶尔花花电路图,实在是不想再学一款新的画图软件啊!

先检查一下文件,命令"i"

好像没有碰到过这种情况哦,楼主可否将文件上传,让大家也试试,以免以后也出现这种问题。

我也遇到过这种问题,我的还是2007正版软件呢,郁闷的很,软件BUG啊

這是習慣問題,修改文件以後,不管如何銅箔一定要重新再鋪一次。

问题是,不管自己怎么铺铜,错误都还是存在的,通过软件Verify检查错误依然存在(其实错误的铜皮用肉眼都能看得到!)。只能手工的编辑铜皮,删除多余的那些铜皮,但这种手工的做法很低级啊。

4楼的朋友也遇到过同样的问题,而且还是正版软件,看来,这确实是软件的问题了。

我怀疑是使用了9.3的破解程序带来的BUG,所以刚才又重新在EDA365下载了一个新的9.4.1专用的Crack破解程序,在虚拟机中重新安装了一个PADS9.4.1来测试,问题依旧,心拔凉拔凉的。

同志们啊,每次出Gerber之前,一定要“Verify Disign”软件检查一遍啊,否则,后果严重!

我把PADS9.4.1的PCB图导出PADS2007格式的.asc文件,然后分别做以下两个测试:

1)从PADS2007上导入.asc文件,重新铺铜后,“Verify Design”检查完全没有问题了。看来,这个问题在PADS2007里面是不存在的。

2)重新让PADS9.4.1上导入.asc文件(看似有点多此一举),同样进行重新铺铜,然后“Verify Design”检查竟然也完全没有问题。通过肉眼观察,也没有看到错误的铺铜出现了。

到目前为此,软件的BUG依然是可以确定的,但通过这两个步骤,似乎由PADS9.4.1直接点击打开PADS2007的PCB文件时,可能在转换过程中出现什么问题(2楼的朋友提示检查文件的命令我也试过了,一直提示没有问题)。

经过这些实验,当大家遇到这样的情况时,姑且先用第2个步骤的方法去折腾一下,至少可以暂时解决这个问题。

感叹一句,用了几年的PADS,它的稳定性真的不敢恭维啊!

这里如果有用过OrCAD+Allegro (即Cadence)的朋友,请报告一下Cadence的稳定性,这样,好让公司的未来选择一个稳定一点的平台,PADS我是再也不敢推荐使用了。

谢谢楼主的经验分享!

我一直使用9.3,没有发现异常。

我遇到过一个有bug的版本,那就是pads2007sp1,这个版本查不出开路。

出光绘前先灌铜和verify design是设计人员的常识和习惯。在设计的过程中经常要进行数据整理,快捷键:I

9。3以上版本我还没使用。以后有机会也尝试一下

"查不出开路"????????????

这个问题很严重啊!一旦量产,就完蛋了。

楼主,我也遇到过这样的问题。用07修改了一个PCB之后,pour之后ddr那里有大片的类似你的现象。然后尝试了用powerpcb铺铜和用9.3铺,powerpcb是一样的错误,9.3会报错退出。最终的办法是手动修改错误地方的poor的边沿,只能这样。感觉pads软件对于铺铜是弱点,不过这个错误也能verify出来,改了就行了。我司还出过这样的事故:pads出gerber,在地层居然少了一个孔,导致电源地短路。所以现在每次出gerber都把pcb和gerber文件用photoshop对一遍看是不是一样。呵呵

10楼的朋友,感谢你的回复啊。让我又收集到更多的PADS BUG信息。

这次的改动,我最后也是通过手动把多余的铺铜删除,虽然这种做法比较低级,但也只能这样了。准备打样10片,再去量产,不敢随便冒这险啊。

关于出Gerber丢失过孔的问题,我到目前为此倒还没出现过。但在9.4.1版本,直接拖走线对它进行位置调整的时候,这条走线上的过孔有时候会突然消失,好在Verify检查时,如果过孔消失,会有不通的错误报告,至少还可以挽回。但你这种出Gerber丢失过孔的话,用肉眼去检查还是不太靠谱的,估计只有打板出来之后才能知道错误。

大家把遇到过的PADS软件BUG都报告一下啊,为自己也为别人避免带来不必要的麻烦。

你们公司不先打样回来测试吗?

,您上面说的敲快捷键I进行数据整理是起什么作用?

另外,您用的是9.3三合一精简版还是完整版?

PADS想说爱你不容易, PADS 9.5如果用中文界面的话一改器件标号字体就崩溃. Mentor买入后新技术增加较慢, 我已经开始学习Allegro, 和PADS比操作思路完全不同, 非常痛苦ing...

A的Hotfix更新很周到,16.3现在还出补丁, 国内正版用户多可以分享给我们穷人; 而M的update只能在supportnet下载, 我看到EE7.9.4已经有第3个update但是搜遍网络都找不到下载,BUG无法及时修复破解了也只能用于学习不敢工作很无奈, 我2003年学习过WG的, 现在也只能转投A了

pads9.3.1+update2遇到过无法修改过孔为,一旦移动过孔软件就遇到问题退出,最后是转移到router保存后再转回layout,让pads自己把错误修复了就好了,你可以试下这个方法能否解决你的问题

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:关于电源的滤波电容的放置,请指点

下一篇:求助结构网表都导好了,下一步是做什么?