- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

pads中关于ECO TO PCB 的问题 急死我了

在原理图中,FPGA的PART TYPE是由多个DCEAL组成的,在pcb布线过程中难免会在不同的管脚间进行网络的交换,当把所有要连到FPGA的线整齐地放到它周围,就等着调整FPGA管脚后,才发现,原来FPGA管脚网络改变后,从LOGIC ECO 到 LAYOUT后所有原来放置好的线全部被删除,也就是说,凡是调整过的网络的连线都被删除了,这样会给布线带来很大的麻烦,不知道大家是怎么样做的?

谢谢大家回答咯

可以ECO PCB TO LOGIC

這樣可能要好點

以后要慢慢抛弃pads了,太不好用了。问题还很多,ECO模式删个器件,GND的孔全掉了;平时删个孔如果其他的地孔不保护,如果没有线连接的话也TM全掉了,什么破软件。

将FPGA周围连好的线做成reuse。然后再进行eco to pcb.

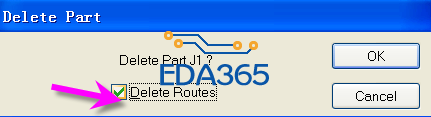

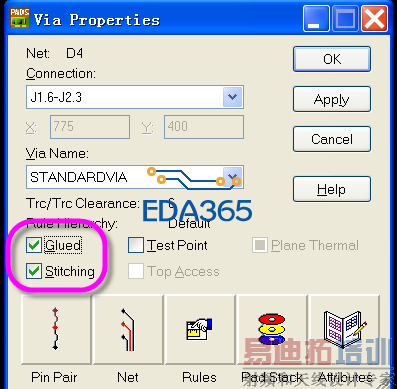

kdc252626658 发表于 2012-12-18 12:06 删除器件前,也可将整板的过孔进行glued和stitching 问题:删个孔如果其他的地孔不保护,如果没有线连接的话也全掉了 JIMMY,霸气! 多谢指教,是自己太浮躁了。 上边这个 delete routes 勾勾,我都勾掉的,但删除器件,相连的网络还是经常回掉,掉的非常干净,只能重新走一遍。哎,是我的器件有问题? 可以将相关的PCB和最新原理图发给我试试看。 可以说是这方面的权威了啊 ,你好! RC01_V1.0-PCB&SCH.rar[/url] 那是,膜拜!

答:只要你的过孔不是直接复制,而是通过select nets,选中某个器件的GND网络的管脚后来add via的,都不会掉。每个软件都有自己的特点,如果要用它,就只有去熟悉它的脾性才能更好的驾驭它。要不然,建议你换其他软件。

您能帮我检查问题真是十分荣幸!pcb是pads2007画的,原理图是用orcad画的。把原理图映射到pcb是用到导出网表的方法。

原理图几经易手,画的比较凌乱,器件命名也很不规范,勿见笑。

举例:拿删除连接器U6来说,在eco模式下删除,即便勾掉delete routes,软件同样会提示与之相连的网络会删除(点到点的会删除,有分支的则不会)。

多谢释疑!

还有另外一个问题,如果我的板子原本6层,后改版降为4层,不知有没有简便的方法操作。我之前的做法是把要减掉的两层的所以信息全部删除,包括贯穿的VIA才能降层成功,否则总是提示要删除的层上还有东西。因为动作实在过大,之后我就不减层了,只是是布线的时候空出某两层,一根线都不走,一片铜都没有,出gerber的时候只出有效的层的信息给板厂,这样也可以解决问题。但总有一丝遗憾。出的gerber中,过孔的信息显示的还是6层,总是要给板厂解释。不知道是否有其他简便的方法?还请多多指教!谢谢!

附件丢了,补上。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...