- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

采用硬件加速发挥MicroBlaze处理能力

Xilinx客户针对这种处理器设计所要求的两个实际应用案例可说明MicroBlaze在硬件加速方面的作用。本文以 Spartan 器件为重点,比较 FPGA 解决方案和标准控制器内核,展现我们能够达到的性价比。这一方法同样适用于Virtex FPGA。

案例1:实施位反转算法

在第一个应用示例中,假定MicroBlaze处理器的运行速度仅为50MHz。采用 Spartan-3或Spartan-6器件可轻松实现这一速度。诸如本地存储器总线(指令和数据,LMB)以及处理器本机总线(PLB)等所有内部总线的运行速度均达到50MHz。为简单起见,假定没有连接外部DDR存储器。

现在假设客户想要在这个CPU上实施位反转算法。MicroBlaze自身没有通过硬件直接提供这个功能。再假定每秒需要完成2万次位反转操作。

要解决这个问题,大多数客户首先会采用纯软件方案,因为这样可轻松地实现想要的功能。而且如果性能足够高,无需进行任何修改。

为此,让我们先从简单的软件算法出发,实施简短精悍的解决方案。结果确实简单、精巧而且容易理解,不过效率很低。

unsigned int v=value;

unsigned int r = v;

int s = sizeof(v) * CHAR_BIT - 1;

for (v >>= 1; v; v >>= 1)

{

r <<= 1;

r |= v & 1;

s--;

}

r <<= s;

return r;

这段程序运行相当顺利,不过就算在专门针对速度优化的MicroBlaze(使用五级流水线)上运行处理一个32 位字的算法,也用了220个周期。要执行2万次位反转操作,在速度为50MHz的MicroBlaze上约需88ms。

客户试图采用略有不同的方法来优化算法,但仍作为纯软件解决方案来实施。

要进一步提升性能,就要采用纯硬件解决方案,通过一种新的方式来让硬件加速器充分发挥性能。

为了加速这种基础操作,只需要在MicroBlaze快速单工链路(FSL)上连接一个非常简单的内核。标准FSL实施方案使用FSL总线(包括同步或异步FIFO)将数据从 MicroBlaze内核传输到FSL 硬件加速器IP核。带FIFO 的FSL总线与FIFO可对上述两者间的数据存取进行去耦。

如果采用带FIFO的标准FSL总线,则一般情况下执行时间为4个周期:一个周期用来将MicroBlaze上的数据通过FSL写入FIFO;一个周期用来将数据从FIFO 传输到FSL IP;一个周期用来把结果从FSL IP传送回 FSL总线的FIFO中;最后一个周期则负责从FSL总线读出结果并传输至 MicroBlaze。

MicroBlaze到FSL总线的连接以及FSL总线到FSL IP的连接可在EDK的图形视图中轻松创建。

这样代码要长得多,效率也有大幅度提升,但时间还是太长了,执行2万次操作现在仍然大概需要52ms。

随后客户在互联网上进行了一些调查,找到一种更好的算法,把代码改编为:

unsigned x = value;

unsigned r;

x = (((x & 0xaaaaaaaa) >> 1) | ((x

& 0x55555555) << 1));

x = (((x & 0xcccccccc) >> 2) | ((x

& 0x33333333) << 2));

x = (((x & 0xf0f0f0f0) >> 4) | ((x

& 0x0f0f0f0f) << 4));

x = (((x & 0xff00ff00) >> 8) | ((x

& 0x00ff00ff) << 8));

r = ((x >> 16) | (x << 16));

return r;

这个代码看起来效率高,短小精悍。而且它不需要会造成流水线中断的分支。它在这个核心系统上运行只需29 个周期。

不过这个算法需要在1 、2、4、8和16位之间进行移位操作。我们在MicroBlaze的属性窗口中激活桶式移位器。不管移位操作的长度如何,采用桶式移位器可允许我们在一个周期内完成移位指令。这样可以让纯软件算法在 MicroBlaze上运行得稍快一些。

激活MicroBlaze硬件上的桶式移位器可将处理算法所需时间缩短到22个周期。与第一个版本的软件算法相比,此算法得到了显著改善。目前采用此算法,执行所有 2万次操作只需8.8ms,效率提升了10倍,不过仍未达到客户要求。

不过效率还有提升的空间。算法中的时延非常关键,应尽可能地缩短。但在我们的实施方案中,采用两根FSL总线仍需要四个时钟周期。不过我们可以通过将 MicroBlaze与硬件加速器之间的现有连接方式改为直接连接,便可将时延减半,缩短至两个时钟周期。这样一个周期用于将数据写入 FSL硬件加速器IP,而另一个周期则负责读回结果。

在采用直接连接方式时,需注意几个问题。首先,协处理器IP应存储输入,并以寄存方式提供结果。请注意在执行此操作时没有使用带FIFO的FSL总线。

此外,以不同时钟速率运行 MicroBlaze和FSL硬件加速器IP 容易发生问题。为避免发生冲突,设计人员最好将MicroBlaze和 FSL硬件加速器IP的运行速率设为一致。

不过,如何在不使用FSL总线的情况下将MicroBlaze和FSL硬件加速器IP直接连接起来呢 这很简单,只需将MicroBlaze和硬件加速器的数据线连接起来即可。如果需要,可再添加握手信号。

例如,使用位反转IP,只需一个写入信号即可。IP会一直很快运行,足以对MicroBlaze的任何请求做出及时响应。

IP本身非常简单。以下是摘录 VHDL 代码中的一段:

architecture behavioral of

fsl_bitrev is

-- data value sent by microblaze:

signal data_value :

std_logic_vector(0 to 31) := (others=>'0');

begin

-- bitreversed value to write back:

FSL_M_Data <= data_value;

process(FSL_Clk)

begin

if rising_edge(FSL_CLK) then

if (FSL_S_Exists = '1') then

-- create the bitreversed data:

data_value(0) <= FSL_S_Data(31);

data_value(1) <= FSL_S_Data(30);

data_value(2) <= FSL_S_Data(29);

...

data_value(30) <= FSL_S_Data(1);

data_value(31) <= FSL_S_Data(0);

end if;

end if;

end process;

end architecture behavioral; [p]

如果在两者之间没有使用 FSL总线的情况下添加这个IP,您必须对项目的MHS文件进行如下修改:

BEGIN microblaze

...

PARAMETER C_FSL_LINKS = 1

...

PORT FSL0_S_EXISTS = net_vcc

PORT FSL0_S_DATA = FSL0_S_DATA

PORT FSL0_M_DATA = FSL0_M_DATA

PORT FSL0_M_WRITE = FSL0_M_EXISTS

PORT FSL0_M_Full = net_gnd

END

BEGIN fsl_bitrev

PARAMETER INSTANCE = fsl_bitrev_0

PARAMETER HW_VER = 1.00.a

PORT FSL_S_DATA = FSL0_M_DATA

PORT FSL_S_EXISTS = FSL0_M_EXISTS

PORT FSL_M_Data = FSL0_S_DATA

PORT FSL_M_Full = net_gnd

PORT FSL_Clk = clk_50_0000MHz

END

现在效率显著提高。硬核仅在两个周期内可完成位反转操作:一个周期用于把数据写入IP,另一个周期则负责读回结果。处理2万个位反转操作现在只需0.8ms。

与最初采用的算法相比,效率提升了110倍。与效率最高的最新软件算法相比,此算法仍使系统性能提升了11倍。

当然,本例只有在您的CPU不提供位反转寻址功能的情况下才有效。大多数 DSP都有此功能,但大多数微控制器都不具备这个功能。具备增加这个功能的特性可大幅度提升这种算法的处理速度。

虽然修改不大,但收效十分明显。我们甚至将代码压缩到两个字大小。当然,现在硬件要求增加一些芯片。不过以此为代价获得比任何标准微控制器更高的速度,是值得的。

案例2:高速浮点性能

现在我们给出另一个 MicroBlaze算法加速示例。一个客户声称他的浮点处理在MicroBlaze系统上运行非常慢。他使用的算法可采用简单的环路同时得出几个结果。

for (i=0;i<512;i++) {

f_sum += farr[i];

f_sum_prod += farr[i] * farr[i];

f_sum_tprod += farr[i] *

farr[i] * farr[i];

f_sqrt + =

sqrt(farr[i]);

if (min_f > farr[i]) { min_f =

farr[i]; }

if (max_f < farr[i]) { max_f =

farr[i]; }

}

所有数值均是单精度浮点值。我们首先想到的是最基础的一个问题:浮点单元 (FPU) 激活了吗 检查项目设置后,我们发现FPU仍然处于未启用状态。这就是为什么永远无法计算出这几个数的原因。FPU可在 MicroBlaze属性设置中加以激活。

FPU支持共有两种。我们也选择扩展FPU (Extended FPU)来支持求平方根运算。现在,在50MHz 的MicroBlaze上需要 1,108,685个周期才能完成 512个值的全部循环。查看生成的汇编程序代码后,可以了解到创建平方根是仍然在使用数学库(Math-lib)功能。其在数学功能中的定义为:

double sqrt(double);

不过客户使用平方根函数仅为处理浮点数值。因此,MicroBlaze FPU定义了一个新的函数来取代原来的函数,解决这个问题:

float sqrtf(float);

把表达式f_sqrt += sqrt(farr[i])变为f_sqrt += sqrtf(farr[i]),就会调用MicroBlaze内部的FPU内部平方根功能。现在执行代码只需要35,336个周期。特别是与第一个根本没有使用FPU的方案相比,我们再次通过小小的调整就实现了31倍的提升。在相同的执行时间内,可能需要大约1.5GHz的CPU才能给出上述这些结果。

不过客户仍不满意,客户要求更高的速度。在这种情况下,把算法从浮点运算变为固点运算并不适合。因此,我们开发了一款新型专用硬件加速器(新型FSL IP)来加快对循环的处理。

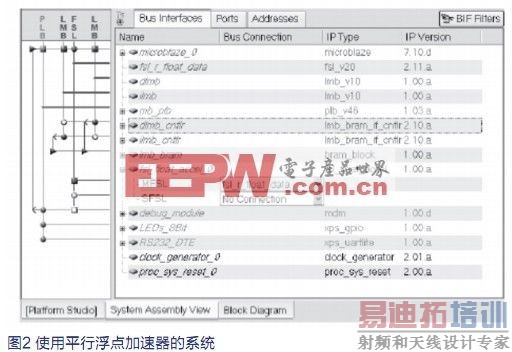

新的FSL IP使用CORE Generator模块浮点_v4_0来为4x ADD、2x MUL、1x GREATER、1x LESS和1x SQRT等操作创建9个示例。所有这些示例都可以实体化,并对相同的输入数据进行完全并行处理(图2)。

FSL IP中实例的创建带有部分时延,但吞吐率仅为1。这要求为加速器内部的控制器硬件准备更多的芯片,不过这样可以在每个时钟周期内向协处理器提供新数据。

在取回结果前,只有在处理循环末端才需要增加周期。

我们采用直连方式把MicroBlaze连接到FSP IP时不需要FIFO。传输的所有数据都将缓存在IP内,并随即加以处理。

从FSL IP返回到MicroBlaze的连接是使用FSL总线创建的。由于我们必须发回一些结果,因而这更加容易实现,而且可以更加简单地在IP内完成。部分CoreGen模块有一些已被添加到执行时间中的时延,并被getfsl()调用完全覆盖。MicroBlaze只需要等到所有结果都存入FSL总线FIFO。不过,只要数据率是1,即可完全实现所要求的吞吐率。

FSL总线的额外延迟仅会占用为数不多的一些周期。使用FSL硬件加速器的C代码如下:for (i=0;i<512;i++) {

putfsl(farr[i],fsl0_id);

}

// get the min,max values:

getfsl(min_f,fsl0_id);

getfsl(max_f,fsl0_id);

// get the sum and products:

getfsl(f_sum,fsl0_id);

getfsl(f_sum_prod,fsl0_id);

getfsl(f_sum_tprod,fsl0_id);

getfsl(f_sqrt,fsl0_id);

算法的最终实施仅需大约4,630个周期,而且依然是全浮点实施。

硬件需要本来应该用于实施硬件加速器的更多芯片才能并行计算出所有结果。不过与扩展FPU实施方案相比,我们最终提升了大约7.6倍。否则,如果使用标准处理器来替换这个50MHz的处理器,可能需要大约380MHz的CPU才能胜任(假设硬件自带有浮点平方根函数)。

更为显著的是与使用PFU的最初方案,而非平方根函数的对比效果:总体提升了大约239倍。这种效果可能需要12GHz左右的浮点处理器才能实现。

如上述例子所示,有时候小小的调整就会显著影响算法的处理效果。实施这些调整,可以让您的50MHz MicroBlaze系统与高性能DSP相媲美。

首先,找出执行时间过长的核心算法,然后对其加速——通过简单调整软件,使用硬件,或使用硬件加速器进行更为复杂的调整。如此一来,您的处理器系统会强于标准控制器。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于AIC23语音接口及AGC方法的实现

下一篇:LED智能照明控制系统的设计