- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于TMS320C6701的自适应滤波器设计与调试

录入:edatop.com 点击:

对于系数固定的FIR、IIR滤波器所具有的特性是确定的,对于输入信号可根据这个滤波器产生相应的输出,即先有了滤波器系数,然后决定相应的输出值。但有些实际应用往往是反过来要求的,即对滤波器输出的要求是明确的,而滤波器的特性却无法事先知道。如在通信系统中,信号通过信道传输,由于信道频率特性的影响,接收信号失真畸变而引发码间干扰,这将严重影响通信质量,为此,需要在系统中插入一种可调的滤波器以减小码间干扰,这种系数可调的滤波器即为自适应滤波器。其参数可以自动地按照某种准则调整到最佳滤波。自适应滤波器已广泛应用于系统模式识别,通信信道的自适应均衡,雷达与声纳的波束形成,减少或消除心电图中的周期干扰,噪声中信号的检测、跟踪、增强和信号预测等。

1 自适应滤波器的原理

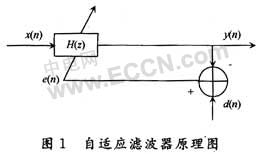

自适应滤波器的原理如图1所示。

图中x(n)称为输入信号,y(n)是输出信号,d(n)称为期望信号,或称参考信号、训练信号,e(π)是误差信号,e(n)=d(n)-y(n)。

自适应滤波器H(z)的系数根据误差信号,通过一定的自适应算法,不断地进行改变,使输出信号y(n)最接近期望信号d(n)。

本文以自适应处理器为例说明自适应滤波器的设计。

2 自适应滤波器的设计

2.1 TMS320C6701的主要特点

TMS320C6701是一种通用浮点超高速DSP,与TMS320C6201管脚兼容,主频167 MHz,共8个运算单元,其中6个为浮点单元,也采用8*32 b=256 b的超长指令字,分置运算能力为1 GFLOPS或1 336 MIPS,结构上与C6201类似,不同之处在于:

(1)4个浮点/定点ALU;

(2)2个定点ALU;

(3)2个浮点/定点乘法器,乘法器接受32 b定点数,产生64 b结果;

(4)支持32/64 b的IEEE浮点格式;

(5)峰值运算能力为:1 GFLOPS(32 b单精度),256 MFLOPS(64 b双精度),乘法并行操作688 MFLOPS。

2.2 自适应处理器的实现

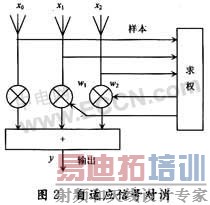

在自适应信号处理中,DSP要根据一定的算法,从实测数据中估算出权值,然后DSP把这种自适应权与数据合成,得到期望的输出。图2是一个自适应对消原理图,在3路数据中都含有期望的信号和要抑制的干扰,其中各路的干扰是相关的,而信号的相关性很弱,信号与干扰不相关。自适应算法就是从3路数据中取来一批数据作为样本,按最小二乘法则,将3路数据合成,使得合成输出中干扰基本上被消除,而信号仍较强。为了使信号不随干扰一起被对消掉,希望在求全样本中无信号。

可采用DSP对3路输入支路进行自适应合成,每路数据为复数据,I,Q串行,即先实部后虚部的次序,数据速率为1.5 MHz,根据复数的合成公式为:

y=x0-w1xl-w2x2

wn,xn,y均为复数。每输出一个复数数据,需要8次实数乘法和8次实数加法,要求DSP始终保持24 MFLOPS的运算速度。主频60 MHz的TMS320C6701峰值运算速度为60 MFLOPS,数据输入/输出速度也能满足要求。

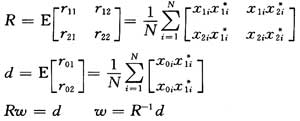

自适应权值的运算和系统的一些控制功能由另一片TMS320C6701完成,此C6701定期从3路信号中取得一批数据作为样本,样本中仅含干扰而没有信号成分,然后按照如下公式计算出自适应权w=[w1,w2]T:

其中E表示求数学期望,在此用N次平均值近似取代,N定为16,各元素均为复数。 [p]

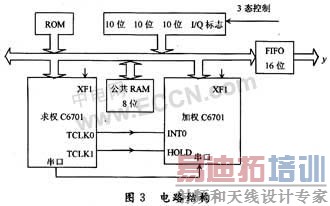

2.3 硬件结构与原理

本电路采用2片C6701,电路结构如图3所示,3路信号为10位定点数据格式,拼成30位并行数据送到C6701的总线上,C6701将其读到片内RAM,利用移位指令分解为3个定点数。求权C6701必须把数据转换成浮点数,才能以较高的精度快速求出自适应权。求权运算中要用到除法操作,浮点DSP进行除法运算很方便。求权C6701将求得的权转换为16位定点格式,写到两片C6701共用的RAM中,加权C6701按定点方式用自适应权对3路数据加权,对结果取16位,通过FIFO后送出。

系统时钟为3 MHz,此时钟将3路共30位数据以及I,Q标志位共6701位数据送向C6701,两片C6701利用互锁信号XF0、XF1确保正确地从总线上读取数据,既不丢失,也不重复读取,并根据数据的I,Q标志区分复数据的实部和虚部,两片C6701的操作如下:

(1)求权C6701用XF1和互锁指令定期读取一批数据作为样本,求得自适应权,并化为16位定点数。

(2)求权C6701利用配置成通用输出管脚的TCLK0、TCLK1向加权C6701先后提出INT0请求、HOLD请求。

(3)求权C6701取得两片C6701的公共总线控制权,利用地址线、数据线、读写R/W和STRB向公共RAM写入自适应权,然后撤销HOLD请求。

(4)加权C6701取得总线控制权,从公共RAM中读自适应权。

(5)加权C6701进行3路数据合成,把16位结果和I,Q标志写入FIFO;系统按数据时钟从FIFO中取走数据。加权C6701一直进行这样的合成、写FIFO操作,直到求权C6701下一次提出中断、HOLD请求。

(6)在两片C6701访问公共RAM,以及加权C6701向FIFO写数时,输入缓冲器74F245上的三态使能是关闭的。

2.4 时序要求

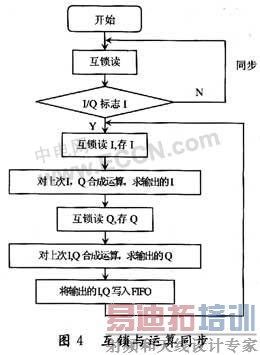

C6701利用互锁操作从数据线上正确读数是关键,数据时钟的占空比是50%,将它与C6701的XF1(设定为输入)相连,C6701通过互锁指令保证读数操作与数据时钟准确同步,同时加权C6701还要完成多次乘加运算和FIFO写数操作,这要求在硬件时序给定的情况下,C6701利用软件指令的优化排列来保证处理的正确性和高效性,其同步和运算、读写流程如图4所示,当C6701读数、写FIFO的时序与数据时钟不合拍时,可以执行指令执行顺序或增减空操作(NOP)指令。

3 软硬件调试

将PC机通过仿真卡、电缆与C6701电路板上的仿真口接好,给电路板加电,运行仿真软件,观察C6701的寄存器、程序、数据内容,因为有两片C6701,用两个仿真器调试更方便。软硬件调试的工作主要是C6701与其他设备的握手、通信问题。求权C6701的主要调试过程是:

(1)调试互锁读数指令,若有信号源,即前端送来3路数据和相应的时钟且3路信号值已知或已测出的话,则令C6701全速运行读取一段数据,然后让C6701停下来,观察读到的数据与送来的数据是否完全一致,若不一致,则逐步检查;若没有信号源,则利用示波器或逻辑分析仪来分析波形,C6701进行互锁读时,就会将XF0置低,观察XF0与XF1(数据时钟)以及STRB信号的波形,可以看出同步互锁的时序配合,若达不到要求,则要修改C6701程序,还应注意C6701读数时刻(STRB上升沿)是否临近数据转换沿。

(2)向RAM写自适应权:利用仿真器直接察看RAM中内容是否正确写入,或者将写入的权再从RAM读回后比较,以次验证存储器总线操作。

4 程序固化

软硬件调试符合要求后,就可以将程序固化到RAM中。求权C6701的程序代码固化在EPROM地址1000H开始的区间,加权C6701的程序代码固化在EPROM地址8000H开始的区间,求权C6701是标准的8位ROM引导方式,而加权C6701是串行口引导方式,其程序头与求权C6701代码的程序头一样,加权C6701的32位代码事先按先低字节,后高字节的顺序转换成8位代码。

求权C6701的代码在上电复位后自动装入片内RAM,求权C6701引导成功后要通过串口向加权C6701发送加权C6701的代码,求权C6701总共向加权C6701发送N+2个32字。

在程序固化后,再检验电路板的工作是否正确,可通过C6701的IACK等管脚连到的发光二极管闪烁来表明DSP程序已经正确引导并正常运行,在C6701的程序中应加入IACK指令,C6701全速工作时定期在IACK管脚上输出一个负脉冲。

5 结 语

DSP器件已经应用于很多领域,用其构成的自适应滤波器,也得到了广泛应用,本文提出的这种特殊结构的自适应滤波器,由于有较好的实时性和滤波效果,应该有较好的应用前景。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>