- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ADSP—TS2O2的高性能字脉冲压缩实现

O 引 言

脉冲压缩技术是指雷达发射出宽脉冲信号,在接收端,回波宽脉冲信号通过处理后得到窄脉冲的实现过程。它有效地解决了雷达的作用距离和距离分辨力之间的矛盾,可以在不损失雷达威力的前提下提高雷达的距离分辨力,是雷达系统中广泛采用的一种比较成熟的技术。随着数字技术和大规模集成电路技术的飞速发展,采用数字技术实现脉冲压缩越来越显示出优越性。数字脉压在实现滤波的同时,可以方便地实现旁瓣抑制加权处理,既可以有效地缩小脉压系统的设备量,又具有高稳定性和可维护性,进一步提高了系统的可编程性能,是现代脉压系统发展的趋势,特别是高性能DSP(数字信号处理器)的不断推出,为进一步提高数字脉压系统的性能和集成度提供了可能。脉冲压缩信号有多种形式,目前采用最多的是线性调频信号和相位编码信号,本文选用ADI公司的新一代高性能DSP芯片ADSP-TS202,实现线性调频信号的高速、高精度数字脉冲压缩。

1 脉冲压缩

脉冲压缩器的设计实际上就是匹配滤波器的设计。设发射信号为s(t),根据匹配滤波理论,匹配滤波器的冲击响应为h(t)=s*(t0—t),匹配滤波器输出为y(t)=s(t)*h(t)。数字信号处理时,脉压过程就是通过对回波序列s(n)与匹配滤波器的脉冲响应序列h(n)求线性卷积实现。则数字匹配滤波器的输出:

![]()

式(1)的方法叫做时域相关法。根据傅里叶变换理论,时域卷积等效于频域的乘积,故(1)式可以采用FFT(快速傅立叶变换)和IFFT(快速逆傅立叶变换)在频域实现,这种方法称为频域FFT法。用公式表示为: ![]()

根据匹配滤波理论,FFT[h(n)]=FFT[s*(-n)]=S*(k)。设接收的回波信号为x(t),用频域FFT法实现脉压的具体过程如下:先对接收信号A/D采样后得到x(n),再对信号x(n)进行FFT变换得到X(k),X(k)与发射信号s(t)的采样序列s(n)的FFT的复共轭S*(k)相乘,然后再对乘积作IFFT而获得时域脉压结果。由于S*(k)可以预先算出存入DSP的RAM空间里,每次运算时,只需读出RAM中的数值即可进行运算,在对脉压作加窗处理时,仅需事先将窗函数W(k)与S*(k)的乘积H(k)=S*(k)·W(k)存入RAM中即可,不会额外增加存储量及运算量。脉冲压缩的点数比较大时,频域FFT法的处理速度要比时域相关法快很多,下面讨论用频域FFT法实现高速数字脉冲压缩,文中的脉冲压缩就是基于图1的原理实现的。

2 数字脉压系统的实现

2.1 芯片介绍

ADI公司生产的ADSP-TS202是一款性能极高的静态超标量处理器,具有两个计算块,每计算块均有一个加法器、一个乘法器、一个移位单元,并具有专门的IALU进行地址产生和程序指针管理,每指令周期最多可并行执行四条指令。片上存储空间高达12Mbit,四条相互独立的128 bit宽度的内部数据总线。该处理器可以将多种不同宽度存储单元与双运算模块相结合处理,最高工作频率500MHz。利用其独特的单指令多数据流技术,可以提供40亿次40bitMAc运算或者10亿次80bitMAC运算。

ADSP-TS202内的IALU提供了位反序寻址和循环缓冲寻址等操作,乘法器提供了“定点复数共轭相乘”指令,即当操作数为两个复数a,b时,该指令产生a×b*的结果。利用该指令能使IFFT与FFT共用同一组旋转因子,这样既节省了内存开销,又避免了传统方法中取共轭、排序等耗时的操作;该乘法器还提供了“定点双寄存器乘法”指令,这些特点使得ADSP-TS202特别适用于基于FFT的数字信号处理。

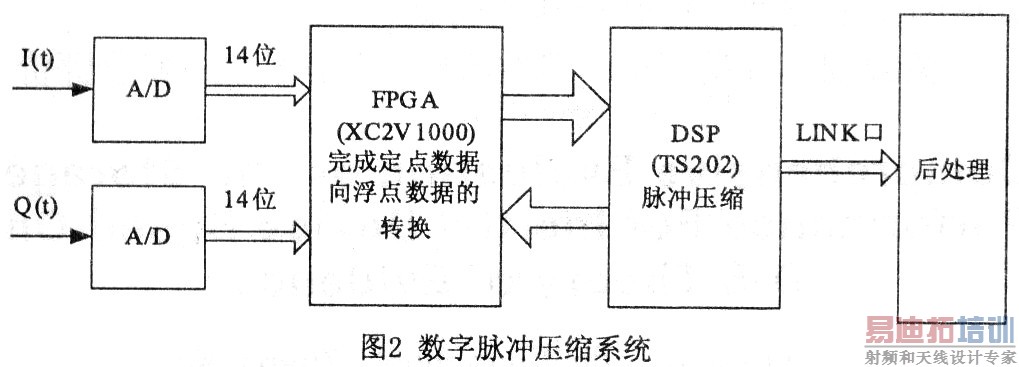

2.2 系统结构和硬件设计 [p]

图2是数字脉冲压缩系统的结构框图。零中频的正交解调信号F(t),Q(t)用A/D转换成数字信号,A/D转换时,必须对每个取样值进行截尾或舍入,会引入量化误差,当采样位数大于12bit时,量化误差对波形的影响可以忽略。为了保证采样精度,系统选择双端口、14位精度的A/D转换器芯片AD9604,该芯片有70dB的SNR,两个通道之间的干扰隔离95dB。为了保证计算精度,进行脉冲压缩时我们采用浮点数据格式进行计算,数据经A/D采样后用硬件实现定点浮点转换(软件实现耗时较长),存储在FPGA内的Block select RAM,I、Q两路对应点组成一个64bit的浮点复数数据,每64bit称为一个字(word),按照100Mword/S(DSP的系统时钊ffSCLK=lOOMHz)的速度通过DMA方式把数据从FPGA转入SSP内。把Block Select RAM配置为双口RAM,可实现数据采样结束即可完成转存。算法实现时,窗函数与旋转因子均可预先存储在DSP内的DRAM中,脉压完成后,通过TS202的LINK口把数据输出给下一级信号处理系统,LINK口的传输也采用DMA的方式进行,这样既不干扰DSP的内核运行,又容易控制。

2.3 软件设计

TS202的软件设计主要包括初始化程序,外部中断响应程序和DMA中断响应程序,其中DMA中断响应程序是核心。初始化程序完成TS202的初始化,包括总线设置,中断响应设置,LINK口传输模式设置,FLAG设置等。FPGA完成数据格式转换后产生一个外部中断给DSP,DSP DSP响应外部中断并调用外部中断响应程序,其功能是通过DMA通道把数据读入DSP的内存。数据读取完毕后,产生一个DMA中断,DSP响应该中断并调用DMA中断响应程序,其主要功能是进行FFT、IFFT等运算,完成脉冲压缩,并设置好LINK口DMA通道的控制寄存器,将脉压后的数据输出。图3是整个程序的流程图。

2.4 系统测试

雷达前端接收机接收一一个脉冲重复周期200us的线性调频脉冲串信号,每一个脉冲的采样点数为1080,补零到2048点,每一个采样点都配置成32bit的复数(实部、虚部各32bit)进行脉冲压缩处理。数据由FPGA向DSP内存转存数据的理论时间是20.48us,实际用时21.63us:ADSP-TS202完成2048点浮点复数FFT需要20667时钟周期,IFFT同样需要20667时钟周期,完成加窗的滤波器系数乘法需要5400个时钟周期,当DSP芯片工作在500MHz时,则完成脉压的总时长为:(20667*2+5400)/500=93.47us;脉冲压缩处理后的数据以4位方式由LINK口输出至下一级DSP进行后续处理,LINK口时钟设置为500MHz,在LINK口时钟的上升沿和下降沿对数据进行锁存和驱动(所谓双倍数据率),一次脉压结果的输出需要2048×64÷(500×2×4)=32.78us。为了节省时间,数据输出可以和数据输入重叠起来进行,相邻两次的数据脉压互不影响,这一次脉压结果的输出可以在下一次数据输入的同时进行,数据输入和输出均采用DMA方式进行,不影响DSP内核的运行。数据输入至DSP和脉压完成共需要2 O.4 8+(20667*2+5400)/500=114us<200us,满足实时性要求。 [p]

系统采用14bit的AD采样,32bit浮点数字处理,使得有限字长效应可以忽略不计,FFT程序计算结果可以达到的精度,IFFT程序可以达到的精度,脉冲压缩结果的精度可以达到。可以看到,本脉冲压缩系统实现了高速、高精度的脉冲压缩,无论在脉压结果还是在实时性上都能满足设计要求。

3 结束语

基于TS202的数字脉冲压缩系统,所需外围器件少,电路设计简单,在以其为核心的处理机硬件平台上通过程序设计,进行FFT/IFFT运算及加权处理,可实现高速雷达信号的频域脉冲压缩处理。此外,这种通用结构可使用于很多高速实时处理的应用场合,具有广泛的推广应用价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于ENC28J60的嵌入式以太网/CAN网关设计

下一篇:表面声波触摸屏